UNSVERSTIN DELEN CALMBRIA

Dipartimento di Elettronica, Informatica e Sistemistica

Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica Giclo XXIV

Tesi di Dottorato

Modulation techniques and synchronization methods for D6|A6 conversion systems

Andrea Ferrise

Coordinatore **Grof. Luigi Dalopoli**

Supervisore Brof. Alfredo Eisinberg

**DET**S

DEIS- DIPARTIMENTO DI ELETTRONICA, INFORMATICA E SISTEMISTICA Novembre

Settore Scientifico Disciplinare: ING-INF/04

To my parents.

To the people that have always played an important role in my life. "The end of wisdom is to dream high enough to lose the dream in the seeking of it" (William Faulkner)

# Contents

| 1        | Intr | oduct                                | ion                                                | 1              |  |  |  |

|----------|------|--------------------------------------|----------------------------------------------------|----------------|--|--|--|

| <b>2</b> | DC   | AC P                                 | ower Conversion                                    | 7              |  |  |  |

|          | 2.1  | Introd                               | luction                                            | $\overline{7}$ |  |  |  |

|          | 2.2  | VSI b                                | ridge topologies                                   | 10             |  |  |  |

|          |      | 2.2.1                                | Single-phase inverter                              | 10             |  |  |  |

|          |      | 2.2.2                                | Pulse width modulation technique                   | 15             |  |  |  |

|          |      | 2.2.3                                | Bipolar pulse width modulation                     | 16             |  |  |  |

|          |      | 2.2.4                                | Multi-polar pulse width modulation                 | 17             |  |  |  |

|          |      | 2.2.5                                | Spectral comparison between bipolar and multilevel |                |  |  |  |

|          |      |                                      | pwm waveforms                                      | 18             |  |  |  |

|          |      | 2.2.6                                | Three-phase inverter                               | 18             |  |  |  |

|          | 2.3  | Comm                                 | non inverter control techniques                    | 22             |  |  |  |

|          |      | 2.3.1                                | Variable voltage dc link                           | 23             |  |  |  |

|          |      | 2.3.2                                | Single-pulse width modulation                      | 23             |  |  |  |

|          |      | 2.3.3                                | Multi-pulse width modulation                       | 25             |  |  |  |

|          |      | 2.3.4                                | Multi-pulse, selected notching modulation          | 26             |  |  |  |

|          |      | 2.3.5                                | Sinusoidal pulse-width modulation                  | 29             |  |  |  |

|          |      | 2.3.6                                | Triplen injection modulation                       | 34             |  |  |  |

|          |      | 2.3.7                                | Voltage space vector PWM                           | 35             |  |  |  |

|          | 2.4  | CSI bi                               | ridge topologies                                   | 39             |  |  |  |

|          |      | 2.4.1                                | Single-phase inverter                              | 39             |  |  |  |

|          |      | 2.4.2                                | Three-phase current source inverter                | 40             |  |  |  |

|          | 2.5  | Reson                                | ant inverters                                      | 43             |  |  |  |

|          |      | 2.5.1                                | L-C resonant circuits                              | 44             |  |  |  |

|          |      | 2.5.2                                | Series resonant $L - C - R$ circuit                | 44             |  |  |  |

|          |      | 2.5.3                                | Parallel-resonant CSI inverters                    | 51             |  |  |  |

|          |      | 2.5.4                                | CSI series resonant inverter                       | 52             |  |  |  |

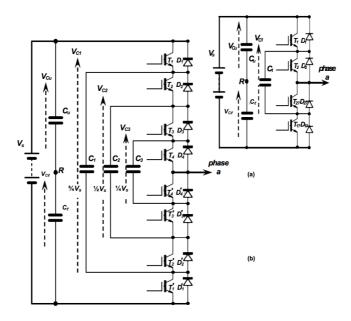

|          | 2.6  | Multi-level voltage-source inverters |                                                    |                |  |  |  |

|          |      | 2.6.1                                | Diode clamped multilevel inverter                  | 55             |  |  |  |

|          |      | 2.6.2                                | Flying capacitor multilevel inverter               | 55             |  |  |  |

### VIII Contents

|     |       | 2.6.3 Emerging Multilevel inverter topologies 57 |

|-----|-------|--------------------------------------------------|

|     |       | 2.6.4 Control and modulation strategies          |

|     | 2.7   | Reversible dc link converters                    |

|     |       | 2.7.1 Simultaneous control                       |

|     |       | 2.7.2 Inverter regeneration                      |

| 3   | A n   | new DC/AC conversion system                      |

|     | 3.1   | Introduction                                     |

|     | 3.2   | Switching loss mechanisms                        |

|     |       | 3.2.1 Diode reverse-recovery                     |

|     |       | 3.2.2 IGBT current tailing                       |

|     |       | 3.2.3 IGBT turn-on loss                          |

|     |       | 3.2.4 Device output capacitances                 |

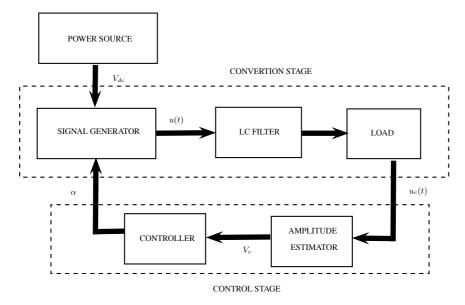

|     | 3.3   | Proposed conversion scheme                       |

|     |       | 3.3.1 The conversion stage                       |

|     |       | 3.3.2 The control stage                          |

|     |       |                                                  |

| 4   | -     | chronization techniques                          |

|     | 4.1   | Introduction                                     |

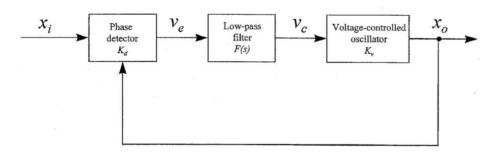

|     | 4.2   | Phase-Locked Loop                                |

|     |       | 4.2.1 Basic Concepts                             |

|     |       | 4.2.2 Standard PLL schemes                       |

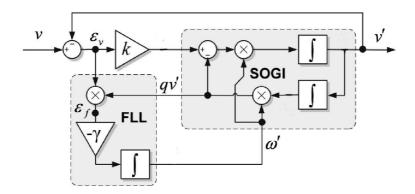

|     |       | 4.2.3 SOGI-PLL                                   |

|     | 4.3   | Adaptive notch filters                           |

|     |       | 4.3.1 ANFs for biased sinusoid input signal      |

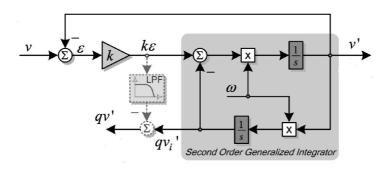

| 5   | soc   | GI methods for signal synchronization            |

|     | 5.1   | Introduction                                     |

|     | 5.2   | Adaptive-SOGI scheme                             |

|     | 5.3   | Biased sinusoid identification                   |

|     |       | 5.3.1 SOGI Structural properties                 |

|     |       | 5.3.2 Non-adaptive SOGI estimation scheme        |

|     |       | 5.3.3 Adaptive SOGI estimation scheme            |

|     | 5.4   | Numerical simulation                             |

|     |       | 5.4.1 Non-adaptive SOGI estimation scheme        |

|     |       | 5.4.2 Adaptive-SOGI estimation scheme            |

| 6   | Con   | nclusions                                        |

| Ref | feren | nces                                             |

|     |       |                                                  |

### Introduction

Current trends in energy supply and use are patently unsustainable regarding the whole set of current economical, environmental and social aspects in energy demand. Without decisive actions, as reported by the International Energy Agency (**IEA**) [70], energy-related emissions of  $CO_2$  will more than double by 2050 and increased oil demand will heighten concerns over the security of supplies. Energy efficiency, many types of renewable energy, carbon capture-storage (CCS) and nuclear power require widespread deployment to achieve the prefigured green-energy targets. The development of a correct energy policy is a nodal point if we want to make possible that the current investment decisions do not saddle us with sub-optimal technologies in the long term. There is a growing awareness of the urgent need of turn political statements and analytical work into concrete action. To spark this movement, at the request of the G8, the IEA is developing a series of road-maps for some of the most important technologies. As reported by the United States Department of Energy,

#### "Energy supply and demand plays an increasingly vital role in our national security and the economic output of our nation."

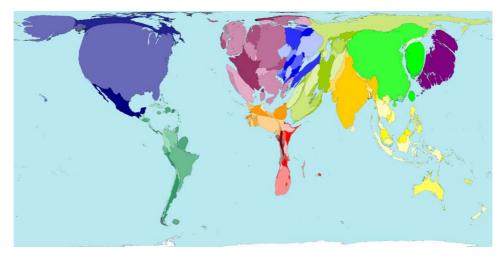

Annually 2584 kilowatt hours of electricity were produced for every person living on earth in 2002. Moreover, it is important to note that the distribution of production is not uniform - Benin and Togo only produce 10 and 11 kilowatt hours per person per year, respectively. Norway and Iceland produce almost 3000 times more per person per year. To better clarify the present situation, the web-site **Worldmapper** (website www.worldmapper.org) makes available very interesting maps where the territory size is proportional to the percentage of world electricity production that occurs there. In Fig. 1.1 is reported the World as far as energy demand and production is concerned.

The current world situation is increasing the need of the development of advanced clean energy technologies in order to address the global challenges of energy security, climate change and sustainable development. This challenge was acknowledged by the Ministers from G8 countries, China, India and South

Fig. 1.1. World Energy demand - WorldMapper

Korea, in their meeting in June 2008 in Aomori (Japan) where they declared the wish to have IEA prepare road-maps to advance innovative energy technology.

"We will establish an international initiative with the support of the IEA to develop road-maps for innovative technologies and co-operate upon existing and new partnerships, including CSS and advanced energy technologies. Reaffirming our Heiligendamm commitment to urgently develop, deploy and foster clean energy technologies, we recognise and encourage a wide range of policy instruments such as transparent regulatory frameworks, economic and fiscal incentives, and public/private partnerships to foster private sector investments in new technologies...."

The IEA has defined its global technology roadmap accordingly:

"... a dynamic set of technical, policy, legal, financial, market and organisational requirements identified by the stakeholders involved in it development. The effort shall lead to improved and enhanced sharing and collaboration of all related technology-specific RDD&D (Research, Development, Demonstration and Deployment) information among participants. The goal is to accelerate the overall RDD&D process in order to deliver an earlier uptake of the specific technology into the marketplace."

It is worth to underline that, at the current date, there exist major barriers, opportunities, and policy measures for policy makers and industry and financial partners to accelerate RDD&D efforts for specific clean technologies on both a national and international level. The guidelines for the research in this area suggest the need of improvements in terms of efficiency, robustness and cheapness of the modern power conversion systems. A first target of this thesis is the design of a more efficient conversion system that is highly competitive with respect to the standard technologies. Indeed, it is known

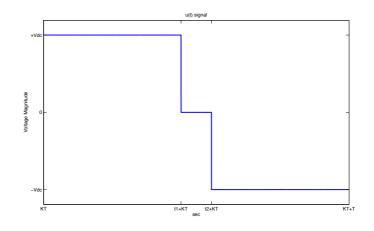

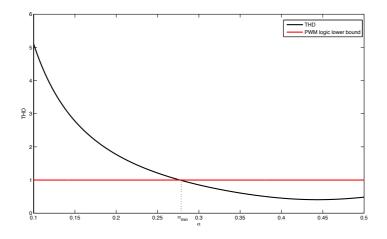

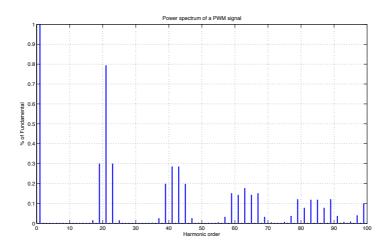

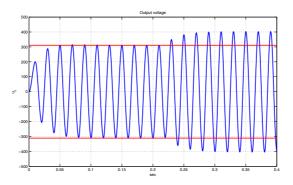

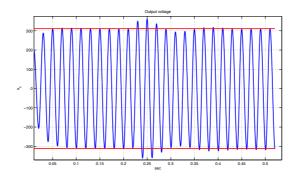

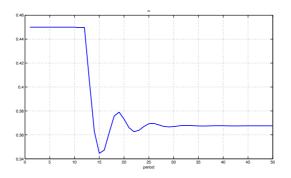

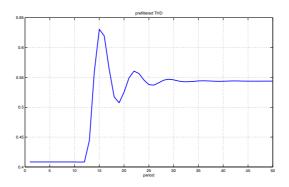

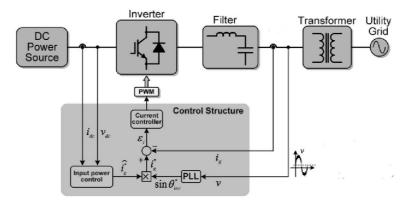

3

that, in conventional power conversion from a continuous power source to an alternate load, the input to inverters is a stiff dc voltage supply and the power switches operate in a switch mode. Therefore, the power devices are subjected to high switching stresses and switching power losses that increase linearly with the switching frequency of the implemented inversion technology. High switching power losses not only restrict switching frequency, but affects also the efficiency by dissipating a large amount of the produced energy inside the inverter. An increased volume and weight of the system are consequences of such losses too. In addition to these limitations, the system suffers from other shortcoming such as electromagnetic interferences and acoustic noise (see [67]). A different inverter output signal is proposed that consists in a T-periodic, three-level signal with a single centred adjustable zero-level. In Chapter 3, the properties of this particular signal are investigated. Interestingly, the particular structure of the proposed signal permits to obtain an analytical expression for the relative total harmonic distortion (THD) in terms of the zero-level duration. The obtained THD expression can be so tuned to assume values that are less than 1 unlike the standard pulse-width modulation (**PWM**) techniques presented in Chapter 2. An immediate result is that, by presenting only three-level, the inverter switches have to switch at a frequency equal to  $3f_{ref}$  if  $f_{ref}$  is the desired output frequency and so the corresponding switching stress, which the switches are subject to, is much smaller than standard devices that require very greater switching frequencies. An explicit tuning for a LC filter and a control algorithm are also presented in Chapter 3: the tuning permits to make the system insensitive with respect to filter variations and the control algorithm maintains the output sinusoidal amplitude at a desired level. The second problem, related to power conversion system and discussed in Chapter 4, is the synchronization of the generated signals. The synchronization between the grid voltage and the voltage or current synthesized by the converter is a central task: phase, amplitude and frequency of the utility voltage are critical information for the operation of the grid-connected inverter systems. In almost all power electronic equipment connected to the grid, a phase-locked loop (PLL) is used to obtain an accurate synchronisation to the grid. More in general, any implemented synchronisation algorithm must cope with the existing electrical environment (see [25]), e.g. with harmonics, voltage sags and commutation notches. Another aspect that must be taken into account is represented by grid frequency variations [80, 89]. In robust grids, the frequency variations are usually small, but larger frequency variations may occur in small interconnected grids. Furthermore, the synchronisation must handle measurement noise and, in general, an accurate zero voltage crossing detection is essential for the control of grid-commutated converters, otherwise the converter system can suffer from poor performance or even instability [32]. The zero voltage crossing therefore must be accurately detected each half period of the grid even if it is well known that zero-cross detectors performance is very low in the presence of electromagnetic disturbances occurring in electrical network in various conditions and affecting electrical

#### 4 1 Introduction

equipments designed to operate in non polluted environment [68, 90]. A more demanding application is the grid connection of a forced-commutated voltage source converter when vector current control is used. The synchronization must be update not just at zero voltage crossings but continuously under the whole period. In this case, a flux-based transformation angle detector is used to obtain the rotating dq-coordinate system [86]. Two classical solutions were proposed in the late 60's as synchronisator devices: Phase-Locked Oscillator (PLO) system and analogue PLL. The PLO system was proposed by J.D. Ainsworth to deal with the novel, at that time, harmonic instability problem in connected grids. The key idea was to place a Voltage Controlled Oscillator (VCO) inside the controller of the thyristor based rectifier of a HVDC by providing good noise rejection and frequency adaptation. The main drawback is the high complexity in the tuning of this kind of controller. The VCO scheme was therefore applied in analogue phase locked loops. The main novelty of the PLL proposal is the fact that the VCO is not a part of the main control algorithm but it is employed within a measurement circuit (estimation). The analogue PLLs provide robustness in the presence of grid frequency deviations and high frequency noise. However they perform bad in the presence of harmonics and unbalance [32]. Today, by using a software solution to the PLL, a flexible and cost effective solution is obtained: digital filters and controller have increased performances and made new methods feasible. Moreover, if the input signal is noisy, a predictive digital filter can be used to find the zero voltage crossing for the PLL. The calculation time is critical for a real time control system, which results in a demand for fast algorithms. The synchronization problem can be posed as a stochastic filter too, such as Kalman and Recursive Least Square algorithms where the best feature of stochastic filters is their potential very fast transient even under distorted conditions. In [83] a smart and simple stochastic filter approach is provided, based on a recursive least square algorithm, named Weighted Least Squares Estimation (WLSE), both for single-phase and three-phase systems. The main advantage of the WLSE is that its speed versus filtering is mainly set by the only forgetting factor.

Following the international standard criteria, any other synchronization algorithm should have:

- high stability margin;

- a fast transient response;

- zero steady-state average phase error and

- low phase jittering

in order to be considered a high performance system. Algorithms based on FIR and stochastic filtering provide a better filtering/transient trade-off than PLLs. However, this assertion should be reconsidered in the presence of grid-frequency deviations. Different standards such as EN 50160, IEC61000 and European Grid Codes consider frequency deviations higher than  $\pm 2Hz$  inside a normal operation range (isolated systems). Therefore, the performances of

advanced filtering techniques should be revised. Techniques that are proposed to improve the frequency adaptation can be classified as

- On-line update of filter implementation: using the frequency estimation the filter coefficients (generalized integrators, notch) are updated in real time.

- Hybrid systems: using a PLL to provide the frequency estimation, the performance of stochastic filters can be improved.

- Frequency loops: similar to the previous technique, by means of a frequency loop, the main algorithm is adapted to the input frequency.

- Variable sampling rate systems: in a general manner, an update of the discrete device switching frequency to be an integer multiple of the input frequency.

- Phase-offset correction techniques: the steady-state phase-error can be estimation from the outputs.

A qualitative comparative summarizes the performance of the difference techniques is reported in Fig. 1.2 (see [32]). The digital breakthrough resulted in a higher performance.

| Technique                         | Freq.  | Har/Unb               | Trans.                     | Amp.   | Comple- |

|-----------------------------------|--------|-----------------------|----------------------------|--------|---------|

|                                   | Adapt. | Filtering             | Response                   | InDep. | xity    |

| Zero-cross Det                    | —      | -                     | +                          | +      | +++     |

| PLO                               | +      | +                     | -                          | -      |         |

| Low-Gain PLL                      | +      | +                     | <u> </u>                   | -      | +       |

| High BW PLL                       | +      |                       | +++                        | -      | ++      |

| SRF-MAF                           | -      | ++                    | +                          | +      | +       |

| WLSE                              | -      | ++                    | ++                         | +      | -       |

| (Big <b>H</b> , small $\lambda$ ) |        |                       |                            |        |         |

| WLSE                              | _      | – –(small $\lambda$ ) | $++(\text{small }\lambda)$ | +      | +       |

| (Small <b>H</b> )                 |        | $+(big \lambda)$      | $-(big \lambda)$           |        |         |

Fig. 1.2. Comparative analysis

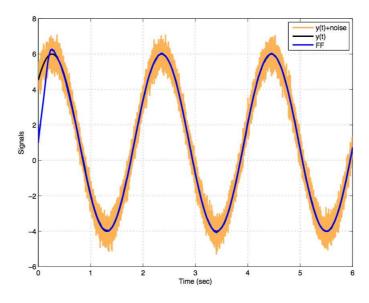

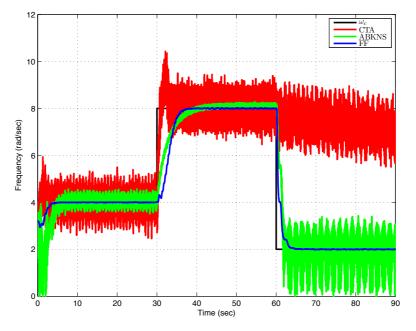

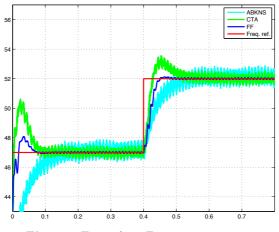

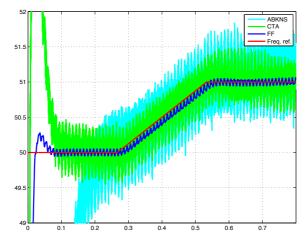

In this thesis a frequency-locked system is presented that is based on a second-order generalized integrator (**SOGI**). SOGI have been widely investigated in the literature. Adaptive and non-adaptive schemes are reported in Chapter 5 to track an input sinusoidal signal in a satisfactory manner. It has to be remarked that SOGI schemes can be easily adapted to a large variety of practical scenarios. Thanks to its flexibility, SOGI approach permits to deal with such a problem showing performances better than PLL and adaptive filters ones. The behaviour of the SOGI as second-order filter leads to fast transient response and a very good noise rejection as shown in numerical simulation. In Chapter 5 numerical simulations are shown to confirm the obtained results.

#### 2.1 Introduction

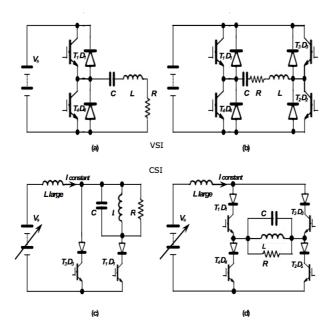

DC-AC power conversion problem consists in the manipulation of a dc power source in order to obtain an alternative power signal at a desired output voltage or current amplitude and frequency through a static semiconductor device that is defined inverter (see [3, 26]). From 1980s, semiconductor manufacture development brought power devices, such as gate turn-off thryristor, Triac, bipolar transistor, insulated gate bipolar transistor and metal-oxide semiconductor field effected transistor (GTO, Triac, BT, IGBT, MOSFET, respectively) and so on, in higher switching frequency. In those equipments, devices as thyristors, GTOs and Triacs could be in low-frequency switching operation. High-frequency/high-power devices such as power BTs and IGBTs were also produced. Nowadays, most DC/AC inverters are DC/AC PWM inverters in different typologies. They are generally used in following applications:

- variable voltage/frequency AC supplies in adjustable speed drives (ASDs), such as induction motor drives, synchronous machine drives and so on;

- constant regulated voltage AC power supplies, such as uninterruptible power supplies (UPSs);

- static var compensations;

- flexible AC transmission systems (FACTSs);

- voltage compensations.

Adjustable speed induction motor drive systems are widely applied in industrial applications. These systems request the DC-AC power supply with variable frequency usually from 0 to 400 Hz, in fractional horsepower (HP) to hundreds of HP. The power devices used for ASD were thyristors, Triacs and GTOS in the 1970s and early 1980s. Power IGBT greatly changed the manufacturing of DC/AC inverters. Nowadays, two main families of power inverter can be identified: voltage- and current-fed respectively. The terms voltage-fed and current-fed are used in connection with the output from inverter circuits, that can be single-phase, three-phase or multi-phase. A voltage-source inverter

(VSI) is one in which the dc input voltage is essentially constant and independent of the load current drawn. The inverter specifies the load voltage while the drawn current shape is dictated by the load. A current-source inverter (CSI) is one in which the load current is predetermined and the load impedance determines the output voltage. The supply current cannot change quickly but it is controlled by series dc supply inductance which prevents sudden changes. The load current magnitude is controlled by varying the input dc voltage to the large inductance, hence inverter response to load changes is slow. Voltage control may be required to maintain a fixed output voltage when the dc input voltage regulation is poor or to control power to a load. Due to the particular generation process, harmonics which may lead to reduced load efficiency and they may affect the inverter output signals. Load harmonic reduction can be achieved by either filtering, selected harmonics reduction, chopping or pulse-width modulation as will be investigated below and a large range of quality indexes exist to evaluate the output signal in terms of their harmonic content. Since middle 1990s, the power quality problem has assumed a growing interest (as widely remarked in [77, 34, 91]). There are different reasons for this enormous increase in the interest in power quality:

- Electronic systems are more sensitive of voltage quality disturbances. These aspects are translated into a much higher costs than before associated with even a very short-duration disturbance.

- Equipment produces more current disturbances than it used to do. Both low- and high-power equipment is more powered by simple power electronic converters which produce a broad spectrum of distortion.

- The liberalization of the electricity industry has let to an increased need for quality indicators.

- Embedded generation and renewable sources of energy create new power quality problems, such as voltage variations, flicker, and waveform distortion. Most interfaces with renewable sources of energy are sensitive to voltage disturbances, especially voltage dips.

- Energy-efficient equipment is an important source of power quality disturbances. Adjustable-speed drives and energy-saving lamps are both important sources of waveform distortion and are also sensitive to certain types of power quality disturbances.

Generally, a difference between voltage and current distortion must be made. Voltage quality is related in fact to the effects of the network with respect to customer or load; current quality takes into account how the customer or the load affects the network. In the waveform distortion framework, it can be noted that distorted voltages affect the customer equipment while distorted currents affect the network components. In the case of voltage distortion the following problems are reported to arise

- inadvertent trip of circuit breaker or fuse;

- transformer overheating;

- capacitor problems;

- malfunctioning of electronic equipment;

- overheating of neutral conductors.

It has been referred with the term *waveform distortion* to all the deviations of the voltage and current signals with respect to the ideal sine wave. With respect to this definition, a number of different forms of waveform distortion can be distinguished: harmonic, interharmonic, and nonperiodic distortion. Harmonic distortion dominates in most the cases. When a signal is T-periodic, an analysis in terms of its Fourier series can be conducted. For a voltage waveform, it can be written

$$v(t) = V_0 + \sum_{j=1}^{H} V_j \sin(j\omega t)$$

(2.1)

where H is infinite in the case of continuous signal while it is determined by the sample frequency in the case of discrete signals. The same remains true for the current waveform. Within harmonic distortion, a further distinction can be made into dc components, even-harmonic distortion, and odd-harmonic distortion, that is the dominating case in the generality of applications. DC components need of different measurement or estimation techniques. It is important to remark that often the voltage or current waveform contains components that are not a multiple integer of the power system frequency and the presence of inter-harmonics can be interpreted in the time domain as the signal being periodic but with a period of more than one cycle. A further distinction is so provided between rational and irrational inter-harmonics. The former lead to periodic signals whereas the latter signals are aperiodic. Finally, some signals contain no periodicity at all. Examples are the voltage during ferro-resonance and the current taken by an arc furnace. In such scenarios, noise or chaotic behaviour can occur. In terms of the spectrum of the signal, harmonic distortion corresponds to frequency components at integer multiples of the power system frequency, inter-harmonic distortion to non-integer multiples, and noise to a continuous spectrum in between the harmonic and inter-harmonic spectral lines. Two particular indices assume a key role in the treatment of power quality for conversion systems: the total harmonic distortion and the **crest** factor. Eq. (2.1) shows as a periodic signal can be decomposed into a number of harmonics and so the signal can be totally characterized by the magnitude and phase of these harmonics. In power system applications, the fundamental component will normally dominate. The total harmonic distortion indicates the deviation of voltages or currents from ideal and desired sine waves and it is expressed as

$$THD = \frac{\sqrt{\sum_{j=2}^{H} V_j^2}}{V_1}.$$

(2.2)

The crest factor is a time-domain property indicating the distortion of the actual amplitude. It is defined as the ratio between the amplitude of a signal

and its rms value:

$$C_r = \frac{V_{max}}{V_{rms}} \tag{2.3}$$

with

$$V_{rms} = \sqrt{\frac{1}{T} \int_0^T v^2(t) d(t)}.$$

(2.4)

For a perfect sine wave the crest factor is equal to  $\sqrt{2}$  so that is makes sense to introduce a *relative crest factor* which is unity for a perfect sine wave:

$$c_r = \frac{1}{\sqrt{2}} \frac{V_{max}}{V_{rms}}.$$

(2.5)

This index takes into account how much a signal deviates from a dc signal, whereas the relative crest factor indicates how much a signal deviates from a sine wave. In the following sections the generality of the inverter topologies will be investigated and in particular their frequency behaviour will be highlighted. The main standard results regarding the state of art of the power switching conversion systems are below reported. For an exhaustive overview, the considered bibliography (see for example [41, 92, 60, 63, 72, 73, 7, 65]) is highly recommended.

#### 2.2 VSI bridge topologies

#### 2.2.1 Single-phase inverter

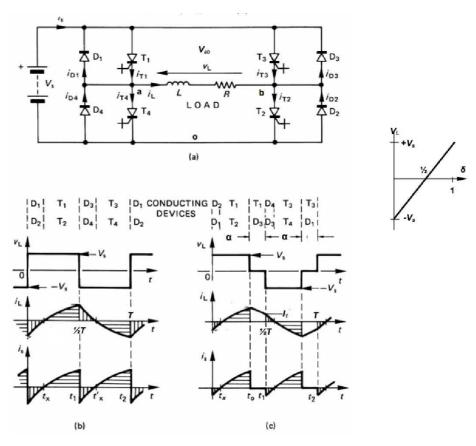

The structure of an H-bridge voltage-source inverter (VSI) is reported in Fig. 2.1 that makes use of switches which may be transistors (MOSFET or IGBT), or thyristors (GTO or GCT) at high power. Device conduction patterns are also shown in the same figure. With inductive loads (not purely resistive), stored energy at turn-off is fed through the bridge reactive feedback or free-wheel diodes  $D_1$  to  $D_4$ .

In Fig. 2.1, the generated waveforms for a square-wave output  $(2t_1 = t_2)$  are shown. It is an immediate result that the load current  $i_L$  grows exponentially through  $T_1$  and  $T_2$  according to the differential law

$$V_s = L \frac{d}{dt} i_L + i_L R. aga{2.6}$$

Such equation is obtained by turning off  $T_1$  and  $T_2$ , turning on  $T_3$  and  $T_4$ , and thereby reversing the load voltage polarity. Instantaneous changes of polarity for the load current are not permitted by the inductive topology of the load and load reactive energy flows back into the supply via diodes  $D_3$  and  $D_4$ (which are in parallel with  $T_3$  and  $T_4$  respectively) according to

$$-V_s = L\frac{d}{dt}i_L + i_L R.$$

(2.7)

**Fig. 2.1.** GCT thyristor single-phase inverter: (a) circuit (b) square-wave output (c) quasi-square-wave output

The load current goes exponentially fast to zero. As it can be noticed, the output voltage is a square wave of magnitude  $\pm V_s$ . For a resistive-inductive load, characterized by resistor R and inductor L, with time constant  $\tau = \frac{L}{R}$ , during the first cycle, the load current is (with no initial load current)

$$i_L(t) = \frac{V_s}{R} \left( 1 - e^{-\frac{t}{\tau}} \right).$$

(2.8)

where Eq. (2.6) is taken into account. Under steady-state conditions, Eq. (2.6) yields

$$i_L(t) = \frac{V_s}{R} - \left(\frac{V_s}{R} - I_0\right)e^{-\frac{t}{\tau}} \quad 0 \le t \le \frac{T}{2}.$$

(2.9)

where  $I_0$  stands for the initial current. During the second half-cycle  $(t_1 \le t \le t_2)$  when the supply is effectively reversed across the load, Eq. (2.7) yields

$$i_L(t) = -\frac{V_s}{R} + \left(\frac{V_s}{R} - I_0\right)e^{-\frac{t}{\tau}} \quad 0 \le t \le \frac{T}{2}.$$

(2.10)

In steady-state conditions, Eq. (2.9) permits to obtain the initial current  $I_0$  by imposing that at  $t = t_1$ ,  $i_L = I_0$ . The zero current cross-over point  $t_x$  can be found by solving Eq (2.9) for  $t = t_x$  when  $i_L = 0$  which yields

$$t_x = \tau \log\left(1 + I_0 \frac{R}{V_s}\right). \tag{2.11}$$

There are other signals of interest in the analysed circuit and, in particular, an estimate of thyristor, average diode and mean source currents, namely  $\overline{I}_t$ ,  $\overline{I}_d$  and  $\overline{I}_s$  respectively, are often needed. Such currents can be obtained via integration of the load current over the appropriated bounds. In particular

$$\overline{I}_{t} = \frac{1}{t_{2}} \left[ \frac{V_{s}}{R} (t_{1} - t_{0}) + \tau \left( \frac{V_{s}}{R} + I_{0} \right) \left( e^{-\frac{t_{1}}{\tau}} - e^{-\frac{t_{0}}{\tau}} \right) \right], \qquad (2.12)$$

and

$$\overline{I}_D = \frac{1}{t_2} \left[ -\frac{V_s}{R} t_x - \tau \left( \frac{V_s}{R} + I_0 \right) \left( e^{-\frac{t_x}{\tau}} - 1 \right) \right].$$

(2.13)

The average DC voltage source current is related to the average semiconductor device currents by

$$\overline{I}_s = \frac{1}{t_2} \left[ -\frac{V_s}{R} t_1 + \tau \left( \frac{V_s}{R} + I_0 \right) \left( e^{-\frac{t_1}{\tau}} - 1 \right) \right].$$

(2.14)

In steady-state conditions, the averaged power delivered by the DC supply and absorbed by the resistive load component R is equal to

$$P_L = V_s \overline{I}_s. \tag{2.15}$$

Fourier series expression of the instantaneous output voltage is the following

$$V_L = \frac{4}{\pi} V_s \sum_{n \text{ odd}}^{\infty} \frac{1}{n} \sin n\omega_0 t$$

(2.16)

where  $\omega_0 = 2\pi f_0$  is the fundamental frequency and for n = 1 the magnitude of the fundamental frequency is  $\frac{4}{\pi}V_s$ . Even load current can be expressed in terms of the Fourier voltage waveform series, leading to

$$i_L(\omega t) = \sum_{n=1,3,5}^{\infty} I_n \sin(n\omega_0 t - \phi_n),$$

(2.17)

where  $I_n = \frac{4}{n} \frac{V_s}{nZ_n}$  whence  $I_{n,rms} = \frac{I_n}{\sqrt{2}}$ ,

2.2 VSI bridge topologies 13

$$Z_n = \sqrt{R^2 + (n\omega_0 L)^2}$$

(2.18)

and

$$\phi_n = \tan^{-1} \frac{n\omega_0 L}{R} \tag{2.19}$$

such that  $\cos \phi_1 = \frac{R}{Z_1}$ . The fundamental output power is

$$P_1 = \frac{V_s^2}{R} \frac{8}{\pi^2} \cos^2 \phi_1.$$

(2.20)

The load power is given by the sum of each harmonic power component, that is

$$P_L = \sum_{n=1,3,5}^{\infty} I_{n,rms}^2 R.$$

(2.21)

Alternately, after integrating Eq. (2.15), with the load current from Eq. (2.17), one can obtain

$$P_L = \frac{V_s^2}{R} \left( 1 - \frac{2\tau}{t_1} \frac{1 - e^{-\frac{t_1}{\tau}}}{1 + e^{-\frac{t_1}{\tau}}} \right).$$

(2.22)

The rms output voltage from a H-bridge can be varied by producing a quasisquare output voltage  $(2t_1 = t_2, t_0 < t_1)$  as shown in Fig. 2.1(c). Moreover, according to Fig. 2.1(c), the load current  $i_L$  for an applied quasi square-wave voltage is derived in the following manner. For  $v_L > 0$ , it can be derived that

$$i'_L(t) = \frac{V_s}{R} - \left(\frac{V_s}{R} - \tilde{I}\right)e^{-\frac{t}{\tau}} \quad 0 \le t \le t_0.$$

$$(2.23)$$

where

$$\tilde{I} = -\frac{V_s}{R} \frac{e^{-\frac{t_1-t_0}{\tau}} - e^{-\frac{t_1}{\tau}}}{1 + e^{-\frac{t_1}{\tau}}}.$$

(2.24)

For  $v_L = 0$ , the following expression is obtained

$$i_L''(t) = \hat{I}e^{-\frac{t}{\tau}} \quad 0 \le t \le t_1 - t_0,$$

(2.25)

with

$$\hat{I} = -\frac{V_s}{R} \frac{1 - e^{\frac{t_0}{\tau}}}{1 + e^{-\frac{t_1}{\tau}}}.$$

(2.26)

Lastly, for  $v_L < 0$

$$i_L(t) = -\frac{V_s}{R} + \left(\frac{V_s}{R} + I_1\right)e^{-\frac{t}{\tau}} \quad 0 \le t \le t_0$$

(2.27)

and  $I_1 = -\tilde{I}$ . The zero current cross-over instant represents the solution of Eq. (2.23) for t when  $i_L$  is equal to zero, i.e.,

$$t_x = \tau \log\left(1 - \frac{\tilde{I}R}{V_s}\right). \tag{2.28}$$

The average thyristor current, namely  $\overline{I}_t$ , average diode current,  $\overline{I}_d$ , and mean source current,  $\overline{I}_s$ , can be found by integration of the load current over the appropriated bounds (assuming alternating zero volt loops)

$$\overline{I}_t = \frac{1}{t_1} \int_{t_x}^{t_1} i'_L dt + \frac{1}{2t_2} \int_0^{t_1 - t_o} i''_L(t) dt, \qquad (2.29)$$

where the currents are the same in Eqs. (2.23)-(2.27), and

$$\overline{I}_d = -\frac{1}{t_2} \int_0^{t_X} i'_L dt + \frac{1}{2t_2} \int_0^{t_1 - t_o} i''_L(t) dt.$$

(2.30)

The average source current is related to the average semiconductor device currents by

$$\overline{I}_s = 2\left(\overline{I}_T - \overline{I}_D\right). \tag{2.31}$$

The Fourier series of the output voltage  $V_L$  is the following

$$V_L = \frac{4}{n} V_s \sum_{n \text{ odd}}^{\infty} \frac{\cos\frac{1}{2}n\alpha}{n} \sin n\omega_0 t, \qquad (2.32)$$

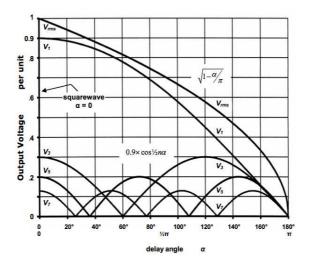

and for n = 1, the rms fundamental of the output voltage  $v_{o1}$  is given by  $0.90 \times V_s \times \cos \frac{1}{2}\alpha$ . The characteristics of these load voltage harmonics are shown in Fig. 2.2.

The current load can be expressed in Fourier series as

$$i_L(\omega t) = \sum_{n=1,3,5,...}^{\infty} I_n \sin(n\omega_0 t - \phi_n)$$

(2.33)

where  $I_n = \frac{4}{n} \frac{V_s}{nZ_n} \cos \frac{1}{2} n \alpha$  whence

$$I_{n,rms} = \frac{1}{\sqrt{2}} I_n \qquad Z_n = \sqrt{R^2 + (n\omega_0 L)^2} \qquad \phi_n = \tan^{-1} \frac{n\omega_0 L}{R}.$$

(2.34)

The load power is given by the sum of each harmonic power component. A variation of the basic four-switch dc to ac single-phase H-bridge is the half-bridge version where two series switches (one pole or leg) and diodes are replaced by a split two-capacitor voltage source. This reduces the number of semiconductors and gate circuit requirements, but at the expense of halving the maximum output voltage.

Fig. 2.2. Full bridge inverter output voltage harmonics normalised with respect to square rms output voltage  $V_{rms} = V_s$ .

**Fig. 2.3.** GCT thyristor single-phase half-bridge inverter: (a) circuit diagram; (b) square-wave output voltage

#### 2.2.2 Pulse width modulation technique

The standard pulse-width modulation techniques, (references [41, 49, 82, 42, 5, 53] and the bibliography therein) that are normally implemented to obtain desired output voltage amplitude and frequency, can de divided into

- bipolar pulse width modulation, and

- multi-polar pulse width modulation.

The main voltage output difference between the two methods is the harmonic content near the carrier frequency and its harmonics. Three-phase

PWM is a naturally extension to the single-phase case, except for the fact that single-phase PWM offers more degrees of flexibility than its application to three phase inverters, although three-phase PWM does have the attribute of triplen harmonic cancellation, due to the use of one (co-phasal) triangular carrier.

#### 2.2.3 Bipolar pulse width modulation

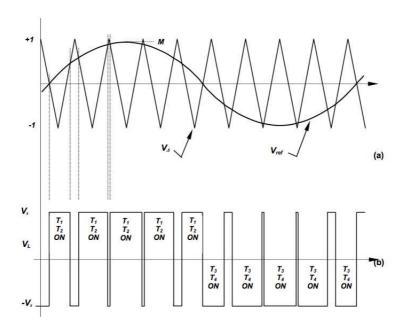

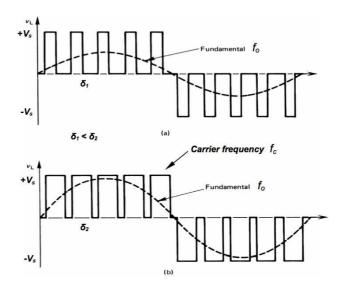

Bipolar modulation is the simplest PWM method that requires a comparison between a fixed-frequency, magnitude triangular carrier and the desired AC waveform, called the modulation waveform. The modulation is usually a sinusoid of magnitude (modulation index) M such that  $0 \leq M \leq 1$ . The waveforms in Fig. 2.4 underline how the load voltage  $V_L$  takes values between the two voltage levels,  $+V_s$  and  $-V_s$  (hence the term bipolar output voltage), according to

- $T_1$  and  $T_2$  are on when  $v_{ref} > v_d$  ( $T_3$  and  $T_4$  are off) such that  $V_L = +V_s$ .  $T_3$  and  $T_4$  are on when  $v_{ref} < v_d$  ( $T_1$  and  $T_2$  are off) such that  $V_L = -V_s$

- •

Fig. 2.4. Bipolar pulse width modulation: (a) carrier and modulation waveforms and (b) resultant load pwm waveform

#### 2.2.4 Multi-polar pulse width modulation

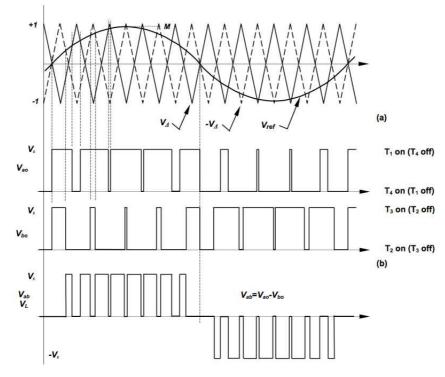

There exists two multi-polar output voltage techniques with single-phase voltage-fed bridges. In both cases, two triangular carries displaced by  $\pi$  radiant provide the same output for the same switching frequency. The waveform in Fig. 2.5 shows that the load voltage  $V_L$  takes values between the two voltage levels ( $+V_s$  and  $-V_s$  respectively) with inter-spaced zero periods, hence the term multilevel, specifically three-level in this case,  $0, +V_s$  and  $-V_s$ , according to

- $T_1$  is on when  $v_{ref} > v_d$  such that  $V_{a0} = +V_s$ ;

- $T_4$  is on when  $v_{ref} < v_d$  such that  $V_{a0} = 0$ ;

- $T_3$  is on when  $v_{ref} < -v_d$  such that  $V_{b0} = V_s$ ;

- $T_2$  is on when  $v_{ref} > -v_d$  such that  $V_{b0} = 0$ .

**Fig. 2.5.** Multilevel (3 level) pulse width modulation: (a) carrier and modulation waveforms and (b) resultant load pwm waveform

The multilevel load output voltage is the difference between the two leg voltage defines as:

•  $T_1$  and  $T_2$  are on such that  $V_{ao} = +V_s$ ,  $V_{bo} = 0$ ,  $V_{ab} = +V_s$ ;

- 18 2 DC-AC Power Conversion

- $T_2$  and  $T_3$  are on such that  $V_{ao} = 0$ ,  $V_{bo} = +V_s$ ,  $V_{ab} = -V_s$ ;

- $T_1$  and  $T_3$  are on such that  $V_{ao} = +V_s$ ,  $V_{bo} = +V_s$ ,  $V_{ab} = 0$ ;

- $T_2$  and  $T_4$  are on such that  $V_{ao} = 0$ ,  $V_{bo} = 0$ ,  $V_{ab} = 0$ .

The two zero output states are interleaved to balance switching losses between all four bridge switches. Device switching is at the carrier frequency, but the bridge load voltage (hence load current) experiences twice the leg switching frequency since the two carriers are displaced by  $\pi$  radiants. In Fig. 2.5 is reported another typology of unipolar approach, where the triangular carriers are not only displaced by  $\pi$  radiants, but are also vertically displaced. The upper triangle modulates reference values greater than zero, while the lower triangle modulates when the reference is less than zero.

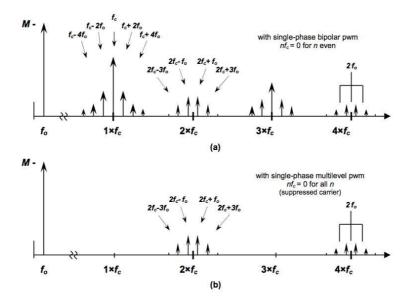

# 2.2.5 Spectral comparison between bipolar and multilevel pwm waveforms

The main characteristics of the H-bridges inverter output voltage with bipolar pwm are:

- a triangular carrier has only odd Fourier components, so the output spectrum only has carrier components at odd harmonics of the carrier frequency;

- the first carrier components occur at the carrier frequency  $f_c$ ;

- side-band components occur spaced by  $2f_0$ , where  $f_0$  is the fundamental frequency, from other components, around all multiples of the carrier frequency  $f_c$ .

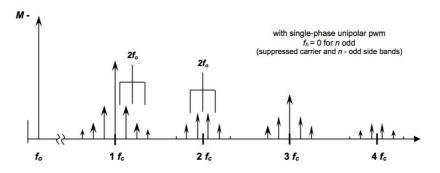

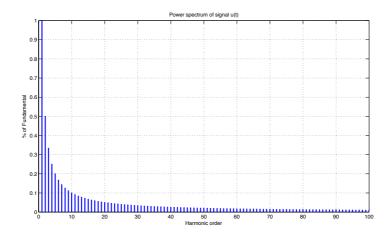

The principal properties of the H-bridges inverter output voltage with multilevel pwm are (as reported in Figure 2.6):

- the output switching frequency is double  $2f_c$  each leg switching frequency  $f_c$  since the switching of each leg is time-shifted (by  $\pi$  radiants) hence the first carrier related components in the output occur at  $2f_c$  and then at multiples of  $2f_c$ ;

- no triangular carrier Fourier components exist in the output voltage since the two carriers are in anti-phase ( $\pi$  apart) effectively cancelling one another in spectrum terms;

- side-band components occur spaced by  $2f_0$  from other components around each multiple of the carrier frequency  $2f_c$ .

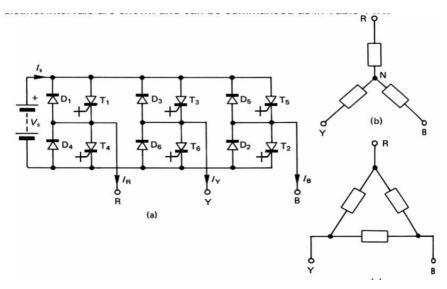

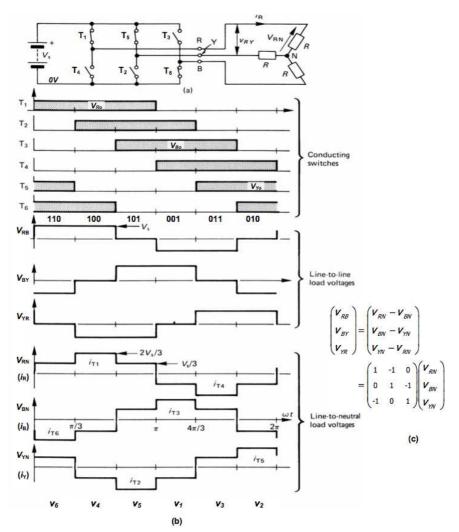

#### 2.2.6 Three-phase inverter

The classical scheme of a three-phase voltage-source inverter (VSI) bridge is reported in Fig 2.8. As it can be easily noted, the scheme involves six power switches together with six reactive energy feedback diodes. The three inverter legs are active at a time displacement, or phase, equal to  $\frac{2}{3}\pi$ .

Fig. 2.6. Typical phase output frequency spectrum, at a give switch commutation frequency, for: (a) bipolar pmw and (b) multilevel pwm

Each switch conducts for  $\pi$  radiants, in order to avoid that two series connected (leg or arm) semiconductor switches across the voltage rail conduct simultaneously. There are six different patterns for one output cycle and the rate of sequencing these patterns,  $6f_0$ , specifies the bridge output frequency  $f_o$ .

The three output voltage waveforms can be derived by analysing a balanced resistive star load and considering each of the six connection patterns (see Fig. 2.12 for better explanation).

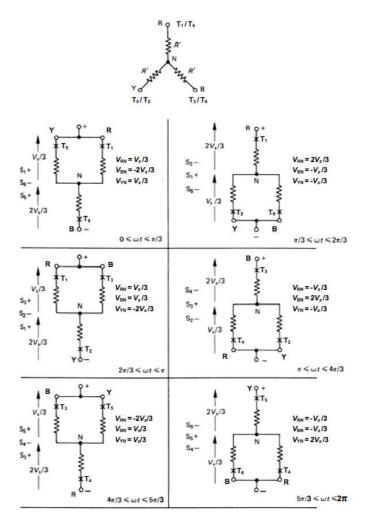

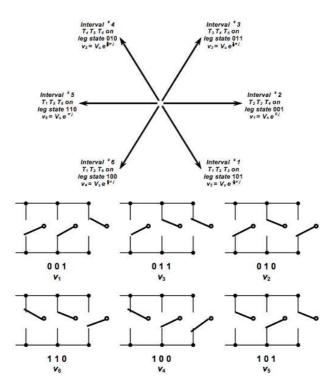

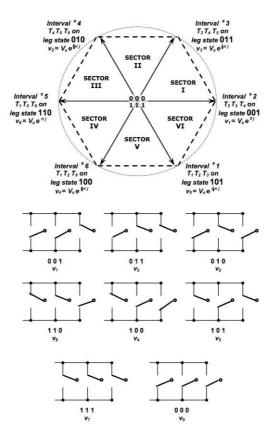

Rotating voltage space vector technique [13, 52, 10] can be adopted to analyse the three-phase output voltages. This technique is based on encoding the three voltage states of the output voltages from each of the three inverter legs (or poles), where a bit equal to the unity means the upper switch in the leg is on, while a bit equals to zero means the lower switch is on in that leg. The resultant binary number (one bit fro each of the three inverter legs) represents the output voltage vector number.

The rotational stepping sequence has been created in order to change only one leg state per time when rotating, that is only one device turns off and then the complementary switch of that leg turns on, at each step. Such aspect permits to obtain minimum inverter switching losses. The dwell time of the created rotating vector at each of the six vector positions is  $\frac{T}{6}$  of the cycle period T. Note that the line-to-line zero voltage states 000 and 111 are not used due to the fact that these configurations represent when either all the upper

Fig. 2.7. Derivation of trigger signals for multi-level naturally sampled pulse-width modulation waveforms: (a) for high fundamental output voltage and (b) for a lower output voltage, with conduction devices shown.

switches  $(T_1, T_3, T_5)$  are on or all the lower switches  $(T_2, T_4, T_6)$  are switched on. Phase reversal can be obtained by interchanging two phase outputs or, as it is the preferred method, the direction of the rotating vector sequence is reversed. Reversing is therefore effectively achieved by back-tracking along each output waveform. It is straightforward to obtain that the line-to-load neutral voltage, in its Fourier series representation, is given by

$$V_{n_{L-N}} = \frac{2}{\pi} V_s \sum_{n=1,6r\pm 1}^{\infty} \frac{\sin n\omega t}{n} \quad r = 1, 2, 3, \dots$$

(2.35)

that is

$$v_{RN} = \frac{2}{\pi} V_s \left[ \sin \omega t + \frac{1}{5} \sin 5\omega t + \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \dots \right].$$

(2.36)

The same structure is still valid for voltages  $v_{YN}$  and  $v_{BN}$  by substituting the  $\omega t$  with the corresponding  $\omega t + \frac{2}{3}\pi$  and  $\omega t - \frac{2}{3}\pi$  respectively. The line-to-line voltage is so expressed as

**Fig. 2.8.** Three-phase VSI inverter circuit: (a) GCT thyristor bridge inverter; (b) start-type and delta-type load

$$V_{n_{L-L}} = \frac{2\sqrt{3}}{\pi} V_s \sum_{n=1,6r\pm 1}^{\infty} sign(\cos\frac{n\pi}{6}) \frac{\sin n\omega t}{n} \quad r = 1, 2, 3, \dots,$$

(2.37)

that is

$$v_{RB} = \frac{2\sqrt{3}}{\pi} V_s \left[ \sin \omega t - \frac{1}{5} \sin 5\omega t - \frac{1}{7} \sin 7\omega t + \frac{1}{11} \sin 11\omega t + \dots \right], \quad (2.38)$$

and similarly for  $v_{BY}$  and  $v_{YR}$ . In Fig. 2.9(b) it is evident as  $v_{RB}$  is shifted by  $\frac{1}{6}\pi$  with respect to  $v_{RN}$  hence to obtain the three line voltages, while maintaining a  $v_{RN}$  reference,  $\omega t$  should be substituted with  $\omega t + \frac{1}{6}\pi$ ,  $\omega t - \frac{1}{2}\pi$ and  $\omega t - \frac{5}{6}\pi$ , respectively. Since the inter-phase voltages consist of two square waves displaced by  $\frac{2}{3}\pi$ , no triplen harmonics exist. The outputs comprise harmonics given by the series  $n = 6r \pm 1$  with an integer  $r \ge 0$ . The  $n^{th}$ harmonic has a magnitude of  $\frac{1}{n}$  relative to the fundamental. In Fig. 2.13 are indicated the main properties for a three-phase inverter output voltage.

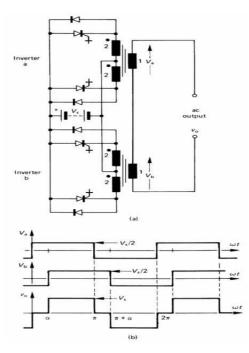

Another technique to control the inverter scheme presented in Fig. 2.8 consists in a conduction phase for each switch equal to  $\frac{2}{3}\pi$  [63]. As a result, at any instant, only two switches (one upper and one non-a complementary lower) conduct and the resultant quasi-square output voltage waveforms are shown in Fig. 2.15.

A  $\frac{\pi}{3}$  radiants dead-time exists between two series switches conducting that implies providing a safety margin against simultaneous conduction of the two series devices across the dc supply. However, a lower semi-conductor device utilisation and less rms output voltage are present.

Fig. 2.9. A three-phase bridge inverter employing  $\pi$  switch conduction with a resistive load: (a) the bridge circuit (b) circuit voltage and current waveforms.

By an analysis of the results above exposed it is easy to verify that the line to neutral voltage of one conduction pattern is proportional to the line-to-line voltage of the other.

### 2.3 Common inverter control techniques

In the most of the applications cases it is required to set up both the amplitude and frequency of the load voltage and current or, in the case of an induction

| Interval | Three conducting switches |                |                |                |                |                |                |                | leg state | voltage vector |

|----------|---------------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------|----------------|

| 1        | T <sub>1</sub>            | T <sub>2</sub> | T <sub>3</sub> |                |                |                |                |                | 101       | V5             |

| 2        |                           | T <sub>2</sub> | T <sub>3</sub> | T <sub>4</sub> |                |                |                |                | 001       | V1             |

| 3        |                           |                | T <sub>3</sub> | T4             | T <sub>5</sub> |                |                |                | 011       | V3             |

| 4        |                           |                |                | T4             | T <sub>5</sub> | T <sub>6</sub> |                |                | 010       | V2             |

| 5        |                           |                |                |                | T <sub>5</sub> | T <sub>6</sub> | T <sub>1</sub> |                | 110       | V6             |

| 6        |                           |                |                |                |                | T <sub>6</sub> | T <sub>1</sub> | T <sub>2</sub> | 100       | V4             |

Fig. 2.10. Quasi-square-wave six conduction states -  $\pi$  radiants

motor, to control the shaft speed and torque by maintaining a constant V/f ratio. The main VSI modulation control techniques are the following:

- Variable voltage dc link;

- Single-pulse width modulation;

- Multi-pulse width modulation;

- Multi-pulse, selected notching modulation;

- Sinusoidal pulse width modulation;

- Triple injection

- Triplens injected into the modulation waveform;

- Voltage space vector modulation;

#### 2.3.1 Variable voltage dc link

The rms voltage of a square-wave can be changed and controlled by varying the dc link source voltage. A variable dc link voltage can be achieved with a dc chopper or an ac phase-controlled thyristor bridge. A dc link L-C smoothing filter may be necessary.

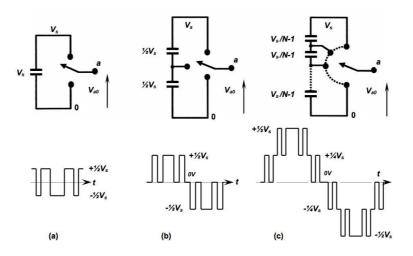

#### 2.3.2 Single-pulse width modulation

Simple pulse-width control can be employed where a single-phase bridge is used to produce a quasi-square-wave output voltage as shown in Fig. 2.16. By phase-shifting the output by  $\alpha$ , a quasi-square sum results as shown in Fig. 2.16 (b).

The output voltage can be described by the following expression

$$V_o = \sum_{n \text{ odd}}^{\infty} v_{an} \sin n\omega t, \qquad (2.39)$$

where

$$v_{an} = \frac{4}{n\pi} V_s \cos \frac{1}{2} n\alpha. \tag{2.40}$$

Fig. 2.11. Determination of the line-to-neutral voltage waveforms for a balanced resistive load and  $\pi$  radiants conduction.

The rms output voltage is  $V_r = V_s \sqrt{1 - \frac{\alpha}{\pi}}$  and the rms value of the fundamental is

$$V_1 = \frac{2\sqrt{2}}{\pi} V_s \cos\frac{1}{2}\alpha. \tag{2.41}$$

The amplitude of the harmonics increases as parameter  $\alpha$  increases and in the meanwhile becoming comparable with the fundamental magnitude. This type of control may be used in high power applications.

Fig. 2.12. Generation and arrangement of the six quasi-square inverter output voltage states.

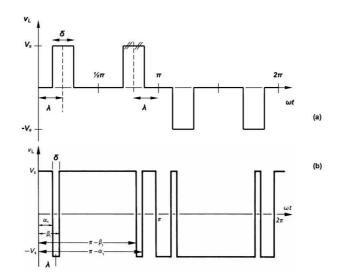

#### 2.3.3 Multi-pulse width modulation

An extension of the single-pulse modulation technique is multiple-notching as shown in Fig. 2.17. The bridge switches are controlled in order to vary the **on** to **off** time of each notch, namely  $\delta$ , thereby varying the output rms voltage which is given by  $V_{rms} = \sqrt{\delta}V_s$ . Alternatively, the number of notches can be varied. The harmonic content at lower output voltages is significantly lower than the one obtained with single-pulse modulation. The increased switching frequency does increase the magnitude of higher order harmonics and the switching losses. The Fourier coefficients of the output voltage are given by

$$V_n = \frac{4}{n\pi} \sum_{j=1,2,3,\dots}^{\frac{f_c}{f_0}} \left[ \cos 2\pi \frac{f_o}{f_c} n(2j-1+\delta) - \cos 2\pi n \frac{f_o}{f_c} (2j-1-\delta) \right], \quad (2.42)$$

where  $0 \le \delta \le 1$  is the duty cycle.

| Conduction Fundamental voltage Characteristic |                            |                            |                          |                   |                            |  |  |

|-----------------------------------------------|----------------------------|----------------------------|--------------------------|-------------------|----------------------------|--|--|

| period                                        | peak                       | rms                        | Total rms                | Distortion Factor | THD                        |  |  |

| ·                                             | $\hat{V}_1$                | $V_1$                      | V <sub>rms</sub>         | μ                 | thd                        |  |  |

| 180°                                          | (V)                        | (V)                        | (V)                      |                   |                            |  |  |

| Phase<br>Voltage                              | $\frac{2}{\pi}V_s$         | $\frac{\sqrt{2}}{\pi}V_s$  | $\frac{\sqrt{2}}{3}V_s$  | $\frac{3}{\pi}$   | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| <b>V</b> <sub>L-N</sub>                       | $= 0.637 V_{s}$            | $= 0.450 V_{s}$            | $= 0.471 V_{s}$          | = 0.955           | = 0.311                    |  |  |

| Line<br>Voltage                               | $\frac{2\sqrt{3}}{\pi}V_s$ | $\frac{\sqrt{6}}{\pi}V_s$  | $\sqrt{\frac{2}{3}} V_s$ | $\frac{3}{\pi}$   | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| <b>V</b> <sub>L-L</sub>                       | $= 1.10 V_{s}$             | $= 0.78 V_{s}$             | $= 0.816 V_{s}$          | = 0.955           | = 0.311                    |  |  |

| 120°                                          | (V)                        | (V)                        | (V)                      |                   |                            |  |  |

| Phase<br>Voltage                              | $\frac{\sqrt{3}}{\pi}V_s$  | $\frac{\sqrt{6}}{2\pi}V_s$ | $\frac{1}{\sqrt{6}}V_s$  | $\frac{3}{\pi}$   | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| <b>V</b> <sub>L-N</sub>                       | $= 0.551 V_{s}$            | $= 0.390 V_s$              | $= 0.408 V_{s}$          | = 0.955           | = 0.311                    |  |  |

| Line<br>Voltage                               | $\frac{3}{\pi}V_s$         | $\frac{3}{\sqrt{2}\pi}V_s$ | $\frac{1}{\sqrt{2}}V_s$  | $\frac{3}{\pi}$   | $\sqrt{\frac{\pi^2}{9}-1}$ |  |  |

| <b>V</b> <sub>L-L</sub>                       | $= 0.955 V_{s}$            | $= 0.673 V_s$              | $= 0.707 V_{s}$          | = 0.955           | = 0.311                    |  |  |

Fig. 2.13. Quasi-squarewave voltage properties.

#### 2.3.4 Multi-pulse, selected notching modulation

A multi-level waveform  $(\pm V_s, 0)$  can be used with quarter wave symmetry, as shown in Figure 2.17, to control both the harmonics and total rms output voltage. If only one pulse is chosen per quarter wave, the  $k^{th}$  harmonic can be annihilated from the output voltage if the centre of the pulse is located such that

$$\sin(k\lambda) = 0$$

i.e.  $\lambda = \frac{\pi}{k}$ . (2.43)

The output voltage total rms depends only on the pulse width  $\delta$  and is given by  $V_s \sqrt{\frac{2}{\pi}} \delta$ . On the other hand, the bipolar waveform  $(\pm V_s)$  has an rms value of  $V_s$ , independent of the harmonics eliminated. The exact switching points are calculated off-line so as to eliminate the required harmonics. It has to be remarked that the more notches, the lower is the output fundamental. The multi-pulse selected notching modulation technique can be translated into a *optimal pulse-width modulation problem control*, where harmonics may not be eliminated, but minimized according to a specific cost function. In this framework, the switching angles that are present in the quarter wave output are tuned to eliminate certain harmonics, minimizing the rms of the ripple current or any other desired performance index. The resultant nonlinear equations are solved using numerical methods off-line. A set of angles

**Fig. 2.14.** A three-phase bridge inverter employing  $\frac{2}{3}\pi$  switch conduction with a resistive load: (a) the circuit with  $T_1$  and  $T_2$  conducing and (b) voltage and current waveforms

| Interval |                |                | Two conducting devices |                |                |                |                |  |

|----------|----------------|----------------|------------------------|----------------|----------------|----------------|----------------|--|

| 1        | T <sub>1</sub> | T <sub>2</sub> |                        |                |                |                |                |  |

| 2        |                | T <sub>2</sub> | T <sub>3</sub>         |                |                |                |                |  |

| 3        |                |                | T <sub>3</sub>         | T <sub>4</sub> |                |                |                |  |

| 4        |                |                |                        | T <sub>4</sub> | T <sub>5</sub> |                |                |  |

| 5        |                |                |                        |                | T <sub>5</sub> | $T_6$          |                |  |

| 6        |                |                |                        |                |                | T <sub>6</sub> | T <sub>1</sub> |  |

Fig. 2.15. Quasi-square wave conduction states -  $\frac{\pi}{3}$  radiants conduction.

Fig. 2.16. Voltage control by combining phase-shifted push-pull inverters: (a) two inverters scheme and (b) circuit voltage waveforms for a phase displacement  $\alpha$

Fig. 2.17. Inverter control giving variable duty cycle of five notches per half cycle: (a) low and (b) higher duty cycle

must be computed and stored for each desired level of the voltage fundamental and output frequency. The optimal pwm approach is particularly useful for high-power, high-voltage GCT thyristor inverters which tend to be limited in switching frequency by device switching losses.

#### 2.3.5 Sinusoidal pulse-width modulation

The sinusoidal pulse-width modulation can be furthermore classified in

- natural sampling modulation, or

- regular sampling modulation.

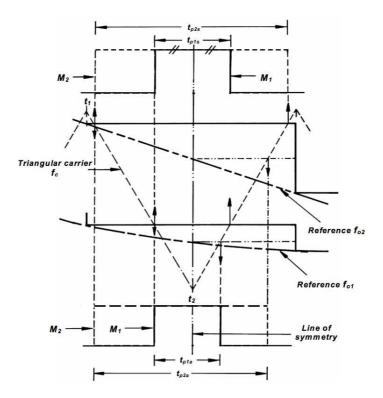

Both the methodologies can be split also into modulation with synchronous carrier and modulation with asynchronous carrier. The output voltage waveform generated by synchronous carrier, natural sampling sinusoidal pwm are illustrated in Figure 2.7. The switching points are determined by the intersection of the triangular carrier wave and the reference modulation sine wave. The output frequency is at the sine-wave frequency  $f_o$  and the output voltage is proportional to the magnitude of the sine wave. The parameter M, with  $(0 \le M \le 1)$ , is called the modulation index. If the frequency of the modulation sine wave, namely  $f_o$ , is an integer multiple of the triangular wave carrier-frequency, indicated as  $f_c$  that is,  $f_c = nf_o$  where n is integer, then the modulation is synchronous, as shown in Figure 2.7. If n is odd then the positive and negative output half cycles are symmetrical and the output voltage contains no even harmonics. In a three-phase system if n is a multiple of 3 (and odd), the carrier is a triplen of the modulating frequency and the spectrum does not contain the carrier or its harmonics,

$$f_c = (6q+3)f_o = nf_o \quad q = 1, 2, 3, \dots$$

(2.44)

The Fourier harmonic coefficients of the line to line voltages are given by

$$a_n = V_l \cos\left(\frac{n}{1}\pi\right) \cos\left(\frac{n}{3}\pi\right),$$

(2.45)

$$b_n = V_l \sin\left(\frac{n}{1}\pi\right) \sin\left(\frac{n}{3}\pi\right) \tag{2.46}$$

where  $V_l$  is proportional to the dc supply voltage  $V_s$  and the modulation index M. The carrier frequency must be much higher than the modulation frequency. The generated output voltage pulses are modulated such that their duration is proportional to the instantaneous value of the sinusoidal waveform at the centre of the pulse; that is, the pulse area is proportional to the corresponding value of the modulating sine wave. If the carrier frequency is very high, an averaging effect occurs, resulting in a sinusoidal fundamental output with high-frequency harmonics, but minimal low-frequency harmonics. Rather than using two offset triangular carriers, as shown in Figure 2.7, a triangular carrier without offset can be used. To better clarify such a technique, Figure 2.18

shows the pwm generation scheme and the voltage bipolar output waveform, when applied to the three-phase VSI inverter. Only one switch in the inverter leg must always be on.

Fig. 2.18. Output voltage harmonic reduction for a single-phase bridge using selected notching: (a) multilevel output voltage and (b) bipolar output voltage

Unlike the waveforms reported in Figure 2.17, no zero voltage output periods exist. This has the effect that, in the case of GCT thyristor bridges, a large number of commutation cycles is required. In the presence of zero output periods, in fact, one GCT thyristos is commutated and the complementary device in that leg is turned off. The previously commutated device can be turned back on without the need to commutate the complementary device, as would be required in other cases. Commutation losses are reduced, control circuitry simplified and the likelihood of simultaneous conduction of two series leg devices is reduced. When the carrier is not an integer multiple of the modulation waveform, asynchronous modulation results. Because the output frequency  $f_o$  is usually variable over a wide range, it is difficult to ensure  $f_c = n f_o$ . To achieve synchronism, the carrier frequency must vary with frequency  $f_o$ . Simpler generating systems are obtained if a fixed carrier frequency is used, resulting in asynchronism between  $f_o$  and  $f_c$  at most output frequencies. When a fixed carrier frequency is used, usually no attempt is made to synchronize the modulation frequency. The output waveforms do not have quarter-wave symmetry which produces sub-harmonics. Such subharmonics can be neglected if  $f_c \gg f_o$ , usually,  $f_c > 20 f_o$ . The implementation of sinusoidal pwm with microprocessors or digital signal processors is common because of flexibility and the elimination of analogue circuity associated problems. The digital pwm generation process involves scaling, by multiplication, of the per unit sine-wave samples stored in ROM. The multiplication process is time-consuming [63, 65], hence natural sampling is not possible. In order to minimize the multiplication rate, the sinusoidal sine-wave reference is replaced by a quantised stepped representation of the sine-wave. Figure 2.19 shows two methods where sampling is synchronized to the carrier frequency and the multiplication process is performed at twice the sampling rate for three-phase pwm generation (the third phase can be expressed in terms of two phases).

Fig. 2.19. Regular sampling, asynchronous, sinusoidal pulse-widt-modulation: (a) symmetrical and (b) asymmetrical modulation

In the (a) part of Figure 2.19 there is illustrated the process of symmetrical modulation, where sampling is at the carrier frequency. The quantized

sine-wave is stepped and held at each sample point. The triangular carrier is then compared with the step sine-wave sample and the modulation process is termed symmetrical modulation because the intersection of adjacent sides of the triangular carrier with the stepped sine-wave, about the non-sampled carrier peak, are equidistant about the carrier peak. The pulse width, independently of the modulation index M, is symmetrical about the triangular carrier peak not associated with sampling, as illustrated by the upper pulse in Figure 2.20.

Fig. 2.20. Regular sampling, asynchronous, sinusoidal pulse-widt-modulation

The pulse width can be expressed as follows

$$t_{ps} = \frac{1}{2f_c} (1 - M\sin 2\pi f_o t_1) \tag{2.47}$$

where  $t_1$  is the time of sampling. Asymmetrical modulation is produced when the carrier is compared with a stepped sine wave produced by sampling and holding at twice the carrier frequency, as shown in Figure 2.19(b). Each side of the triangular carrier about a sampling point intersects the stepped waveform at different step levels. The resultant pulse width is asymmetrical about the sampling point. The pulse width can be now expressed as

$$t_{pa} = \frac{1}{2f_c} \left[ 1 - \frac{1}{2} M \left( \sin 2\pi f_o t_1 + \sin 2\pi f_o t_2 \right) \right]$$

(2.48)

where  $t_1$  and  $t_2$  are the times at sampling such that  $t_2 = t_1 + \frac{1}{2f_c}$ . Figure 2.20 shows that a change in the modulation index M varies the pulse width on each edge, termed double edge modulation. A triangular carrier produces double edge modulation, while a sawtooth carrier produces single edge modulation, independent of the sampling technique.

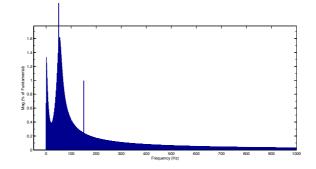

## Frequency spectra comparison

The most common technique of sinusoidal modulation for three-phase inverters is represented by the regular-sampling, asynchronous, fixed frequency carrier pulse width modulation. If  $f_c > 20f_o$ , low frequency sub-harmonics can be neglected. The output spectra consists of the modulation frequency  $f_o$  with magnitude M. Other spectra components are also present associated with the triangular carrier,  $f_c$ . For any sampling, these are  $f_c$  and the off harmonics of  $f_c$ . These decrease in magnitude with increasing frequency. About the frequency  $nf_c$  there exist components of  $f_o$  spaced at  $\pm 2f_o$  which generally decrease in magnitude when further away from  $nf_c$ , i.e., at  $f_c$  the no-zero harmonics are  $f_c$ ,  $f_c \pm 2f_o$ ,  $f_c \pm 4f_o$ , ..., while about  $2f_c$  the present harmonics are  $2f_c \pm f_0$ ,  $2f_c \pm 3f_o$ , ..., but  $2f_c$  is not present. The typical output spectrum is shown in Figure 2.21. The relative magnitudes of the side-bands vary with modulation depth and the carrier related frequencies present  $f_h$  are given by

$$f_k = \frac{1}{2} \left( 1 + (-1)^{n+1} \right) n f_c \pm \left( 2k - \frac{1}{2} \left( 1 - (-1)^n \right) \right) f_c, \tag{2.49}$$

where k = 1, 2, 3, ... (side-bands) and n = 1, 2, 3, ... (carrier).

Fig. 2.21. Location of carrier harmonics and modulation frequency sidebands

The main difference between the proposed technique with respect to other various PWM techniques consists in the magnitude of the carrier harmonics and side-bands. The magnitude increase as the PWM type changes from naturally sampling to regular sampling, then from asymmetrical to symmetrical modulation, and finally from double edge to single edge. With a three-phase inverter, the carrier  $f_c$  and its harmonics do not appear in the line-to-line voltages since the carrier  $f_c$  and in particular its harmonics, are co-phasal to the three modulation waveforms. The magnitude of the fundamental when using standard pulse width modulation can be increased without introducing output voltage distortion, by the injection of triplen components, which are co-phasal in a three-phase system, and therefore do not appear in the line currents. Two basic approaches can be used to affect this undistorted output voltage magnitude increase

- triplen injection into the modulation waveform, or

- voltage space vector modulation.

## 2.3.6 Triplen injection modulation

## Triplens injected into the modulation waveform

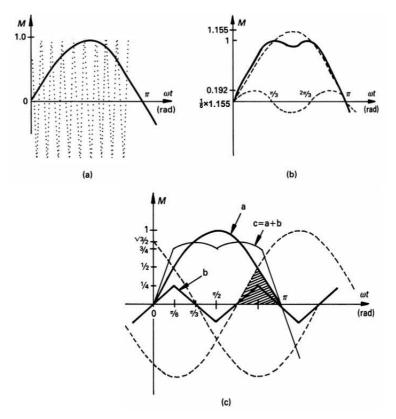

The third harmonic voltage injection permits to obtain higher magnitude of the output three-phase generated voltage with respect to the standard techniques. If over-modulation (M > 1) is not allowed, then the modulation wave  $M \sin \omega t$  is restricted in magnitude to M = 1, as shown in Figure 2.22. In a three-phase pwm generator, to increase possible values of parameter M, it can be used the propriety of harmonics cancellation at  $3f_o$  (and off multiplies of  $3f_o$ ), yet ensuring modulation occurs for every carrier frequency cycle. The voltage  $V_{RN}$  has a maximum instantaneous value equal to the unity, at  $\omega t = \pm \frac{1}{3}\pi$ .

The fundamental of the phase voltage is M' = 1.155M. The increased fundamental has been reported in Figure 2.22(b). The spatial voltage vector technique injects the triplens in according to the following expression

$$V_{RN} = M' \left\{ \sin \omega t + \frac{1}{\sqrt{3}} \sum_{r=0}^{\infty} \frac{(-1)^r}{\left[ (2r+1) - \frac{1}{3} \right] \left[ (2r+1) + \frac{1}{3} \right]} \right\}.$$

(2.50)

Therefore, the spatial voltage vector waveform is defined as

$$\overline{v} = \begin{cases} \frac{3}{2}\sin(\omega t) & 0 \le \omega t \le \frac{1}{6}\pi\\ , \frac{\sqrt{3}}{2}\sin(\omega t + \frac{1}{6}\pi) & \frac{1}{6}\pi & leq\omega t \le \frac{1}{2}\pi. \end{cases}$$

(2.51)

The use of this reference increases the duration for the zero volt loops, thereby decreasing inverter output current ripple. The maximum modulation index is 1.155. Third harmonic injection, yielding M = 1.155 is a satisfactory approximation to spatial voltage vector injection.

**Fig. 2.22.** Modulation reference waveforms: (a) sinusoidal reference; (b) third harmonic injection reference, and (c) triplen injection reference

### 2.3.7 Voltage space vector PWM

When generating three-phase quasi-square output voltages, the inverter switches step progressively to each of the six switch output possibilities (states). In Figure 2.12 when producing the quasi-square output, each of these six states is represented by an output voltage space vector that has a delay equal to  $\frac{\pi}{3}$  from its two adjacent states, with the same length  $V_s$ . Therefore, the quasi-square three-phase output is generated by a rotating vector of length  $V_s$ , jumping successively from one output state to the next in the sequence, and creating six voltage output sectors. The speed of rotation, in particular the time for one rotation, determines the inverter output frequency. The sequence of voltage vectors  $\{v_i, i = 1..., 5\}$  is arranged such that stepping from one state to the next involves only one of the three poles changing state. Thus the number of inverter devices, needing to change states (switch) at each transition, is minimised. The speed of rotation can be naturally changed: from one voltage space vector position to the next, producing a six-step quasi-square fixed mag-

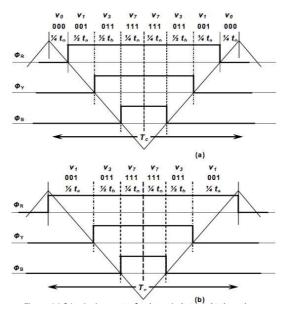

nitude voltage output, the rotating vector is rotated in smaller steps based on the position being updated at a constant rate(carrier frequency). Furthermore, the vector length can be varied, modulating it, to a magnitude less than  $V_s$ . To incorporate a variable rotating vector length (modulation depth), it is necessary to vary the average voltage in each carrier period. Hence pulse width modulation is used in the period between each finite step of the rotating vector. Pulse width modulation requires the introduction of zero voltage output states, namely all the top switches on (state 111,  $v_7$ ), or all the lower switches on (state  $000, v_0$ ) (see Figure 2.23).

Fig. 2.23. Instantaneous output voltage states for the three legs of an inverter

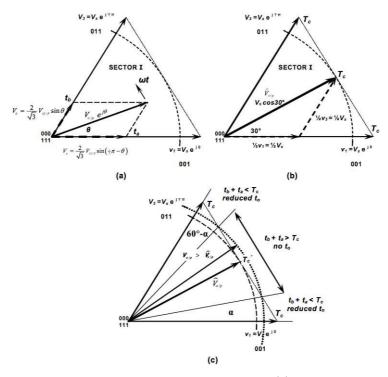

The pole-to-pole output voltage can be annihilated, which allows duty cycle variation to achieve variable average output voltage for each phase, within carrier period, proportional to the magnitude of the position vector. There can exist vector configurations (or angles) that can be expressed as one of the six quasi-square output vector. To overcome such drawbacks, an intermediate vector  $V_{o/p}e^{j\theta}$  is resolved into the vector sum of the two quasi- square vectors

adjacent to the rotating vector. This process is shown in Figure 2.24 for a voltage vector  $V_{o/p}$  that lies in sector I, between output states  $v_1(001)$  and  $v_3(011)$ . It is easy to observe that such vector has been resolved as sum of the two components  $V_a$  and  $V_b$ .

Fig. 2.24. First sector of inverter operational area: (a) general rotating voltage vector (b) maximum allowable voltage vector length (c) over modulation.

The time represented by quasi-square vectors  $v_1$  and  $v_3$  is the carrier period  $T_c$ , in each case. Therefore the portion of  $T_c$  associated with  $v_a$  and  $v_b$  is scaled proportionally to  $v_1$  and  $v_3$ , giving  $t_a$  and  $t_b$ . The sum of such times cannot be greater than the carrier period  $T_c$ , by providing

$$t_a + t_b \le T_c \tag{2.52}$$

and

$$t_o + t_a + t_b = T_c, (2.53)$$

where the variable  $t_o$  represents a slack variable that is used to obtain an equality. Eq. (2.53) shows that the vector  $v_1$  is used for a period  $t_a$ , whereas  $v_3$  is used for a period  $t_b$ , and during period  $t_o$ , the null vector is used,  $v_0$  and  $v_7$  at the centre of the hexagon, which do not affect the average voltage

during the carrier interval  $T_c$ . A further constraint is imposed in the time domain. The rotating voltage vector is a fixed length for all the rotating angles, for a given inverter output voltage. Its length is restricted in both time and space. Obviously the resolved component lengths cannot exceed the pole vector length,  $V_s$ . Additionally, the two vector magnitudes are each a portion of the carrier period, where  $t_a$  and  $t_b$  could be both equal to  $T_c$ , that is, they both have a maximum length  $V_s$ . The shortest vector to the boundary is when both resolving vectors have a length  $\frac{1}{2}V_s$ . In this case,  $t_a = t_b =$  $\frac{1}{2}T_c$ , that is  $t_a + t_b = T_c$ . Therefore for a constant inverter output voltage, when the rotating voltage vector has a constant length  $V_{o/p}$ , the locus of allowable rotating reference voltage vectors must be within the circle described by the maximum length vector. This vector has length  $v_1 \cos 30^\circ$  and the full quasi-square vectors  $v_1, v_2$  etc., which have a magnitude of  $V_s$ , cannot be used for generating a sinusoidal output voltage. The excess length of each quasisquare voltage (which represents time) is accounted for by using zero state voltage vectors for a period corresponding to that extra length (  $1 - \cos 30^{\circ}$ at maximum output voltage). Having calculated the necessary periods for the inverter poles  $(t_a, t_b \text{ and } t_0)$ , the carrier period switching pattern can be assigned in two ways:

- Minimised current ripple, and

- Minimised switching losses, using dead banding.

**Fig. 2.25.** Assignment of pole periods  $t_a$  and  $t_b$ : (a) minimum current ripple and (b) minimum switching transitions per carrier cycle.

Figure 2.25 reports both the scenarios. The waveforms are based on the equivalent of symmetrical modulation where the pulses are symmetrical about the carrier trough. Minimization of current ripple or switching transitions can be chosen. When dead banding, the zero voltage state  $v_0$  is used in even numbered sextants and  $v_7$  is used in odd numbered sextants. Side-band and harmonic component magnitudes can be decreased if double-edged modulation placement of the states is used, which requires recalculation of  $t_a, t_b$  and  $t_o$  at the carrier crest, as well as at the trough.

# 2.4 CSI bridge topologies

In the current source inverters (see [50, 21, 58, 18]), the dc supply presents high values of reactance, being inductive to maintain the required inverter output bidirectional current regardless the inverter load.

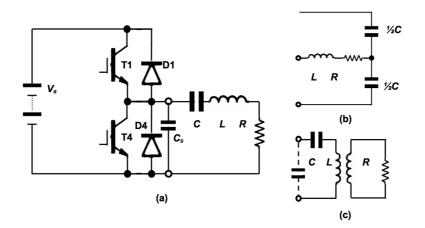

## 2.4.1 Single-phase inverter

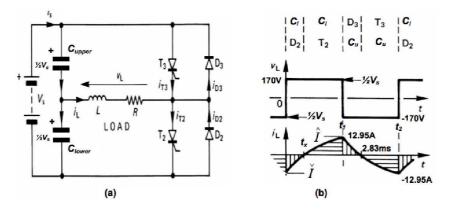

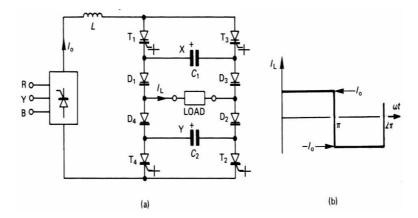

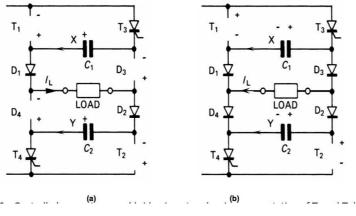

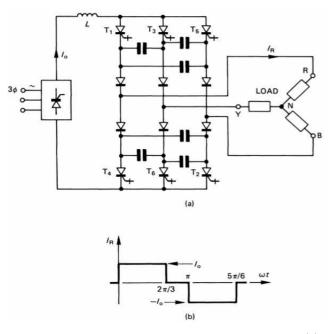

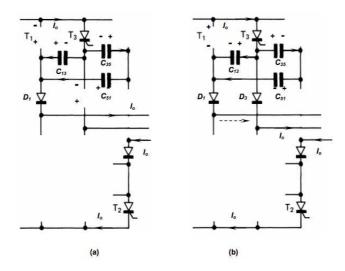

A single-phase, controlled current-sourced bridge is shown in Fig 2.26 with its near square-wave output current.

Fig. 2.26. Single-phase csi bridge inverter: (a) bridge circuit and (b) load current waveform

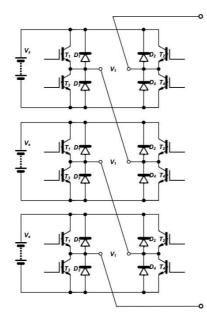

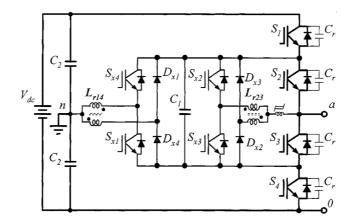

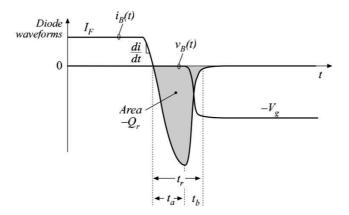

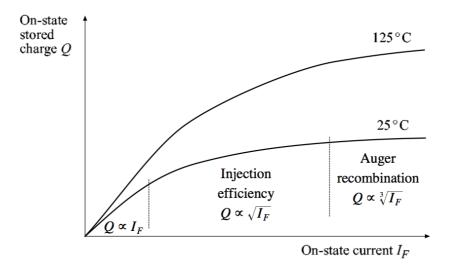

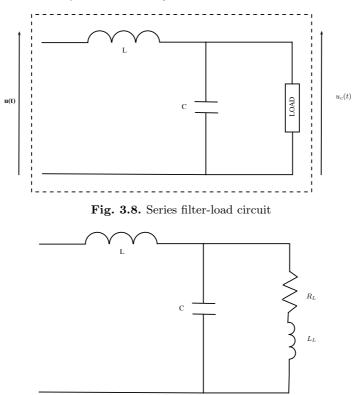

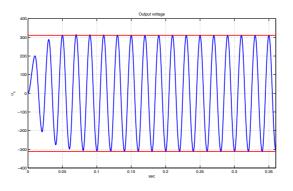

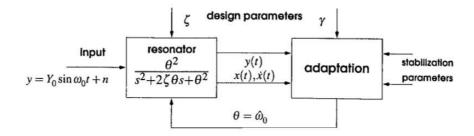

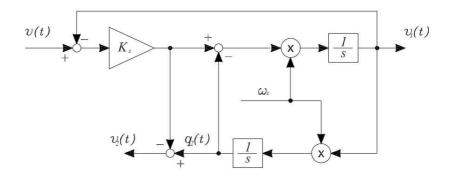

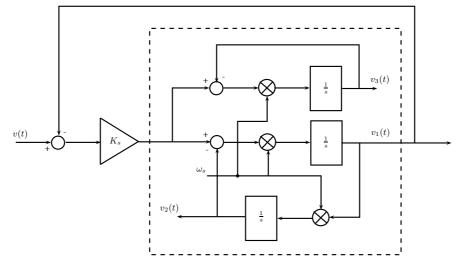

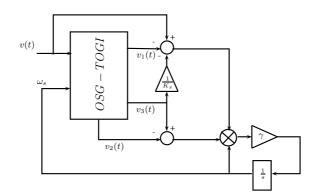

No free-wheel diodes are required and the thyristors required forced commutation and have to withstand reverse voltages. An inverter current path must be maintained at all times for the source controlled current. The circuit can be described by considering two phases. Firstly thyristors  $T_1$  and  $T_2$  are commutated by triggering thyristors  $T_3$  and  $T_4$ . The capacitors impress negative voltages across the respective thyristors to be commutated off, as shown