## UNIVERSITÀ DELLA CALABRIA

Dipartimento di Fisica

Scuola di Dottorato "Archimede" in Scienze, Comunicazione e Tecnologie

Indirizzo: Scienze e Tecnologie dei Sistemi Complessi

Con il contributo di Secretaría de Educación Superior, Ciencia, Tecnología e Innovación SENESCYT - ECUADOR

(Ciclo XXVII)

### New Methodologies and Instrumentations for Power Semiconductor Devices Testing

Settore Scientifico Disciplinare: ING-INF/01

Direttore:

Ch.mo. Prof. Pietro PANTANO Firma Pieto Serto

Supervisore:

Ch.mo. Prof Calogero PACE

Firma Coloque Reco

Correlatore:

Ch.ma. Dott.ssa, Letizia FRAGOMENI Firma Dottorando:

Dott. Jorge Luis HERNANDEZ AMBATO Firma

Novembre 2015

Mira que te mando que te esfuerces y seas valiente; no temas ni desmayes, porque Jehová tu Dios estará contigo en dondequiera que vayas. Jos 1:9.

Dedicado a mi amada esposa Diana, mi queridos padres Jorge y Martha, mis hermanas Catty y Valeria, mis hermanos, mis tesoros Paula y Victoria, mi familia y todas las personas que aportaron a mi vida durante todo este tiempo. Dios los colme de bendiciones!.

## Acknowledgements

De todo corazón, quiero agradecer a Dios por haberme sostenido y provisto todos estos años. A mi dulce esposa, que no obstante todo, ha sabido darme su amor y apoyo en todas la circunstancias de este periodo. Un agradecimiento especial al Pueblo Ecuatoriano y SENESCYT, que hizo posible este sueño. Un sentido saludo y agradecimiento al Prof. Calogero Pace que supo como guiarme, fortaleciendo mis destrezas y retandome a alcanzar unas nuevas. Aprovecho para agradecer a STMicroelectronics en la persona del Ing. Giusseppe Consentino y mis amigos Donatella De Pasquale y Alessandro Dignoti. Un saludos por igual a todos los amigos(as) que conocí en el NexusLab, en especial a Carlo Giordano y Letizia Fragomeni que supieron brindarme su amistad y aporte inigualable. Mi agradecimiento a la gran familia "Siloe" en la persona del Pt. Marco Lienhard y su familia que han aportado tanto a mi vida durante estos años. Finalmente, pero no menos importante, un reconocimiento a todas aquellas personas, amigos y ajenos, que estando en tierra lejana, me hicieron sentir como si fuera a casa!

Rende, novembre 2015

Jorge L. Hernandez Ambato

## Abstract

Nowadays electronic applications involve a high density of power Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) which represent the major percentage of energy flow to be controlled. Moreover, new technologies, such as Silicon Carbide (SiC), have been well involved in the existing power applications. Therefore, the reliability of power devices is highly demanded.

Since decades, a widely used accelerated test to evaluate the reliability of MOSFETs is the so-called High Temperature Reverse Bias (HTRB). In this stress test, the Devices Under Test (DUTs) are reverse polarized at a certain percentage of the rated breakdown voltage and maintained in this condition at high temperature for a determined long time. A typical HTRB test also incorporates Electrical Characterization Tests (ECTs) of DUTs before and after each stress period, seeking for failed devices. However, time elapsed between ECTs are long and degradation and failure information of DUTs might not be registered.

In this context, an advanced methodology for HTRB test is proposed. The latter consists of applying more stress cycles of short duration together with more frequent ECTs at a relatively high temperature that can be directly compared to that of normal operation in power applications (i. e. 125 °C). With this methodology, more detailed information about degradation trends in electrical parameters, time of failures and stopping of stress test on degrading devices before full breakdown can be performed. The latter can be very useful in R&D stages, where the post-failure analysis of well-degraded devices, but not broken, is important.

An automatized instrumentation, aimed to apply this methodology, has been implemented. The latter utilizes individual Thermal Control Modules (TCMs) to control the test temperature per single DUT. The temperature control is performed through an opposite mini-heater and firmware running on an 8-bit microcontroller. TCMs can be set remotely to apply test temperatures in the range [30-200 °C]. In addition, Switch Matrix Modules (SSMs) are implemented to configure the electrical connections required for HTRB or ECT tests remotely. A PC application controls all the modules through a Master Communication Module (MCM) also implemented. A commercial Source and Measure Unit (SMU) is used for the electrical stress. Full customization of HTRB and ECTs test parameters can be performed to optimize the stress and degradation data acquisition.

Combining the advanced methodology and instrumentation above mentioned, more stressful conditions can be applied to shorten the overall test time without losing the electrical degradation trends of failing devices. In fact, features of the implemented instrumentation allow for controlling unbeneficial thermal runaway process on the single device, isolating thermal and electric of degraded devices, acquiring frequently electrical parameters data, performing ECTs at a relatively high temperature between shorter stress cycles, managing real-time control of HTRB test. These features are useful to get reliability data in a shorter time than a typical application of HTRB tests while preserving DUTs for post-failure analysis.

The advanced methodology and automatized instrumentation have been applied to Si and SiC power MOSFETs with interesting results, demonstrating to be suitable for both shorter and more accelerated HTRB tests to acquire critical information necessary for the study of degradation processes and reliability in power devices. Moreover, results have demonstrated that degradation trends are not affected when more frequent ECTs at slightly different temperature are performed in the DUTs. In addition, accurate test results have shown that drawbacks of typical HTRB implementation have been solved through the advanced methodology and instrumentation reported.

Complementing the work presented, Low-Frequency Noise Measurements (LFNMs) were also applied as valuable tool to investigate the degradation process in power MOS-FETs after stressing them through HTRB test. A correlation between the results from advanced HTRB test and LFNM in power MOSFETs demonstrates that the electrical degradation is represented by a noise spectrum different to that for intrinsic 1/f noise.

## Riassunto

Le applicazioni elettroniche odierne sono caratterizzate da un'elevata densità di transistori ad effetto di campo di tipo metallo-ossido-semiconduttore (MOSFET) che rappresentano dunque la maggiore sorgente di consumo di energia da gestire. Inoltre, nuove tecnologie, come quella basata sul Silicon Carbide (SiC), sono state impiegate nelle applicazioni ad alta tensione/corrente. L'affidabilità dei dispositivi di potenza è dunque una caratteristica fondamentale.

Da decenni una tipologia di test accelerati largamente impiegata per valutare l'affidabilità dei MOSFET è quella denominata High Temperature Reverse Bias (HTRB). In questi test, i dispositivi da testare sono polarizzati inversamente ad una certa percentuale della tensione di breakdown e mantenuti in queste condizioni ad elevata temperatura per un determinato intervallo di tempo. Tipicamente, prima e dopo ogni ciclo di stress, vengono effettuate delle caratterizzazioni elettriche (Electrical Characterization Tests -ECTs) al fine di valutare eventuali forme di degrado e fallimenti dei dispositivi. Tuttavia, gli ECT sono effettuati ad intervalli di tempo molto lunghi, quindi le informazioni legate ad eventuali forme di degrado e fallimento possono non essere rilevate.

In questo contesto, il lavoro di ricerca si è concentrato principalmente sulla definizione di una metodologia avanzata per la realizzazione dei test HTRB. La procedura proposta consiste nell'applicazione di più cicli di stress a breve durata, intervallati da caratterizzazioni elettriche eseguite a temperature relativamente alte, confrontabili con quelle che si raggiungono normalmente in applicazioni di potenza (cioè, 125°C). Impiegando la metodologia proposta è possibile ottenere informazioni più dettagliate circa l'andamento del degrado dei parametri elettrici ed i tempi di fallimento dei dispositivi. Inoltre, la procedura prevede l'interruzione del test sui dispositivi degradati prima della completa rottura degli stessi. In particolare, quest'ultimo aspetto è rilevante nelle fasi di ricerca e sviluppo, dove l'analisi dei dispositivi danneggiati, ma non totalmente distrutti, consente di ottenere informazioni importanti.

Al fine di applicare la metodologia ideata, è stata sviluppata tutta la strumentazione richiesta. In particolare, questa impiega dei moduli di controllo che consentono di gestire la temperatura dei singoli dispositivi da testare (Thermal Control Module - TCM). Il controllo della temperatura è effettuato attraverso l'uso di adeguati mini-riscaldatori e di un firmware che è eseguito da un microcontrollore ad 8-bit. Il TCM può essere gestito da remoto in modo da impostare una temperatura di test compresa tra 30 °C e 200 °C. Inoltre, è stato necessario implementare una matrice di switch (Switch Matrix Module - SSM) per poter configurare da remoto le connessioni elettriche richieste durante i test HTRB e gli ECT. Un software dedicato gestisce tutti i moduli attraverso un apposito apparato di comunicazione (Master Communication Module - MCM). Uno strumento di misura commerciale di tipo 'Source and Measure Unit (SMU)' è impiegato per gli stress elettrici. L'apparato implementato consente di scegliere i diversi parametri da impostare durante i test HTRB ed ECT in modo da ottimizzare l'acquisizione dei dati.

Impiegando la metodologia proposta insieme alla strumentazione implementata è dunque possibile applicare condizioni di stress più intense riducendo, contemporaneamente, il tempo totale della misura, senza tuttavia perdere informazioni importanti sull'andamento del degrado dei dispositivi. Infatti, le caratteristiche della strumentazione implementata consentono di controllare eventuali processi di deriva termica dei singoli dispositivi, di isolare i dispositivi degradati, di acquisire frequentemente dati sui parametri elettrici eseguendo gli ECT a temperature relativamente elevate ad intervalli di tempo brevi, di gestire in real-time il controllo dei test HTRB. Queste caratteristiche sono utili per ottenere dati di affidabilità in un tempo più breve rispetto alle applicazione dei tipici test HTRB, permettendo inoltre di eseguire analisi successive ad i fenomeni di degrado.

La procedura descritta è stata applicata a dispositivi MOSFET realizzati in silicio ed in SiC ottenendo risultati interessanti e dimostrando, al contempo, che la metodologia ideata è adatta per l'esecuzione di test HTRB più brevi e più accelerati, in modo da acquisire informazioni necessarie per l'analisi dei processi di degrado e dell'affidabilità dei dispositivi di potenza. Inoltre, i risultati sperimentali hanno dimostrato che l'esecuzione più frequente di ECT a temperature leggermente diverse non impattano sugli andamenti di degrado dei dispositivi. Inoltre, la metodologia implementata consente di risolvere i principali svantaggi legati alle procedure standard di test HTRB.

In aggiunta a questo, il presente lavoro riporta l'applicazione di misure di rumore a bassa frequenza come utile strumento per investigare ed individuare i meccanismi di fallimento indotti dai test HTRB sui dispositivi MOSFET di potenza. Le misure effettuate dimostrano l'esistenza di una correlazione tra lo spettro di rumore dei dispositivi sottoposti a stress ed i relativi test HTRB: in particolare, i risultati ottenuti mostrano che lo spettro di rumore differisce da quello intrinseco rappresentato dal rumore 1/f.

## Pubblication List

#### **Conference contributions**

- C. Pace, J. Hernandez-Ambato, and C. Giordano, "A Novel Instrumentation for an Advanced High Temperature Reverse Bias (HTRB) Testing on Power Transistors," Applications in Electronics Pervading Industry, Environment and Society (APPLEPIES), 2014. (*in edition*)

- G. Consentino, M. Laudani, G. Privitera, C. Pace, C. Giordano, J. Hernandez-Ambato, and M. Mazzeo, "Effects on power transistors of Terrestrial Cosmic Rays: Study, experimental results and analysis," in Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE, 2014, pp. 2582–2587, doi: 10.1109/ APEC.2014.6803667.

- G. Consentino, D. De Pasquale, S. Galiano, A. D. Ignoti, C. Pace, J. Hernandez-Ambato, M. Mazzeo, and C. Giordano, "Innovative Instrumentation for HTRB Tests on Semiconductor Power Devices," in AEIT Annual Conference, 2013, pp. 1–5, doi: 10.1109/ AEIT.2013.6666814.

- 4. G. Consentino, M. Laudani, G. Privitera, A. Parlato, N. Marchese, E. Tomarchio, C. Pace, C. Giordano, M. Mazzeo, and J. Hernandez-Ambato, "Dangerous effects induced on power MOSFETs by terrestrial neutrons: A theoretical study and an empirical approach based on accelerated experimental analysis," in AEIT Annual Conference, 2013, 2013, pp. 1–6, doi: 10.1109/AEIT.2013.6666813.

### Journal papers

C. Pace, J. Hernandez-Ambato, D. De Pasquale, and G. Consentino, "Instrumentation for Innovative Semiconductor Power Devices Reliability Tests," Int. J. Eng. Ind., vol. 4, no. 2, pp. 119–127, 2013, doi: 10.4156/ijei.vol4.issue2.14.

## Acronyms

**ADC** Analog to Digital Converter **ADT** Accelerated Degradation Testing AEC Automotive Electronics Council **ALT** Accelerated Life Test **CNP** Charge Neutrality Point **COTS** Commercial On The Shelf **DFT** Discrete Fourier Transform **DMOSFET** Double Diffused MOSFET  $\mathbf{DUT}$  Device Under Test  ${\bf ECT}$  Electric Characterization Test **EECT** Emergency Electric Characterization Test  ${\bf EVT}$  Electric Verification Test **FIT** Failures In Time GPIB General Purpose Interface Bus **GUI** Graphical User Interface HALT Highly Accelerated Life Testing **HASS** Highly Accelerated Stress Screening HTRB High Temperature Reverse Bias HTGB High Temperature Gate Bias

HTS High Temperature Storage Life

H3TRB High Humidity High Temperature Reverse Bias

**IDE** Inter-Digitated Electrode

**IEC** International Electrotechnical Commission

**IGBT** Insulated Gate Bipolar Transistor

$\mathbf{I}^{2}\mathbf{C}$  Inter-Integrated Circuit

**JEDEC** Joint Electron Device Engineering Council

LFN Low-Frequency Noise

LFNM Low-Frequency Noise Measurement

LPEG Liquid-Phase Exfoliated Graphene

LTS Low Temperature Storage Life

$\mathbf{MCM}$  Master Communication Module

MIL-DoD Military Department of Defense of United States

**MOSFET** Metal Oxide Semiconductor Field Effect Transistor

${\bf MS}\,$  Mechanical Shock

$\mathbf{MTTF}\,$  Mean Time To Failure

**MTBF** Mean Time Between Failure

${\bf NI}$  National Instruments

$\mathbf{PC}$  Power Cycling

$\mathbf{PCB}$ Printed Circuit Board

${\bf PWM}\,$  Pulse Width Modulation

**PID** Proportional Integrative Derivative

**PSD** Power Spectral Density

**RAT** Reliability Acceptance Test

$\mathbf{R}\&\mathbf{D}$  Research and Development

**RDT** Reliability Demonstration Test

**RTS** Random-Telegraph-Signal

**SAFeFET** Surface Added Feature Field Effect Transistor

SCPI Standard Commands for Programmable Instrumentation

${\bf SEM}\,$  Scanning Electron Microscopy

${\bf SMD}\,$  Surface Mounting Device

${\bf SMM}$  Switch Matrix Module

${\bf SMU}$  Source and Measuring Unit

TAT Thermal Adjustment Tool

${\bf TC}\,$  Temperature Cycling

${\bf TCM}\,$  Temperature Control Module

${\bf TST}\,$  Thermal Shock Test

${\bf UART}~{\bf Universal}~{\bf Asynchronous}~{\bf Receiver-Transmitter}$

${\bf USB}\,$  Universal Serial Bus

**VDMOS** Vertical Diffused MOS

## Contents

| A             | bstra        | lct      | vii                                         |  |

|---------------|--------------|----------|---------------------------------------------|--|

| Ri            | Riassunto ix |          |                                             |  |

| A             | crony        | /ms      | xiii                                        |  |

| $\mathbf{Li}$ | st of        | figure   | s xxvi                                      |  |

| $\mathbf{Li}$ | st of        | tables   | xxviii                                      |  |

| In            | trod         | uction   | 1                                           |  |

| 1             | Pow          | ver Ser  | niconductor Devices 3                       |  |

|               | 1.1          | Electro  | onic Properties of Si and SiC               |  |

|               |              | 1.1.1    | Carrier Mobility Parameter                  |  |

|               |              | 1.1.2    | Impact Ionization                           |  |

|               | 1.2          | Struct   | ure of a Power MOSFET                       |  |

|               | 1.3          | Electr   | ic Characteristics of Power MOSFET 11       |  |

|               |              | 1.3.1    | Breakdown Voltage Parameter                 |  |

|               |              | 1.3.2    | Drain Leakage Current Parameter             |  |

|               |              | 1.3.3    | On-Resistance Parameter 18                  |  |

|               |              | 1.3.4    | Gate Leakage Current                        |  |

|               |              | 1.3.5    | Threshold Voltage Parameter                 |  |

|               | 1.4          | Noise    | in Semiconductor Devices                    |  |

|               |              | 1.4.1    | Power spectral density                      |  |

|               |              | 1.4.2    | High Frequency Noise                        |  |

|               |              | 1.4.3    | Low Frequency Noise                         |  |

| 2             | Reli         | iability | Testing on Power Devices 39                 |  |

|               | 2.1          | Why I    | Reliability on Power Semiconductor Devices? |  |

|               | 2.2          | Reliab   | ility Concepts                              |  |

|   |     | 2.2.1   | Failure Terms                                                          | . 41  |

|---|-----|---------|------------------------------------------------------------------------|-------|

|   |     | 2.2.2   | Acceleration Factor and Accelerated Test                               | . 43  |

|   | 2.3 | Reliat  | pility Methodologies Testing                                           | . 43  |

|   |     | 2.3.1   | Accelerated Life and Degradation Testing                               | . 43  |

|   |     | 2.3.2   | Highly Accelerated Life Testing                                        | . 44  |

|   |     | 2.3.3   | Highly Accelerated Stress Screening                                    | . 44  |

|   |     | 2.3.4   | Reliability Demonstration and Acceptance Tests                         | . 44  |

|   |     | 2.3.5   | Burn-In Test                                                           | . 45  |

|   | 2.4 | Accele  | erated Life Testing for Power Semiconductor Devices                    | . 45  |

|   | 2.5 | Electr  | ical Characterization of Power Devices                                 | . 45  |

|   |     | 2.5.1   | Drain to Source Leakage Current Measurement                            | . 47  |

|   |     | 2.5.2   | Drain to Source Breakdown Voltage Measurement                          | . 47  |

|   |     | 2.5.3   | Gate Leakage Current Measurement                                       | . 47  |

|   |     | 2.5.4   | Threshold Voltage Measurement                                          | . 48  |

|   |     | 2.5.5   | On-Resistance Measurement                                              | . 49  |

| 3 | Hig | h Tem   | perature Reverse Bias: Instrumentation Development                     | 55    |

|   | 3.1 |         | B standard technique                                                   |       |

|   | 3.2 |         | backs of HTRB Instrumentation and Standards                            |       |

|   |     | 3.2.1   | Thermal Runaway                                                        | . 59  |

|   |     | 3.2.2   | Uncertainties of Lifetime Estimation                                   |       |

|   | 3.3 | HTRE    | B Innovative Methodology                                               |       |

|   | 3.4 |         | ative HTRB Instrumentation                                             |       |

|   |     | 3.4.1   | Source Measurement Unit                                                |       |

|   |     | 3.4.2   | Switch Matrix Module                                                   | . 64  |

|   |     | 3.4.3   | Thermal Control Module                                                 | . 65  |

|   |     | 3.4.4   | Master Module Communications                                           | . 76  |

|   |     | 3.4.5   | Instrumentation Management Computer Application                        | . 76  |

| 4 | Hig | h Tem   | perature Reverse Bias: Experimentation                                 | 83    |

|   | 4.1 |         | nal Stabilization Time                                                 | . 85  |

|   | 4.2 | Temp    | erature Extrapolation in TCMs                                          | . 86  |

|   | 4.3 | Exper   | iment 1: Thermal Runaway Control                                       | . 87  |

|   | 4.4 | Exper   | iment 2:HTRB on 650<br>V $MDmesh^{TM}\text{-}V$ Power Si n-MOSFET<br>s | . 89  |

|   | 4.5 | Exper   | iment 3: HTRB on 650V Super Junction Power Si n-MOSFETs                | . 92  |

|   | 4.6 | Exper   | iment 4: HTRB on $MDmesh^{TM}$ 550V Power Si n-MOSFETs                 | . 95  |

|   | 4.7 | Exper   | iment 5: HTRB on 1200V Power SiC n-MOSFETs                             | . 99  |

|   | 4.8 | Exper   | iment 6: Si and SiC Drain Leakage Current Comparison                   | . 106 |

| 5 | Low | /-Frequ | uency Noise Characterization                                           | 111   |

|   | 5.1 | Metho   | $\operatorname{pdology}$                                               | . 112 |

|   | 5.2 | Instru  | mentation                                                              | . 113 |

|   | 5.3 | Exper   | imentation                                                             |       |

|   |     | 5.3.1   | Thermal Noise Measurement on SMD Resistor                              | . 116 |

|             | 1/f Noise Measurement on Power n-MOSFETs |     |

|-------------|------------------------------------------|-----|

| Conclusions |                                          | 129 |

| Appendices  |                                          | 135 |

|             |                                          |     |

A Flowcharts Implemented in the Firmware of the HTRB Instrumentation 135

# List of Figures

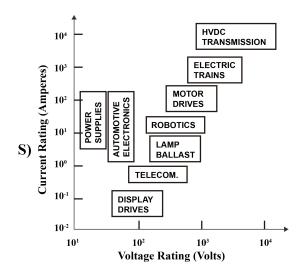

| 1.1  | Classification for power devices according to voltage and current ratings                                                                                                                                                    | 4  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

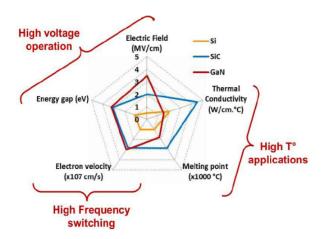

| 1.2  | Application fields of WBG materials (SiC and GaN) vs Si [8]                                                                                                                                                                  | 7  |

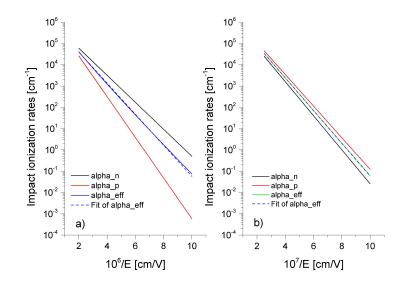

| 1.3  | Numerical simulation of impact ionization rates for electron (black lines) and holes (red lines) in a) Si and b) 4H-SiC. Effective ionization rates (blue                                                                    |    |

|      | lines) are also presented. Electric Field is ranging in 0.1-0.5 $MV.cm^{-1}$ and                                                                                                                                             |    |

|      | 1-4 $MV.cm^{-1}$ for Si and 4H-SiC, respectively                                                                                                                                                                             | 9  |

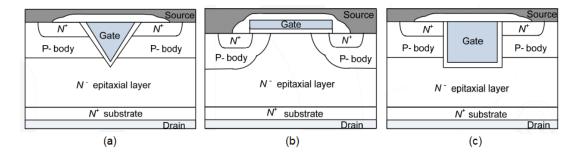

| 1.4  | Types of vertical structures for modern enhanced power MOSFET [23]. $\ $ .                                                                                                                                                   | 10 |

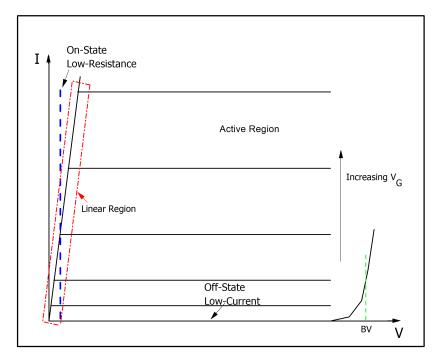

| 1.5  | Analytical trans-characteristic curves of a typical enhanced n-channel                                                                                                                                                       |    |

|      | MOSFET transistor.                                                                                                                                                                                                           | 11 |

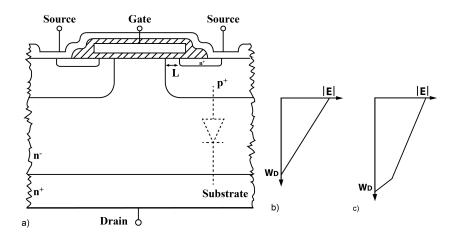

| 1.6  | a) DMOSFET cell structure of a Power n-MOSFET (PiN diode is purposely highlighted). b) Triangular shape distribution of Electric Field $(E)$ named Non-Punch-Through (NPT). c) Trapezoidal shape distribution of             |    |

|      | of the space charge named Punch-Through (PT)                                                                                                                                                                                 | 12 |

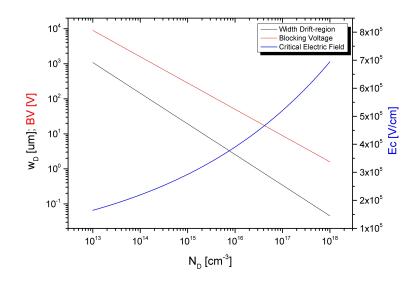

| 1.7  | Critical electric field strength $(E_C)$ , breakdown voltage $(BV)$ and de-                                                                                                                                                  | 14 |

| 1.1  | pletion width $(w_D)$ at breakdown as function of doping density $N_D$ for                                                                                                                                                   |    |

|      | $p^+$ n-junction in Si at 300K                                                                                                                                                                                               | 14 |

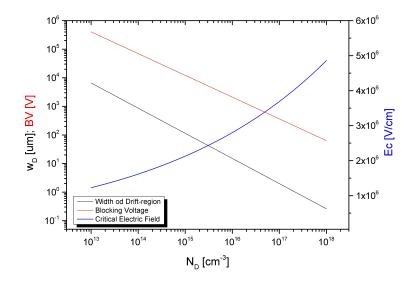

| 1.8  | Critical electric field strength $(E_C)$ , breakdown voltage $(BV)$ and de-                                                                                                                                                  |    |

| 1.0  | pletion width $(w_D)$ at breakdown as function of doping density $N_D$ for                                                                                                                                                   |    |

|      | $p^+$ n-junction in SiC at 300K                                                                                                                                                                                              | 15 |

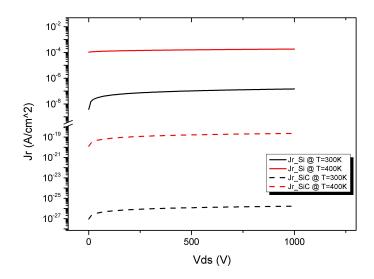

| 1.9  | Simulation results of $j_r$ in function of $V_{DS}$ for a Si (solid-lines) and SiC (dash-lines) of an n-MOSFET designed for BV=1 kV. Simulations performed at 300K (black-lines) and 400K (red-lines). Avalanche multiplica- | -  |

|      | tion effect during the breakdown was not considered                                                                                                                                                                          | 18 |

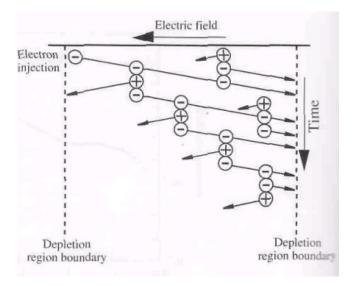

| 1.10 | Band diagram's example of the interaction of electron-hole generation by                                                                                                                                                     |    |

|      | impact ionization in the depletion zone during avalanche multiplication<br>under the effect of a strong electric field                                                                                                       | 19 |

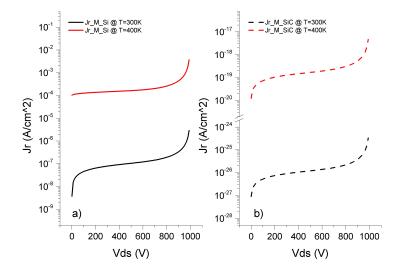

| 1.11 |                                                                                                                                                                                                                              |    |

|      | breakdown was considered.                                                                                                                                                                                                    | 19 |

|      |                                                                                                                                                                                                                              |    |

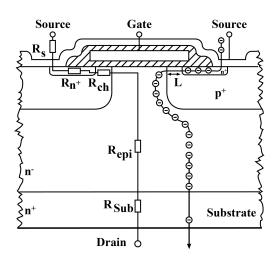

| 1.12                                                                                                  | Representation of current path and resistance contribution of different sections in a standard vertical MOSFET.                                                                                                                  | 20                               |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

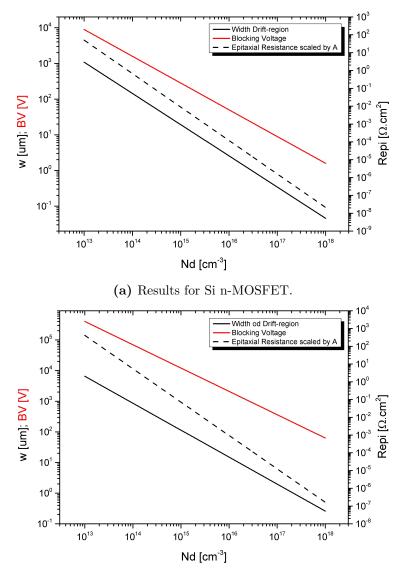

| 1.13                                                                                                  | Numerical calculation of Epitaxial Resistance $(R_{epi})$ scaled by the active area (A) of a power MOSFET in function of $N_D$ . For comparison purpose, the results simulation for $w_D$ and $BV$ are also plotted. Simulations |                                  |

|                                                                                                       | pose, the results simulation for $w_D$ and $D_V$ are also plotted. Simulations performed at 300K.                                                                                                                                | 21                               |

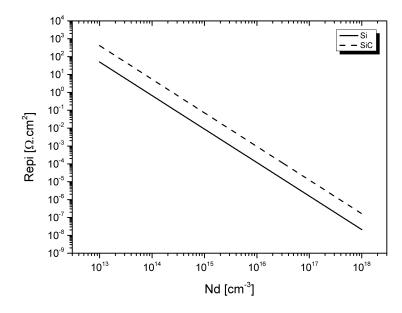

| 1.14                                                                                                  | Comparison of $R_{epi}$ , scaled by the active area A, obtained from numerical simulation for a Si and 4H-SiC vertical power MOSFET in function of $N_D$ .                                                                       | 22                               |

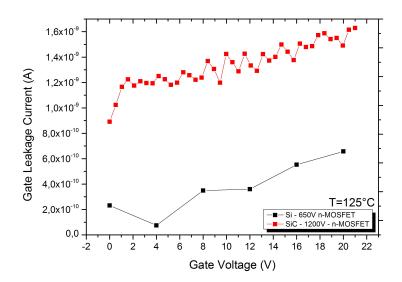

|                                                                                                       | Comparison of gate leakage current measured on a 650V Si and a 1200V SiC n-MOSFET devices at 125°C.                                                                                                                              | 23                               |

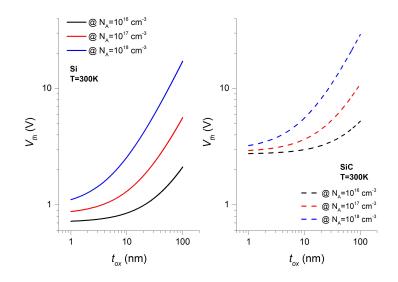

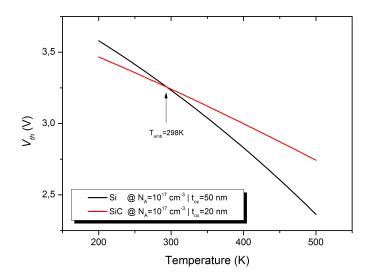

|                                                                                                       | Threshold voltage simulation as function of oxide thickness $t_{ox}$ for different acceptor doping densities $N_A$ for Si and SiC n-channel MOSFETs                                                                              | 25                               |

| 1.17                                                                                                  | Threshold voltage simulation as function of temperature for Si and SiC n-<br>channel MOSFETs. Parameters calculation of both devices were selected                                                                               | 0.0                              |

| 1 10                                                                                                  | to have a similar $V_{th}$ at room temperature.                                                                                                                                                                                  | 26<br>27                         |

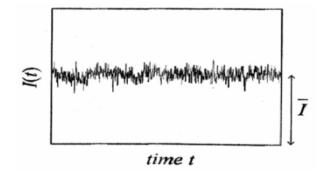

|                                                                                                       | Typical electronic signal noisy [47]                                                                                                                                                                                             | $\frac{21}{28}$                  |

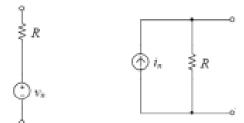

|                                                                                                       | Circuital models of the thermal voltage and current noise.                                                                                                                                                                       | 20<br>29                         |

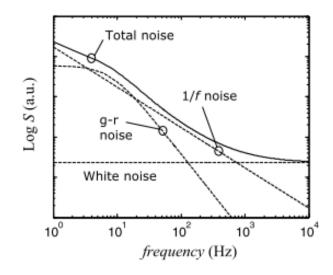

| 1.20                                                                                                  |                                                                                                                                                                                                                                  | -0                               |

|                                                                                                       | from [47]                                                                                                                                                                                                                        | 32                               |

|                                                                                                       |                                                                                                                                                                                                                                  |                                  |

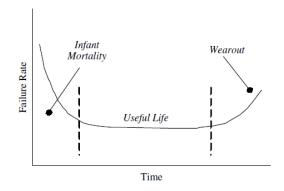

| 2.1                                                                                                   | Typical bathtub curve of the failure rate in function of time.                                                                                                                                                                   | 42                               |

| $2.1 \\ 2.2$                                                                                          | Typical bathtub curve of the failure rate in function of time Test circuit for drain to source leakage current $(I_{DSS})$ measurement in Power n-MOSFETs                                                                        | 42<br>47                         |

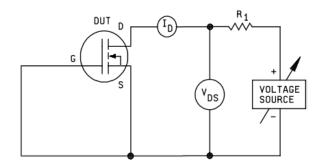

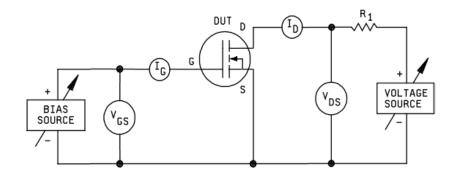

|                                                                                                       | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in                                                                                                                                                      |                                  |

| 2.2                                                                                                   | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47                               |

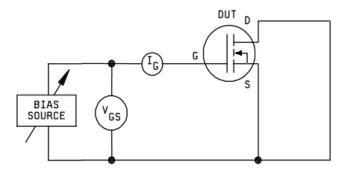

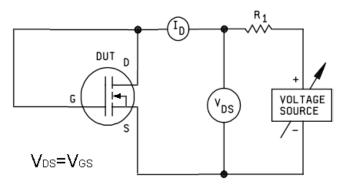

| 2.2<br>2.3                                                                                            | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48                         |

| <ul><li>2.2</li><li>2.3</li><li>2.4</li></ul>                                                         | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48<br>50                   |

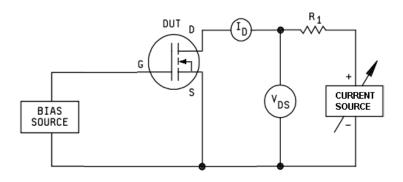

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> </ol>                                        | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48<br>50<br>50             |

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> </ol>                           | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48<br>50<br>50<br>51       |

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>3.1</li> </ol>              | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48<br>50<br>50<br>51<br>57 |

| <ol> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>3.1</li> <li>3.2</li> </ol> | Test circuit for drain to source leakage current $(I_{DSS})$ measurement in<br>Power n-MOSFETs                                                                                                                                   | 47<br>48<br>50<br>51<br>57<br>59 |

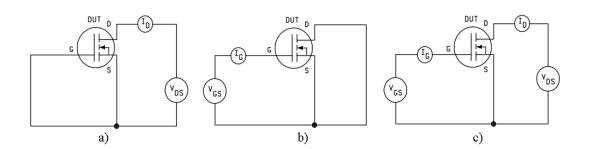

| 3.6  | Circuital schematics used for measuring: a) Drain Leakage Current $(I_{DSS})$<br>& Breakdown Voltage $(BV_{DSS})$ , b) Gate Leakage Current $(I_{GSS})$ and c)                                            |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | Threshold Voltage $(V_{th})$ . Such measurements are performed during the Electric Characterization Tests (ECTs), Electric Verification Test (EVTs)                                                       |     |

|      | and Emergency Characterization Test (EECTs) operations.                                                                                                                                                   | 64  |

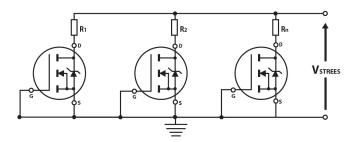

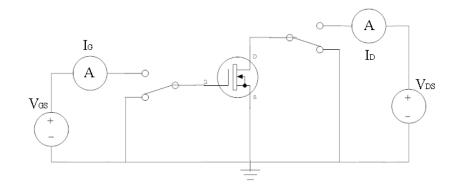

| 3.7  | Circuital schematic of the system exploited for switching electrical inter-<br>connections during the ECTs, EVTs, EECTs, HTRB and HTGB tests:                                                             | CF. |

| 3.8  | two-relays per every Device Under Test (DUT) have been used Alternative circuit schematic for the HTRB with the proposed instrumen-                                                                       | 65  |

| 2.0  | tation                                                                                                                                                                                                    | 65  |

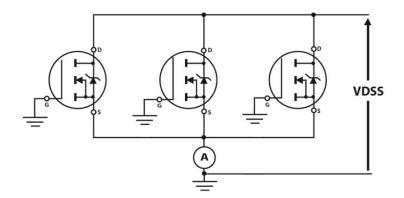

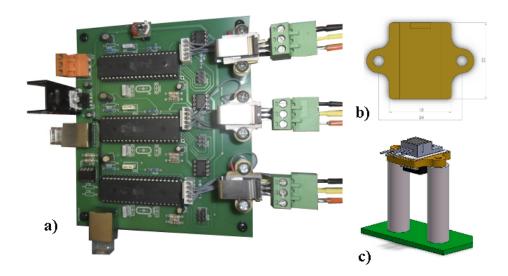

| 3.9  | Cable connection and c) Prototype Board of the SMM                                                                                                                                                        | 66  |

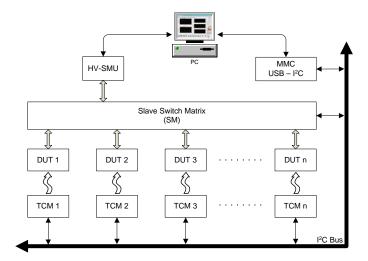

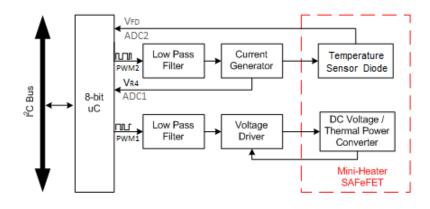

| 3.10 | Block diagram of a single Thermal Control Module (TCM) developed for<br>individually controlling the temperature of each DUT.                                                                             | 66  |

| 3.11 | Thermal Control Module (TCM) physical implementation. a) First PCB prototype with 3 TCMs. b) Bottom view of the Brass-Sinker designed for the SAFeFET (Surface Added Featured Metal Oxide Semiconductor)- |     |

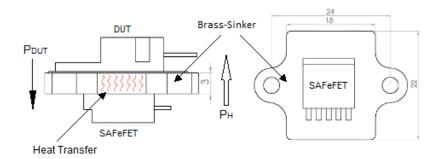

|      | DUT placing. c) 3D view of the SAFeFET and DUT disposal.                                                                                                                                                  | 67  |

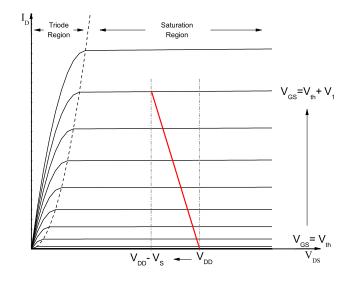

| 3.12 | Symbolic I-V characteristic of the SAFeFET working for heating genera-<br>tion into the TCM (red line).                                                                                                   | 68  |

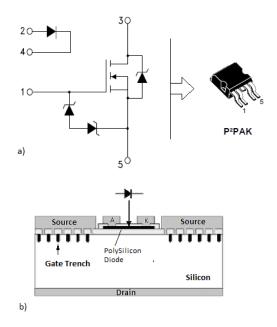

| 3.13 | a) Electrical schematic of SAFeFET and the $P^2PAK$ package. b) Cross-<br>section view of the SAFeFET cell structure.                                                                                     | 68  |

| 3.14 | Electronic circuit schematic for heating generation using SAFeFET.                                                                                                                                        | 70  |

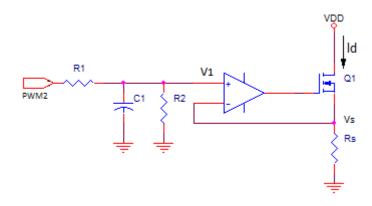

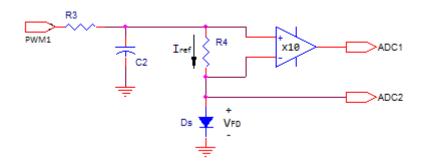

|      | Electronic circuit schematic for temperature sensing using the internal SAFeFET Sensing Diode $(D_s)$ .                                                                                                   | 71  |

| 3.16 | Block schematic of a Proportional Integrative Derivative (PID) controller<br>for analogue signals.                                                                                                        | 73  |

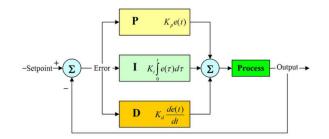

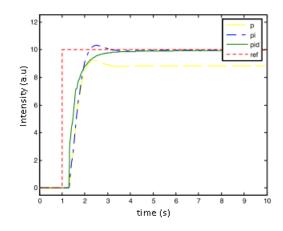

| 3.17 | Typical PID regulator responses for step change in reference input from                                                                                                                                   |     |

| 9 10 | $\begin{bmatrix} 23 \end{bmatrix} \dots $                                                           | 74  |

| 3.18 | Schematic of the physical disposal of the SAFeFET (heater) and DUT on<br>a Brass-Sinker sample holder.                                                                                                    | 75  |

| 3 10 | View of the Master Communication Module (MCM) prototype board im-                                                                                                                                         | 10  |

| 0.19 | plementation.                                                                                                                                                                                             | 77  |

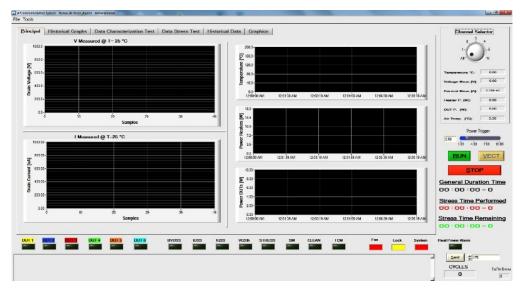

| 3.20 | Screen capture of the control application Graphical User Interface (GUI).                                                                                                                                 | 77  |

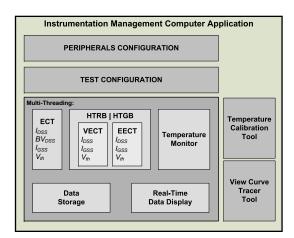

| 3.21 | Block diagram of the software application for the HTRB instrumentation.                                                                                                                                   | 78  |

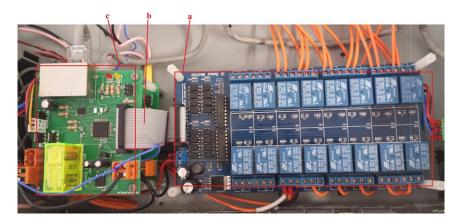

| 4.1  | First prototype of the innovative HTRB instrumentation implemented with SAFeFETs to test 6 DUTs. Maximum temperature of test 175 $^{\circ}$ C.                                                            | 84  |

| 4.2  | Second prototype of the innovative HTRB instrumentation implemented<br>with SiC power MOSFETs to test 6 DUTs. Maximum temperature of test                                                                 |     |

|      | 200 °C.                                                                                                                                                                                                   | 84  |

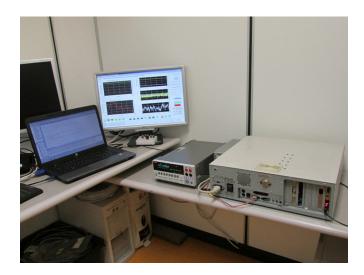

| 4.3  | Innovative HTRB instrumentation setup.                                                                                                                                                                    | 85  |

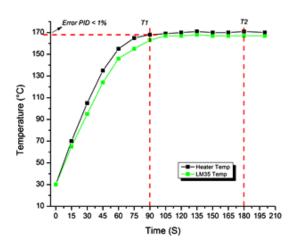

| 4.4  | Comparison between temperatures measured from SAFeFET sensing diode<br>Ds (Heater Temperature) and external sensor (LM35DT Temperature).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 86   |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

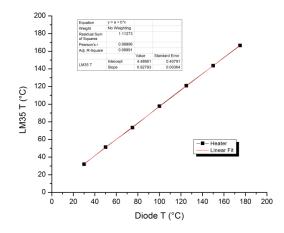

| 4.5  | Linear Fitting of temperature measured on SAFeFET sensing diode (val-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|      | ues in X-axis) and external sensor (LM35DT for Y-axis)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 87   |

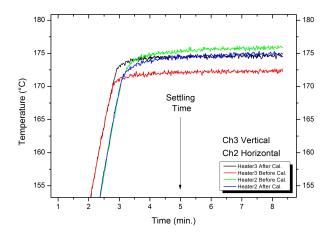

| 4.6  | Measured temperature trends vs. time, of two different heater disposal,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|      | before and after the temperature calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87   |

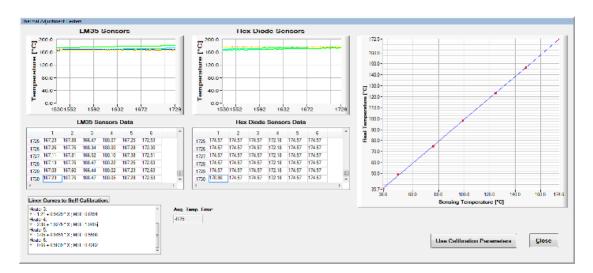

| 4.7  | GUI of the Thermal Adjustment Tool (TAT) developed to automatize the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|      | $T_{dut}$ calibration procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88   |

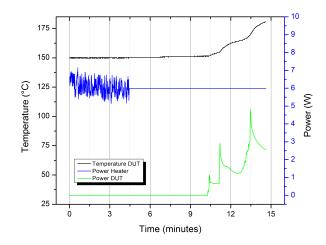

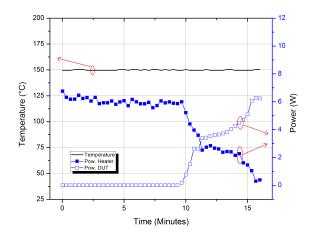

| 4.8  | Detection and control of thermal runaway effect, over a DUT power tran-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

|      | sistor, performed by the TCM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88   |

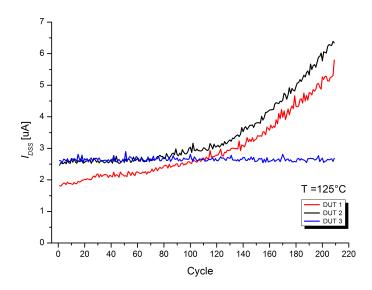

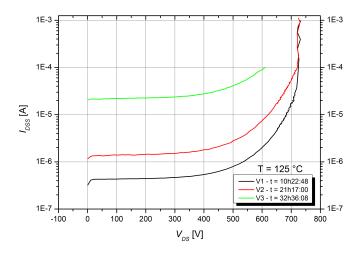

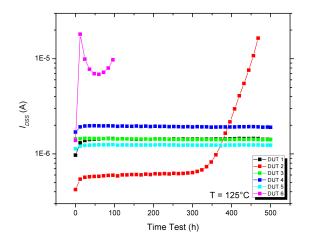

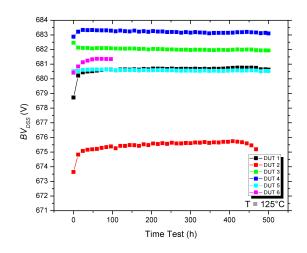

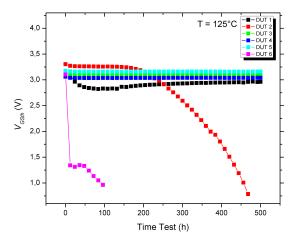

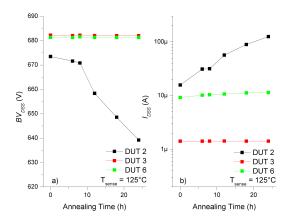

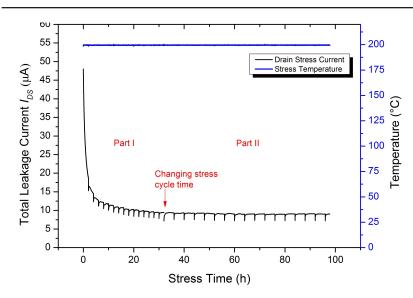

| 4.9  | $I_{DSS}$ data measured via interim ECT along stress test on DUTs at $V_{DS} = 650V$ and $T_{DUT} = 125^{\circ}C$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91   |

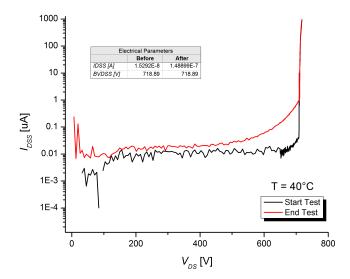

| 4.10 | Comparison between $I_{DSS}$ curves measured before and after the stress test on DUT1 (power n-MOSFET).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 91   |

| 4.11 | Comparison of $I_{DSS}$ trends of two different p-MOSFET DUTs stressed continuously (blue line) and by cycle (black line).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 92   |

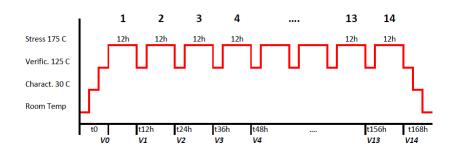

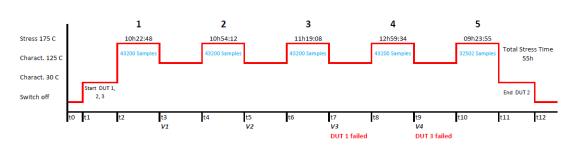

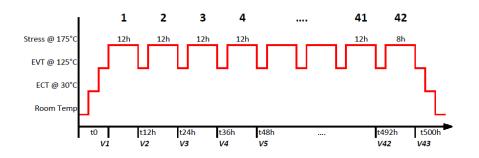

| 4.12 | Scheduled cycles approach for advanced HTRB test run 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 93   |

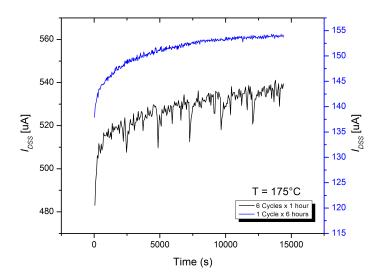

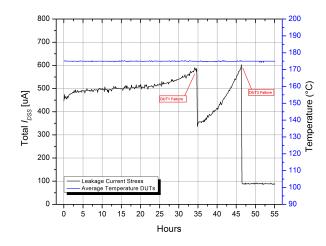

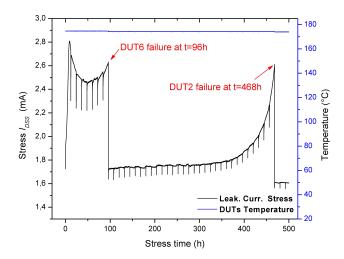

| 4.13 | Total $I_{DSS}$ trend at T=175°C measured on the DUTs during the test run 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 94 |

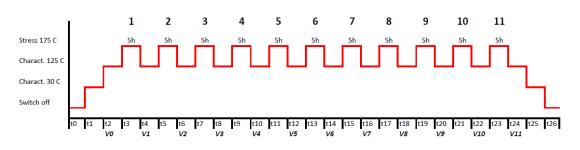

| 4.14 | Scheduled cycles approach for advanced HTRB test run 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 94   |

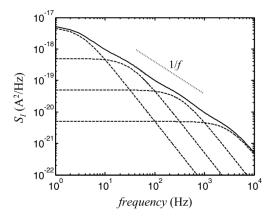

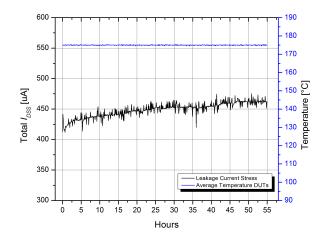

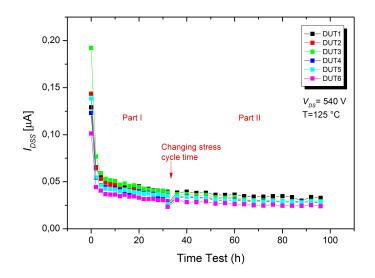

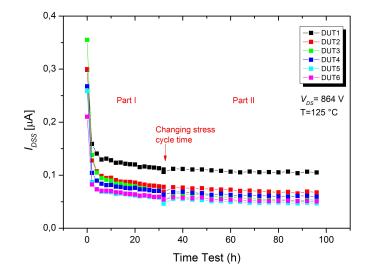

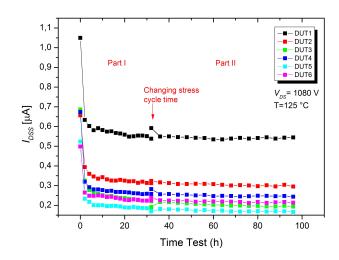

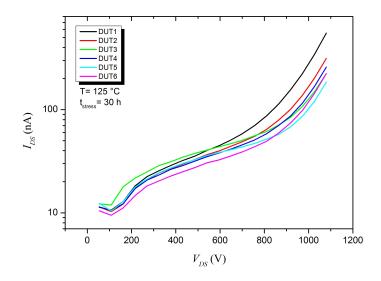

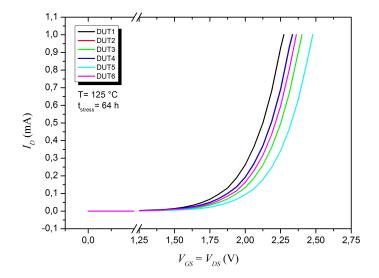

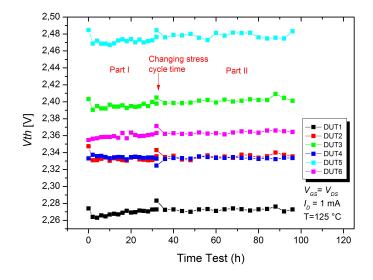

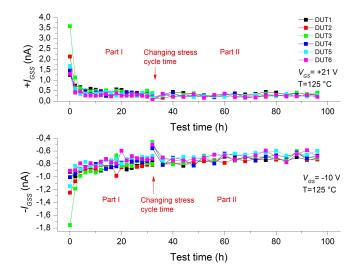

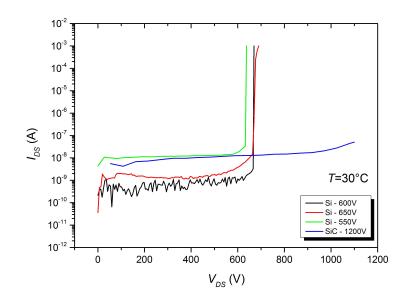

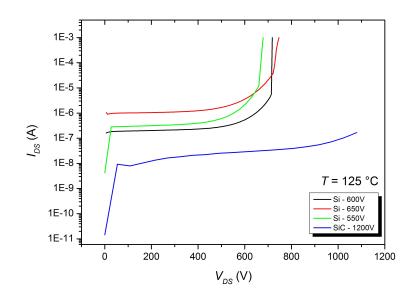

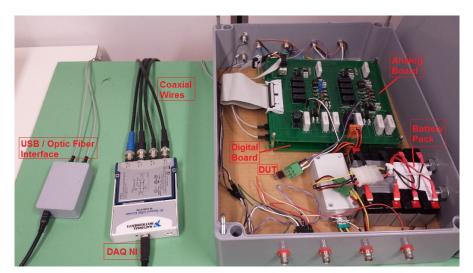

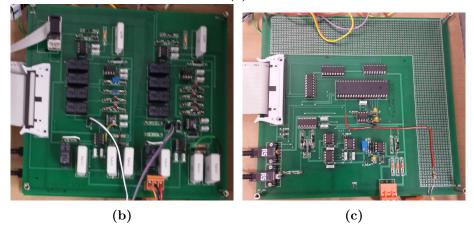

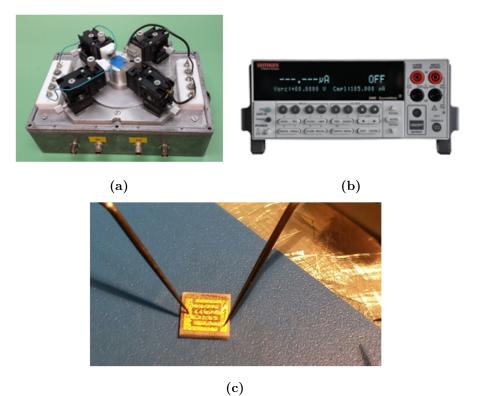

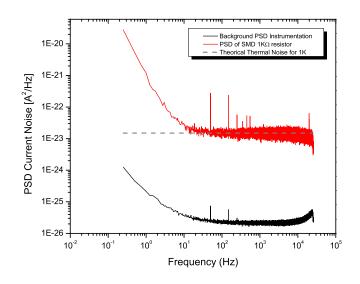

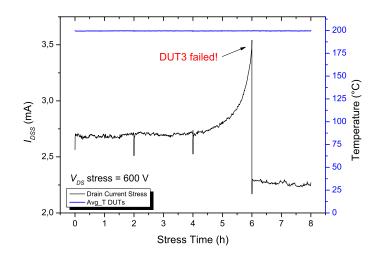

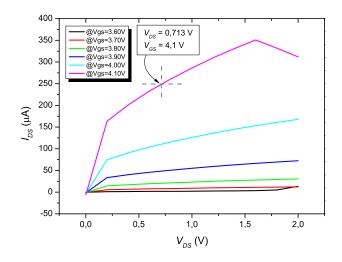

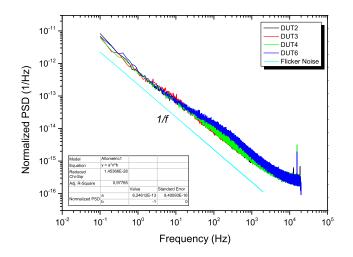

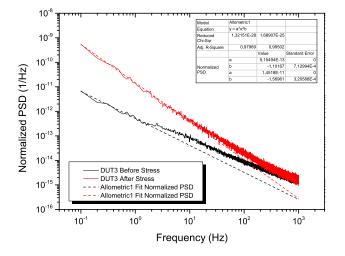

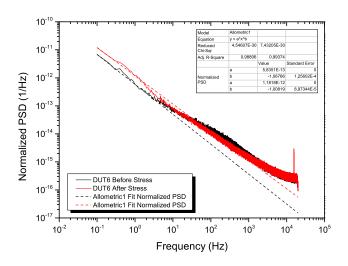

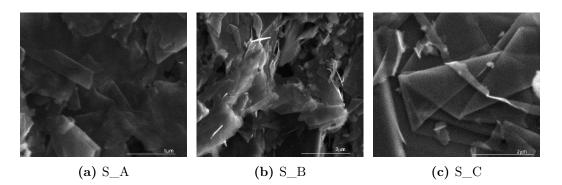

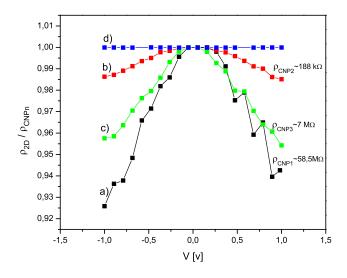

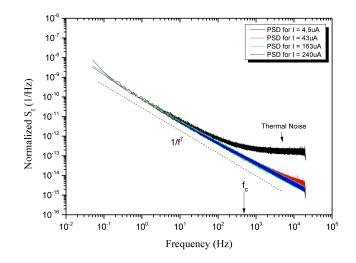

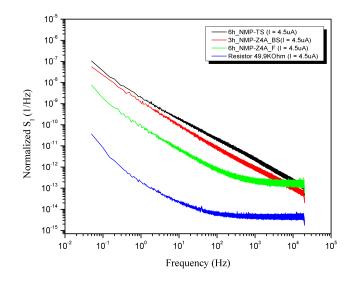

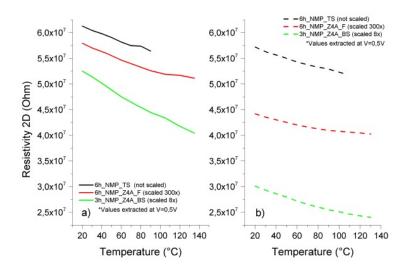

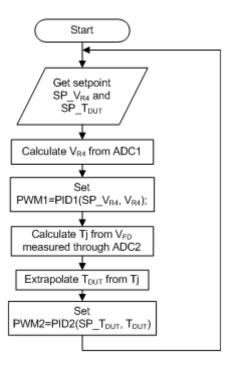

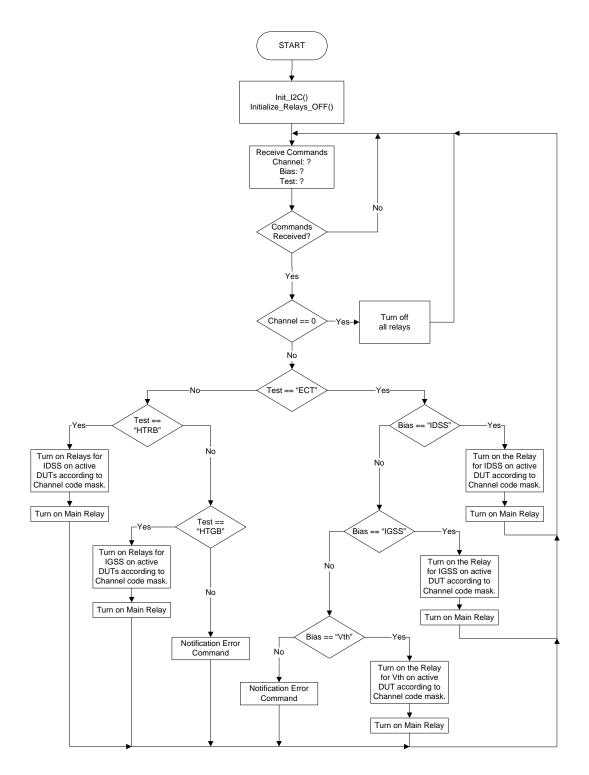

|      | Total $I_{DSS}$ trend at T=175°C measured on the DUTs during the test run 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |