#### UNIVERSITA' DELLA CALABRIA

#### Dipartimento di Fisica

#### Scuola di Dottorato

di Scienza e Tecnica BERNARDINO TELESIO Con il contributo del CERN

#### CICLO

XXVIII

#### **TITOLO TESI**

High-Repeatable Data Acquisition Systems for Pulsed Power Converters in Particle Accelerator Structures

#### Settore Scientifico Disciplinare ICAR/08

| Direttore:   | Ch.mo Prof. Roberto Bartolino |

|--------------|-------------------------------|

| Directore.   |                               |

| Supervisore: | Ch.mo Prof. Raffaele Zinno    |

|              | Ch.mo Prof. Pasquale Arpaia   |

| Tutor:       | Ph.D. Michele Martino         |

|              | / /                           |

Dottorando: Dott. Carlo Baccigalupi

### Summary

In this Ph.D. thesis, the issues related to the metrological characterization of high-performance pulsed power converters are addressed.

Initially, a background and a state of the art on the measurement systems needed to correctly operate a high-performance power converter are presented. As a matter of fact, power converters usually exploits digital control loops to enhance their performance. In this context the final performance of a power converter has to be validated by a reference instrument with higher metrological characteristics. In addition, an on-line measurement system is also needed to digitize the quantity to be controlled with high accuracy.

Then, in industrial applications of power converters metrology, specifications are given in terms of Worst-Case Uncertainty (WCU). Therefore, an analytical model for predicting the Worst-Case Uncertainty (*WCU*) of a measurement system is discussed and detailed for an instrument affected by Gaussian noise. Furthermore, the study and the design of a *Reference Acquisition System* for characterizing the high-power pulses of the klystron modulators of the Compact LInear Collider (*CLIC*), a new linear accelerator under study at CERN, is presented.

The Thesis continues with the numerical results obtained in simulation for the three main topics (Worst-Case Uncertainty, Reference Acquisition System, On-line Acquisition System) to demonstrate the effectiveness of the proposals.

Finally, the experimental results of a case study in the framework of the above-mentioned CLIC accelerator are reported and compared with the simulations in order to obtain the final validation of the proposals. In particular, CLIC main requirements for the measurement systems mostly concern their level of repeatability which was proven to be only affected by the instrumental noise under certain assumptions. Thus, the two systems were designed to be ultra-low noise solutions and, in turn, they are demonstrated to be repeatable in the order of few tens of parts per million (*ppm*).

### Acknowledgements

I would like to express my sincere gratitude to my university supervisors. Professor Pasquale Arpaia for sharing his experience and fundamental knowledge with me. Professors Raffaele Zinno and Domenico Grimaldi for their patience and support.

I am deeply grateful to my CERN supervisor, Ph.D. Michele Martino for his excellent guidance. His constant presence was a fundamental incitement to improve my professional competencies.

My sincere thanks also go to Ph.D. Miguel Cerqueira Bastos and the Electrical Power Converters group at CERN for offering me the opportunity to work in such an interesting and challenging project. Being surrounded by exceptional and helpful colleagues represented an incredible mine to draw upon.

I would like to thank Francesca for standing by me every time I need. Sharing with you this bitter sweet life is my biggest success.

I would also like to thank my family. They were always supporting me and encouraging me with unconditional love.

Finally, I thank all my friends. One of the greatest gifts of life is friendship, and I have received it.

Geneva, November 25<sup>th</sup> 2015

С. В.

### Contents

| Su | ımma    | ary                                      |      |

|----|---------|------------------------------------------|------|

| Ac | knov    | vledgements                              | i    |

| Li | st of f | figures                                  | vii  |

| Li | stof    | tables                                   | xi   |

| Sy | mbo     | ls and Acronyms                          | xiii |

| In | trodu   | uction                                   | 1    |

| PA | RT 1    | - BACKGROUND AND STATE OF THE ART        | 3    |

|    | Bac     | kground                                  | 4    |

|    | Stat    | e of the Art                             | 7    |

| PA | ART 2   | - PROPOSAL                               | 9    |

| 1  | The     | Worst-Case Uncertainty Analytical Model  | 11   |

|    | 1.1     | Overview                                 | 11   |

|    | 1.2     | Worst-Case Uncertainty Theoretical Model | 11   |

|    |         | 1.2.1 Worst-Cacse Uncertainty Definition | 12   |

|    |         | 1.2.2 Analytical Model                   | 15   |

| 2  | The     | Reference Acquisition System             | 17   |

|    | 2.1     | Overview                                 | 17   |

|    | 2.2     | Requirements for CLIC                    | 17   |

|    |         | 2.2.1 Pulse-to-Pulse Repeatability       | 18   |

|    |         | 2.2.2 The Acquisition System             | 18   |

|    | 2.3     | Analogue Front-End                       | 20   |

|    |         | 2.3.1 Basic Ideas                        | 20   |

|    |         | 2.3.2 Concept Design                     | 21   |

|    |         | 2.3.3 Physical Design                    | 21   |

|    | 2.4     | Design Enhancement                       | 23   |

| 3  | The        | On-line Acquisition System                                                   | 25 |

|----|------------|------------------------------------------------------------------------------|----|

|    | 3.1        | Overview                                                                     | 25 |

|    | 3.2        | Requirements for CLIC                                                        | 25 |

|    |            | 3.2.1 Measurand                                                              | 26 |

|    |            | 3.2.2 Repeatability                                                          | 26 |

|    |            | 3.2.3 Throughput and Bandwidth                                               | 27 |

|    |            | 3.2.4 Delay                                                                  | 27 |

|    | 3.3        | Design                                                                       | 28 |

|    |            | 3.3.1 Basic Principle                                                        | 28 |

|    |            | 3.3.2 Full-Signal Reconstruction                                             | 29 |

|    |            | 3.3.3 Sampling and Filtering Strategy                                        | 29 |

|    |            | 3.3.4 ADC Noise vs Analogue Noise                                            | 30 |

|    | 3.4        | Physical Design of the Analogue Front-End                                    | 32 |

|    |            | 3.4.1 Input Stage                                                            | 32 |

|    |            | 3.4.2 Clipping Stage                                                         | 33 |

|    |            | 3.4.3 Differential Stage                                                     | 33 |

|    |            | 3.4.4 Output Stage                                                           | 33 |

| PA | RT 3       | - NUMERICAL RESULTS                                                          | 35 |

|    | <b>m</b> 1 |                                                                              | 07 |

| 4  |            | Worst-Case Uncertainty Analytical Model                                      | 37 |

|    | 4.1        | Repeatability Case Study at CERN         A La Nation Standard Deviation      | 37 |

|    |            | 4.1.1       Noise Standard Deviation         4.1.2       Number of Community | 38 |

|    |            | 4.1.2 Number of Samples                                                      | 39 |

|    |            | 4.1.3 Number of Observations                                                 | 39 |

|    | 4.2        | Numerical Results                                                            | 39 |

|    |            | 4.2.1 Model Goodness                                                         | 39 |

|    |            | 4.2.2 Model Characterization                                                 | 41 |

| 5  | The        | Reference Acquisition System                                                 | 43 |

|    | 5.1        | Amplitude Frequency Response                                                 | 43 |

|    | 5.2        | Noise Analysis                                                               | 43 |

|    | 5.3        | Linearity                                                                    | 44 |

|    | 5.4        | Settling Time                                                                | 45 |

| 6  | The        | On-line Acquisition System                                                   | 47 |

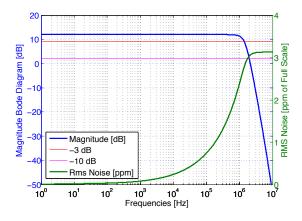

|    | 6.1        | Noise and Bandwidth                                                          | 47 |

|    | 6.2        | Delay                                                                        | 48 |

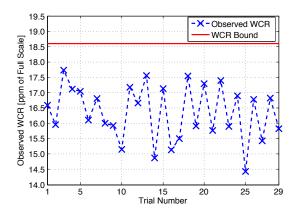

|    |            | Worst-Case Repeatability                                                     | 48 |

| PA | ART 4      | - EXPERIMENTAL RESULTS                                                       | 51 |

| 7  | The Worst-Case Uncertainty Analytical Model                                      | 53 |

|----|----------------------------------------------------------------------------------|----|

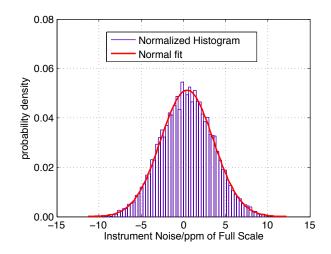

|    | 7.0.1 Additive White Gaussian Noise                                              | 53 |

|    | 7.0.2 WCR Prediction                                                             | 54 |

| 8  | The Reference Acquisition System: Proof of Principle                             | 57 |

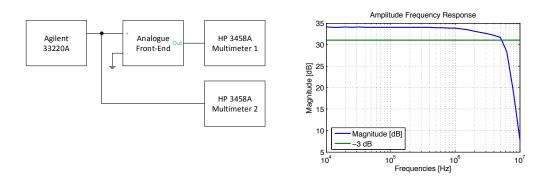

|    | 8.0.1 Amplitude Frequency Response                                               | 57 |

|    | 8.0.2 Noise Analysis                                                             | 58 |

|    | 8.0.3 Linearity                                                                  | 58 |

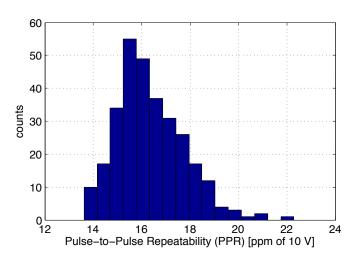

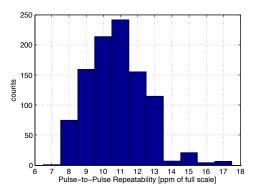

|    | 8.0.4 Repeatability Results                                                      | 58 |

|    | 8.0.5 Differential Sensing Circuit                                               | 61 |

| 9  | The Reference Acquisition System: Metrological Characterization                  | 63 |

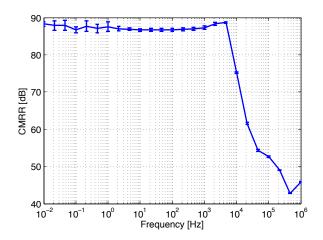

|    | 9.1 CMRR Measurement                                                             | 63 |

|    | 9.1.1 Common-Mode Input Voltage Rejection                                        | 63 |

|    | 9.1.2 Common Mode Ground Voltage Rejection                                       | 65 |

|    | 9.2 Offset Drift                                                                 | 68 |

|    | 9.2.1 Offset in Nominal Conditions                                               | 68 |

|    | 9.2.2 Slow Temperature Variation                                                 | 69 |

|    | 9.2.3 Fast Temperature Variation                                                 | 70 |

|    | 9.2.4 Humidity Response                                                          | 70 |

|    | 9.3 Worst-Case Repeatability                                                     | 72 |

|    | 9.3.1 Short Circuit                                                              | 72 |

|    | 9.3.2 10 <i>V</i> <sub>DC</sub> Common Mode                                      | 72 |

|    | 9.3.3 Distribution Mode vs Common Mode Input Voltage                             | 73 |

| 10 | ) The On-line Acquisition System                                                 | 75 |

|    | 10.1 Noise Test                                                                  | 75 |

|    | 10.2 Bandwidth Test                                                              | 76 |

|    | 10.3 Delay Test                                                                  | 77 |

|    | 10.4 DC CMRR Test                                                                | 78 |

|    | 10.5 AC CMRR Test                                                                | 79 |

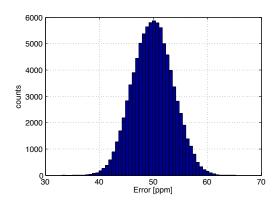

|    | 10.6 Full-Signal Acquisition and Pulse-to-Pulse Repeatability Test               | 81 |

| Co | onclusions                                                                       | 85 |

| A  | APPENDIX: Rigorous Formula for WCU Distribution                                  | 87 |

|    | A.0.1 WCU for a Given Sample Size with Gaussian Noise                            | 87 |

|    | A.0.2 Dominant Approximation of <i>WCU</i> for a Given Sample Size with Gaussian |    |

|    | Noise                                                                            | 89 |

# List of Figures

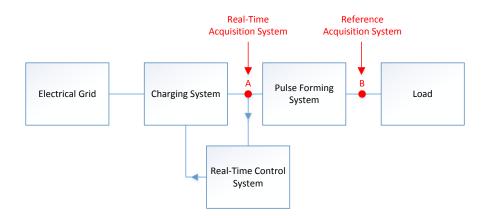

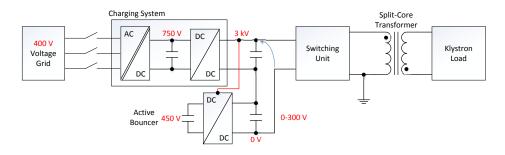

| 1   | Typical Topology of a Pulsed Power Converter.                                                            | 1  |

|-----|----------------------------------------------------------------------------------------------------------|----|

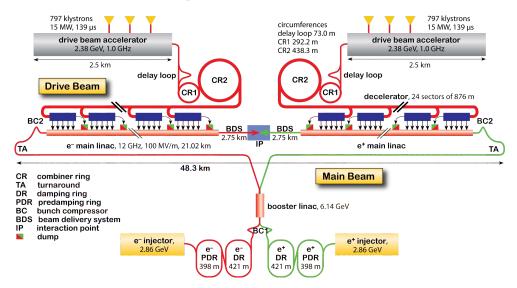

| 2   | CLIC Layout at 3 <i>TeV</i>                                                                              | 4  |

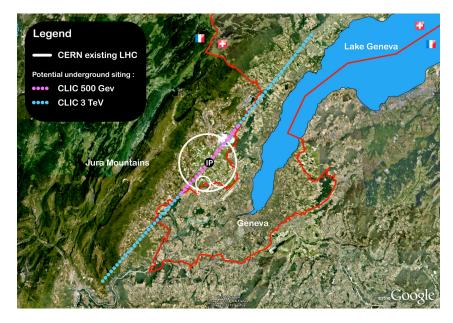

| 3   | Map showing a potential location for the CLIC accelerator complex $\ldots$ .                             | 5  |

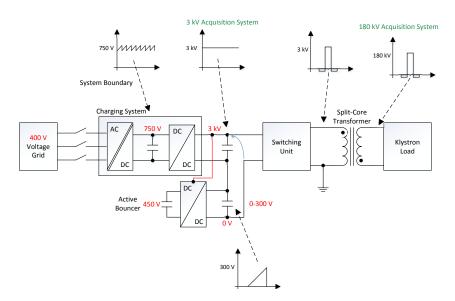

| 4   | Topology of the CLIC Klystron Modulator.                                                                 | 6  |

| 1.1 | Worst-Case Uncertainty Definition ( $t_s$ : sampling period, T: signal period)                           | 13 |

| 2.1 | Pulse Parameters Definition.                                                                             | 18 |

| 2.2 | Pulse-to-Pulse Repeatability Definition.                                                                 | 19 |

| 2.3 | Reference Measurement System - Common Ground Is Represented In Order To                                  |    |

|     | Simplify The Diagram.                                                                                    | 20 |

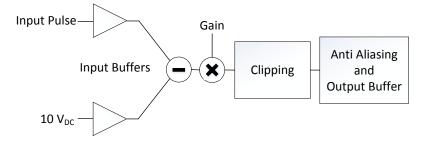

| 2.4 | Analogue Front-End Block Diagram                                                                         | 20 |

| 2.5 | Analogue Front-End Schematic.                                                                            | 22 |

| 2.6 | The Enhanced Analogue Front-End                                                                          | 23 |

| 3.1 | Topology of the High-Voltage Modulator under design at ETH Zurich $\ldots$ .                             | 26 |

| 3.2 | Switching Unit Input Voltage                                                                             | 27 |

| 3.3 | Pulse-to-Pulse Repeatability Definition                                                                  | 27 |

| 3.4 | Definition of Delay in a Power Converter Real-time Data Acquisition                                      | 28 |

| 3.5 | Measurement System Block Diagram                                                                         | 28 |

| 3.6 | Frequency Response of the Average $4^{th}$ FIR filter $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 30 |

| 3.7 | Analogue Front-End Schematics                                                                            | 32 |

| 4.1 | Reference Acquisition System Block Diagram.                                                              | 38 |

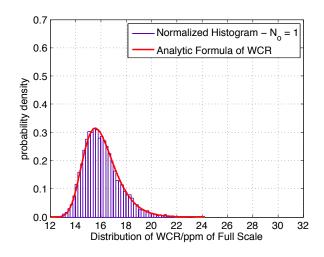

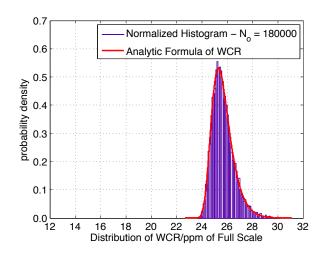

| 4.2 | Distribution of <i>WCR</i> for $N_o = 1$ and $N_{test} = 10,000$                                         | 40 |

| 4.3 | Distribution of <i>WCR</i> for $N_o = 180,000$ and $N_{test} = 10,000$                                   | 41 |

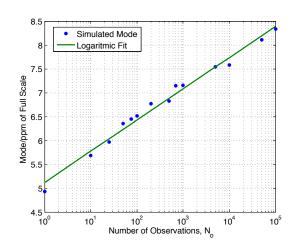

| 4.4 | Mode of <i>WCR</i> versus $N_o$ , $\sigma = 1$ ppm of Full Scale                                         | 41 |

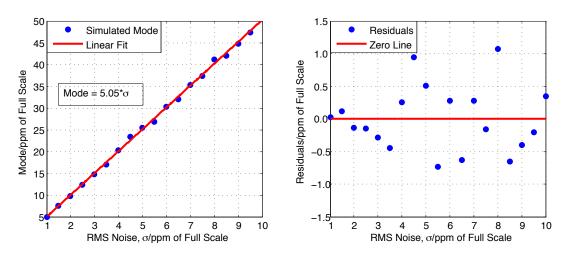

| 4.5 | Mode of <i>WCR</i> versus $\sigma$ (left), Residuals of Linear Fit (right). $N_o = 1. \ldots \ldots$     | 42 |

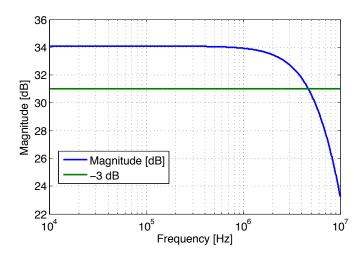

| 5.1 | Simulated Amplitude Frquency Response.                                                                   | 44 |

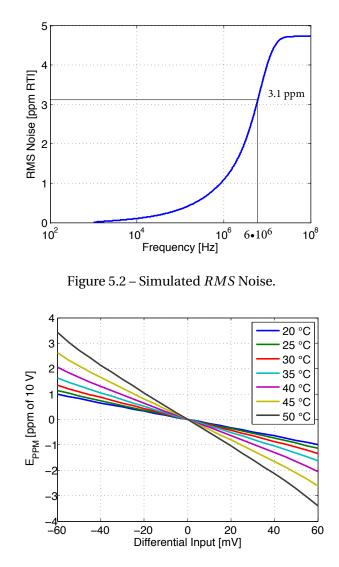

| 5.2 | Simulated <i>RMS</i> Noise.                                                                              | 45 |

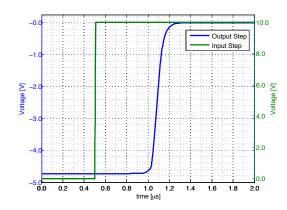

| 5.3 | Non-Linearity Curves At Different Temperatures.                                                          | 45 |

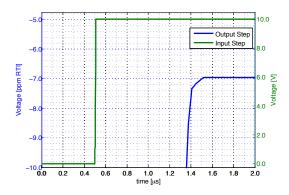

| 5.4 | Response to $10V - 10$ ns step (Input Step in Green, Output Step in Blue)                                | 46 |

| 5.5 | Response to $10V - 10$ ns step (Input Step in Green, Output Step in Blue) - Zoom                         | 46 |

#### List of Figures

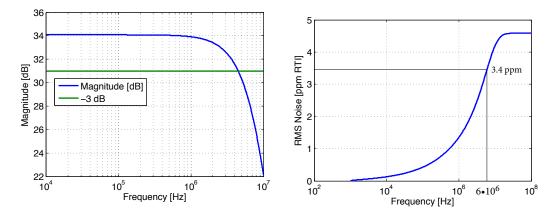

| 6.1  | Magnitude Bode Diagram and RMS Noise                                                           | 47 |

|------|------------------------------------------------------------------------------------------------|----|

| 6.2  | Observed Worst-Case Repeatability                                                              | 49 |

| 7.1  | Worst-Case Repeatability Measurement Setup                                                     | 53 |

| 7.2  | Noise of the CLIC Reference Acquisition System with Normal Fit (10,000 samples).               | 54 |

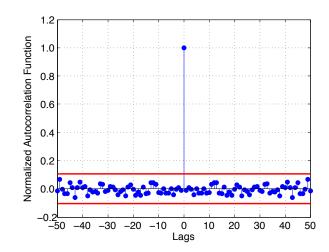

| 7.3  | Normalized Auto-Correlation Function with 99.9 $\%$ of Confidence Interval                     | 55 |

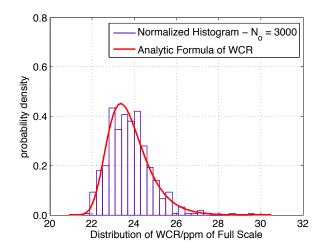

| 7.4  | <i>WCR</i> of the CLIC Reference Acquisition System for $N_o = 3,000$ and $N_{test} = 500$ .   | 55 |

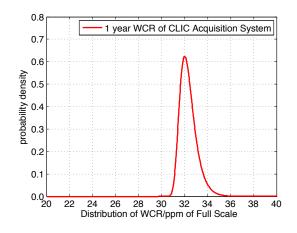

| 7.5  | Estimated <i>WCR</i> of the CLIC Reference Acquisition System for $N_o = 1.5768 \times 10^9$ . | 56 |

| 8.1  | System Frequency Response Setup                                                                | 57 |

| 8.2  | Amplitude Bode Diagram                                                                         | 57 |

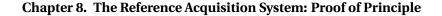

| 8.3  | Noise Evaluation Setup Block Diagram                                                           | 58 |

| 8.4  | Typical Acquired Noise Sample                                                                  | 58 |

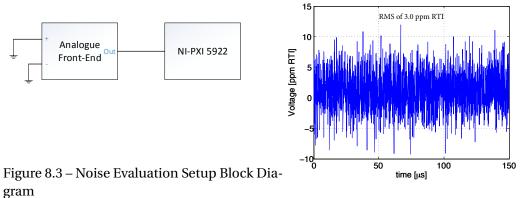

| 8.5  | Linearity Setup                                                                                | 59 |

| 8.6  | Measured Linearity                                                                             | 59 |

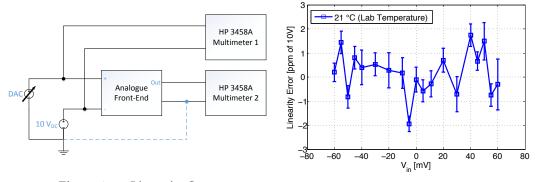

| 8.7  | Repeatability Measured in Short Circuits.                                                      | 60 |

| 8.8  | Setup For Repeatability Measurement With 10 $V_{DC}$ At Both Inputs                            | 60 |

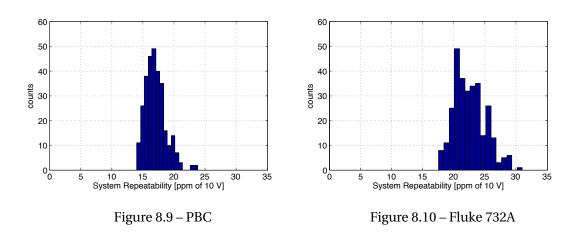

| 8.9  | PBC                                                                                            | 60 |

| 8.10 | Fluke 732A                                                                                     | 60 |

| 8.11 | Differential Sensing Circuit.                                                                  | 61 |

| 8.12 | Simulated Amplitude Frequency Response with Differential Sensing on Positive                   |    |

|      | Input                                                                                          | 62 |

| 8.13 | Simulated <i>RMS</i> Noise with Differential Sensing on Positive Input                         | 62 |

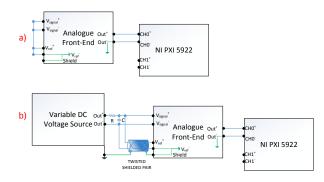

| 9.1  | Setup for measuring $CMRR_{diff}$ , with inputs: a) Shorted to Ground, and b)                  |    |

|      | Supplied by <i>DC</i> Voltage                                                                  | 63 |

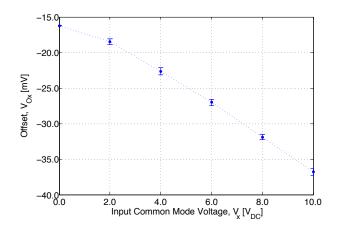

| 9.2  | Measured Output Offset ( $V_{Ox}$ ) vs Common-Mode Input Voltage ( $V_x$ ). Error bars         |    |

|      | show the standard deviation for the 68 % confidence interval $(1-\sigma)$                      | 64 |

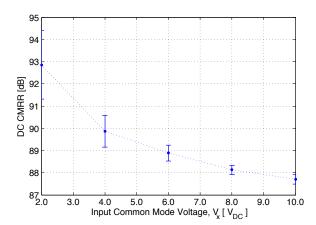

| 9.3  | $CMRR$ vs Common-Mode Input Voltage (1- $\sigma$ Uncertainty Band)                             | 64 |

| 9.4  | Ground Loop Between Two Far Grounds                                                            | 66 |

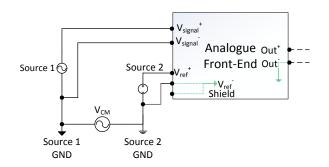

| 9.5  | Test Setup for Measuring $CMRR_{ref}$ Between the Two Voltage Reference $\ldots$               | 66 |

| 9.6  | $CM_{ref}$ definition                                                                          | 66 |

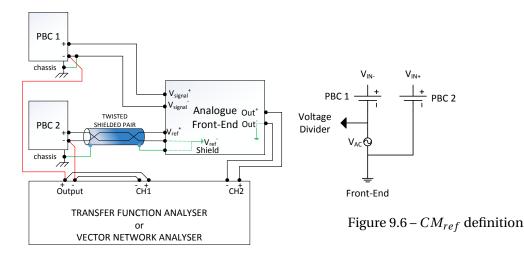

| 9.7  | $CMRR_{ref}$ Measurement Setup and $CM_{ref}$ Definition                                       | 66 |

| 9.8  | <i>CMRR</i> of the Circuit for Rejecting Common Mode Voltage Between the Voltage               |    |

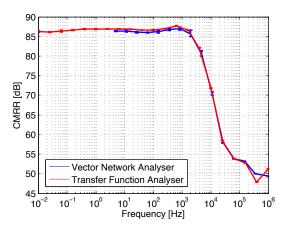

|      | Divider and the Local Ground                                                                   | 67 |

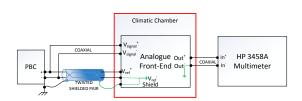

| 9.9  | Test Setup for Offset Drift Measurement                                                        | 68 |

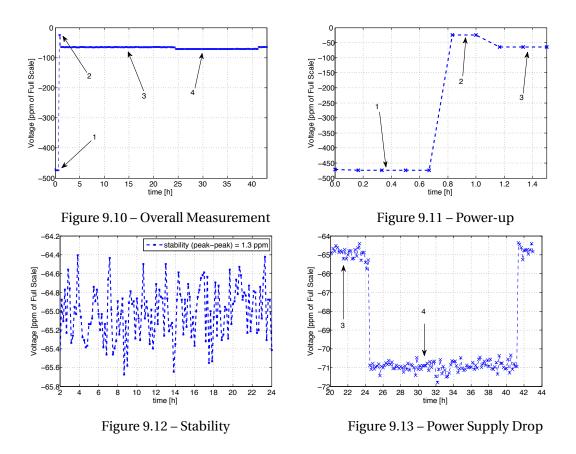

|      | Overall Measurement                                                                            | 69 |

|      | Power-up                                                                                       | 69 |

|      | Stability                                                                                      | 69 |

|      | Power Supply Drop                                                                              | 69 |

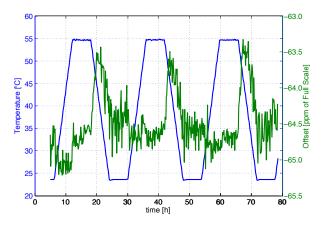

| 9.14 | Offset Variations (right-hand scale in green) Due to a 5 °C/h Temperature Profile              |    |

|      | (left-hand scale in blue)                                                                      | 70 |

#### List of Figures

| 9.15 Offset Variations (right-hand scale in green) Due to a 10 °C/h Temperature Profile            |    |

|----------------------------------------------------------------------------------------------------|----|

| (left-hand scale in blue)                                                                          | 71 |

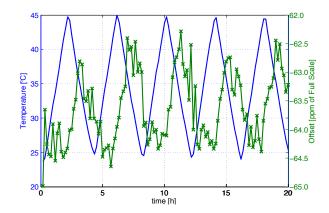

| 9.16 Offset Variations Due to a Humidity Change from 30% to 70%                                    | 71 |

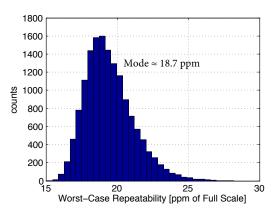

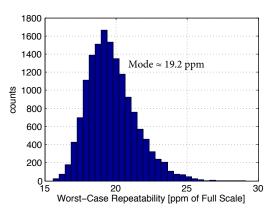

| 9.17 Worst-Case Repeatability histogram with both input shorted to GND                             | 72 |

| 9.18 Worst-Case Repeatability histogram with both input connected to a PBC                         | 73 |

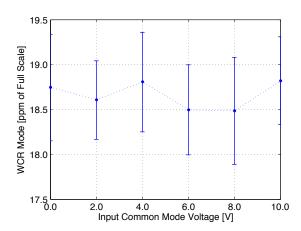

| 9.19 Mode of WCR for Different Common Mode Input Voltages with 1- $\sigma$ error bars $% \sigma$ . | 73 |

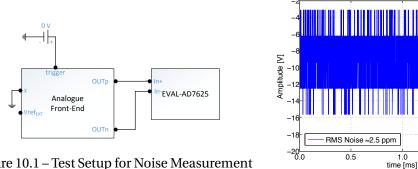

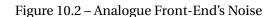

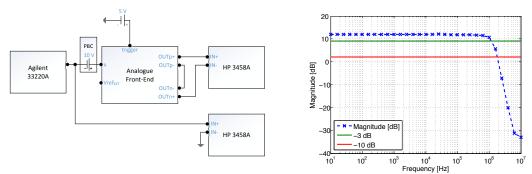

| 10.1 Test Setup for Noise Measurement                                                              | 76 |

| 10.2 Analogue Front-End's Noise                                                                    | 76 |

| 10.3 Test Setup (a) and Experimental Results (b) of Analogue Front-End's Noise                     | 76 |

| 10.4 Test Setup for Bandwidth Measurement                                                          | 76 |

| 10.5 Amplitude Frequency Response                                                                  | 76 |

| 10.6 Test Setup (a) and Experimental Results (b) of Analogue Front-End Amplitude                   |    |

| Bode Diagram                                                                                       | 76 |

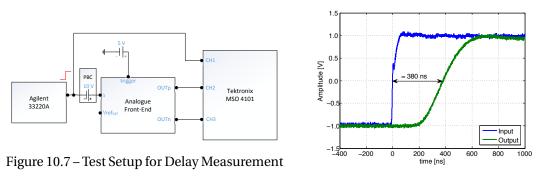

| 10.7 Test Setup for Delay Measurement                                                              | 77 |

| 10.8 Step Response                                                                                 | 77 |

| 10.9 Test Setup (a) and Experimental Results (b) of Step Response                                  | 77 |

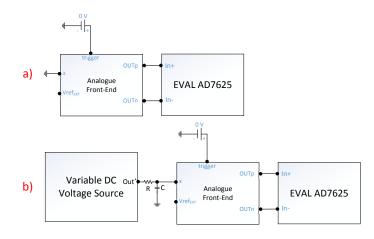

| 10.10Test Setups for DC CMRR Measurement: first (a) and second (b) test phase                      | 78 |

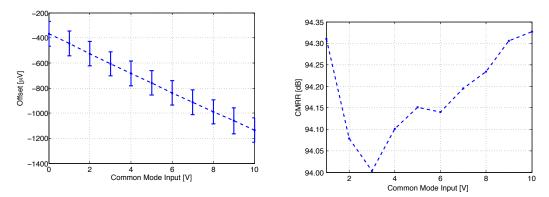

| 10.11Measured Output Offset $V_{Ox}$ vs Common-Mode Input Voltage $V_x$ (1 – $\sigma$ Uncer-       |    |

| tainty)                                                                                            | 79 |

| 10.12CMRR vs Common-Mode Input Voltage $(1 - \sigma \text{ Uncertainty})$                          | 79 |

| 10.13Ground Loop Between Two Far Grounds                                                           | 79 |

| $10.14CMRR_{ref}$ Measurement Setup                                                                | 80 |

| 10.15 $V_[CM]$ Definition                                                                          | 80 |

| 10.16 <i>CMRR</i> of the Circuit for Rejecting Common Mode Voltage Between the Voltage             |    |

| Divider and the Local Ground (1- <i>sigma</i> uncertainty)                                         | 81 |

| 10.17Test Setup for full signal reconstruction and <i>PPR</i> measurement                          | 82 |

| 10.18Pulse-to-Pulse Repeatability in nominal working conditions                                    | 82 |

| 10.19Online Reference System Accuracy                                                              | 82 |

### List of Tables

| 1   | Typical Pulse Characteristics.             | 6  |

|-----|--------------------------------------------|----|

| 3.1 | Main Requirements                          | 28 |

|     | Reference Acquisition System Specification |    |

| 6.1 | Expected Delay                             | 48 |

### **Symbols and Acronyms**

*ADC* = Analogue-to-Digital Converter AWGN = Additive White Gaussian Noise CDF = Cumulative Density Function CLIC = Compact LInear Collider CMRR = Common-Mode Rejection Ratio DSC = Differential Sensing Circuit ENOB = Effective Number of Bits EVT = Extreme Value Theory*FTD* = Flat-Top Duration GUM = Guide to the expression of Uncertainty in Measurement *iid* = independent and identically distributed *LHC* = Large Hadron Collider LSB = Least Significant Bit LSE = Least Squares Errors  $N_o$  = Number of Observations  $N_p$  = Number of pulses  $N_s$  = Number of Samples *PDF* = Probability Density Function ppm = parts per million (referred to 10V so 1 ppm = 10 $\mu$ V) *PPR* = Pulse-to-Pulse Repeatability *RMS* = Root Mean Square *RTI* = Referred to Input SINAD = SIgnal-to-Noise And Distortion ratio VIM = International Vocabulary of Metrology WCU = Worst-Case Uncertainty

WCR = Worst-Case Repeatability

### Introduction

A power converter is a device able to process and control the flow of electric energy by supplying voltages and currents in a form that is optimally suited for the user loads. In power engineering, a converter has to transform electric energy from one form to another (e.g. from AC to DC) [1]. High-performance power converters are becoming more and more used in applications in which a big amount of energy is demanded by the load and, thus, the power consumption from the electrical grid should be kept as low as possible (e.g. reducing losses). This is the case, for instance, of smart power flow management among separate energy storage units [2] or high-performance electric vehicles [3]. In many applications in which power consumption is relevant, pulsed power converters are used [4]. In Fig.1, the typical topology of a pulsed power converter is sketched. The energy coming from the electrical grid is stored into a charging system. A pulse forming system allows the stored energy to be released to the load over a short period, by obtaining a train of high peak-power pulses.

An adequate control for power supply quality is provided through a comprehensive characterization of power pulses (node *B* in Fig.1), both in time and frequency domains. Of course, to characterize the power pulses, a reference measurement system is needed [5]. However, the main evolution efforts were dedicated to pushing the technology toward to the sub-nanosecond regime overlooking the aspects related to the accurate and precise digitization of the pulses themselves. Thus, the metrological problem of a full characterization of the

Figure 1 – Typical Topology of a Pulsed Power Converter.

pulsed power converter becomes challenging because of the lack of reference instruments [6]. Furthermore, even if the reference standards concerning pulse measurements [7] give both definitions and procedures to evaluate the pulse parameters, a full characterization procedure in time-domain is not provided; thus, custom methods have to be identified along the specific applications.

Due to all the uncertainty sources inside the measurement chain (e.g. noise super-posed to the measurand, intrinsic uncertainty of the measurement system, and so on), a statistical approach should be used to define the pulses characteristics. In many industrial applications, a worst-case approach is desired in order to determine an uncertainty interval in which any measurement will lie (under given conditions) [8].

In addition, applying digital methods to the control of power converters allows different enhancements as (i) creating new features, (ii) improving performance, and (iii) increasing flexibility while keeping low the cost [9]. Indeed, high-performance pulsed power converters usually exploit a digital control loop for regulating the voltage out of the charging system [9]. To do that, a high-performance real-time acquisition system is needed to digitize the output of the charging system (node *A* in Fig.1) and provide the samples to the controller of the loop in order to adjust the voltage [10]. In this PhD thesis, all these aspects are discussed and addressed.

In particular, in *PART 1*, a background and a state of the art on the measurement systems needed to correctly operate a high-performance power converter are presented.

In *PART 2*, the analytical model for predicting the Worst-Case Uncertainty (*WCU*) of a measurement system is discussed and detailed for an instrument affected by gaussian noise. Furthermore, the study and design of a *Reference Acquisition System* for characterizing the high-power pulses of the klystron modulators of the CLIC, is presented. Finally, the design of the *Real-Time Acquisition System* for controlling the CLIC power converter, is presented.

In *PART 3*, the numerical results obtained in simulation of the three main topics (Worst-Case Uncertainty, Reference Acquisition System, Real-Time Acquisition System) are discussed to demonstrate the effectiveness of the proposals.

Finally, in *PART 4*, the experimental results of a case study in the framework of the new linear electron-positron particle accelerator currently under study at *CERN*, the Compact LInear Collider (*CLIC*) [11], are reported and compared with the simulations in order to obtain the final validation of the proposals.

## PART 1 - BACKGROUND AND STATE OF THE ART

#### Background

At CERN, a new particle accelerator is currently under study, the Compact LInear Collider (*CLIC*) [11]. The CLIC project is focused on the design of a linear electron-positron collider with a center-of-mass collision energy of 3 *TeV* and a luminosity of  $2 \times 10^{34} cm^{-2} s^{-1}$ .

In Fig.2, the latest layout of CLIC is reported. The top part of the figure shows the Drive Beam generation in two Main Linacs and the successive time compression of the Drive Beam pulses in the Delay Loops and Combiner Rings (CR1 and CR2). The time-compressed Drive Beam reaches a current of about 100 *A* at a beam energy of about 2.4 *GeV*. This compressed Drive Beam is transported through the Main Linac tunnel to 24 individual turnarounds. Each Drive Beam segment is directed by pulsed extraction elements, for the final RF power generation, into the accelerating structures of the Main Beams. Hence in the Main Linac tunnel we find four beam transport lines: the transport lines of the Main Beam and Drive Beam. The beams collide after a long Beam Delivery Section (BDS) (collimation, final focus) in one interaction point (IP) in the center of the complex [12].

Figure 2 – CLIC Layout at 3 TeV

Fig.3, shows a possible implementation of this accelerator in the Geneva area. The proportions become more clear. The generation of the Main Beams, the Drive Beams, and the central collision point would fall into existing CERN territory, whereas the two 24 m long acceleration tunnels would extend into the local area as underground installations. The blue dots show the tunnel length needed for a collision energy of 3 TeV, whereas the pink dots indicate the size of the installation for 500 GeV.

To operate such a high-performance particle accelerator a huge amount of energy needs to be provided by its power converters. In fact, the *mass-energy* equivalence formulated by Einstein,

Figure 3 - Map showing a potential location for the CLIC accelerator complex

reported in equation (1), states that the more particles are accelerated, the more mass they gain and thus, the more high-energy collisions can be observed.

$$E = mc^2 \tag{1}$$

In order to accelerate and guide a beam of charged particles (q), forces shall be applied according to equation (2):

$$\vec{F} = q(\vec{E} + \vec{v} \times \vec{B}) \tag{2}$$

The first part of equation (2),  $q\vec{E}$ , indicates that particles are accelerated by means of an electrical field. To reach an adequate level of acceleration, high-voltage power converters are needed to generate strong electrical fields. In addition, the second part of equation (2), states that as the energy of particles increases, the magnetic field controlling their trajectory must also increase. Therefore, strong magnetic fields are demanded to the electro-magnets. Once again, to do that, power converters are needed.

In order to reach the desired energy level, together with reasonable power consumption from the electrical grid, *CLIC* power converters [13] are demanded to deliver a pulsed power repeatable to better than  $\pm 100$  parts per million (ppm) [14]. Its klystron modulators [15] will therefore be operated in pulsed mode with a pulse length of  $140 \mu s$  [14],[11]. In Tab.1, the typical specifications of the *CLIC* power pulses are reported.

| Pulse Specification                |                      |                 |  |

|------------------------------------|----------------------|-----------------|--|

| Parameter                          | Acronym              | Value           |  |

| Nominal Pulse Amplitude Level      | V <sub>kn</sub>      | 180 kV          |  |

| Nominal Pulse Current Level        | Ikn                  | 150 A           |  |

| Pulse Peak Power                   | P <sub>mod-out</sub> | $\approx 27 MW$ |  |

| Positive Going Transition Duration | t <sub>rise</sub>    | 3 <i>µs</i>     |  |

| Negative Going Transition Duration | t <sub>fall</sub>    | 3 µ s           |  |

| Transition Settling Duration       | t <sub>set</sub>     | $5 \mu s$       |  |

| Flat-Top Duration                  | t <sub>flat</sub>    | 140 <i>µs</i>   |  |

| Repetition Rate                    | REPR                 | 50 Hz           |  |

| Voltage Overshoot                  | Vovs                 | 1%              |  |

| Precisions                         |                      |                 |  |

| Flat-Top Tolerance                 | FTT                  | 0.85%           |  |

| Pulse-to-Pulse Repeatability       | PPR                  | ±100 ppm        |  |

| Frequency Range of Interest        | FRI                  | 1  kHz - 5  MHz |  |

Table 1 – Typical Pulse Characteristics.

Two different topologies of the *CLIC* klystron modulator are currently under study at *ETH Zurich* (*CH*) [16] and the *LEEPCI Laval* (*CA*) [17]. In Fig.4, the latest topology of the modulator under study at *ETH Zurich* is sketched. As shown in Fig.4, to meet the requirements for the RF power quality, derived directly from the accelerator performance specifications, two high-performance measurement system are needed.

Figure 4 – Topology of the CLIC Klystron Modulator.

The first one (*3 kVAcquisition System* in Fig.4) will be used for a real-time control of the output voltage of the charging system. The second one (*180 kVAcquisition System* in Fig.4) will be used for an offline verification of the modulator performance, in particular with respect to its Pulse-to-Pulse Repeatability (PPR).

#### State of the Art

Pulsed power supplies are widely used in many applications as radars, pulsed lasers, electromagnetic pulse generators and particle accelerators. In this framework, the full characterization of power pulses is needed, both in time and frequency domains, in order to guarantee an adequate control for power supply quality.

The market interest and the research on pulse measurements are significantly dedicated to improving the immunity to interference demanded by the transmission protocols in Ultra Wide-Band (UWB) applications [18]. This trend was highlighted in the state of the art for time-domain pulse waveform measurements in the nanosecond regime, produced by the National Institute of Standards and Technology (NIST) [6]. The main evolution efforts were dedicated to pushing the technology toward to the sub-nanosecond regime overlooking the aspects related to the accurate and precise digitization of the pulses themselves. Thus, the metrological problem of a full characterization of the pulsed power converter becomes challenging because of the lack of reference instruments. Furthermore, even if the reference standards concerning pulse measurements [7] give both definitions and procedures to evaluate the pulse parameters, a full characterization procedure in time-domain is not provided; thus, custom methods have to be identified along the specific applications.

In this context, the crucial specification of Worst-Case Uncertainty (WCU) [19] is required as in many other engineering fields, such as nuclear or aero-space applications. However, WCU is not included into the Guide to the Expression of Uncertainty in Measurements (GUM) [20], which mainly focuses on providing the standard uncertainty associated with a best estimate of a measurand. More recently, the focus of the GUM working group has shifted towards the probability density function (pdf) as a comprehensive way to express the experimenter's knowledge of a measurand [21]. Moreover, in the measurement practice, the WCU is usually determined as a Type-B uncertainty [22], e.g. on the basis of manufacturer's production specification of the particular instrument. In many cases of research, when custom-designed instruments have to be characterized, manufacturer's specifications are not available, thus Type-A methods have to be defined for determining WCU. In fact, this turns into the problem of characterizing the extreme values (e.g. the peaks) considered as the worst cases of a measurement system working in its nominal conditions [23]. The Uni-variate Extreme Value Theory, or simply Extreme Value Theory, is widely used for predicting the peak values of a given phenomenon in different fields (e.g., risk management [24],[25], finance, economics, or even for estimating the fastest human time on the 100 m sprint [26]), and specifically in engineering, e.g., studies ranging from tides [27] to accelerator technology [28]. As an example, in telecommunications, an accurate expression for the peak distribution of the Orthogonal Frequency Division Multiplexing (OFDM) envelope was determined by the University of Massachusetts [29]. In fact, the main problem about the applicability of OFDM systems in low-power wireless applications is the highly-variable amplitude of transmitted signals. The above study defined a rigorous method for predicting the upcoming peak values of the envelope by the previous peak observations.

However, this means that each prediction needs to be supported by an adequate data collection which, in some cases, requires very-long observations of the phenomena, resulting in unfeasible test duration. Therefore, an analytical model was identified to overcome this problem by predicting the *WCU* statistical distribution of a given instrument by only characterizing its internal noise.

If on one side one has to guarantee the final performance of a power converter by means of a reference acquisition system, on the other side the introduction of a digital control loop allows different enhancements while keeping low the cost of the converter [9]. Indeed, high-performance pulsed power converters usually exploit a digital control loop for regulating the voltage out of the charging system [9]. To do that, a high-performance real-time acquisition system is needed to digitize the output of the charging system (node *A* in Fig.1) and provide the samples to the controller of the loop in order to adjust the voltage. In designing an effective digital control system, the main challenge is to meet simultaneously both the metrological requirements and the time constraints imposed by the specific application. As a matter of fact, the stability of a regulator is heavily affected by the speed of the control loop. Researchers working in fields ranging from military [30] to electronic controls in automotive [31], found great interest in this research line. However new and more demanding applications arise from particle accelerator structures in which the repeatability of the power converters is a key parameter for guaranteeing the performance of the machine.

PART 2 - PROPOSAL

### **1** The Worst-Case Uncertainty Analytical Model

In this chapter, the exact Cumulative Distribution Function (*CDF*) of the uncertainty of several measurements, modelled as independent and identically distributed (*iid*) normal random variables, is presented, together with an approximated *pdf* of the Worst Case Uncertainty.

#### 1.1 Overview

In a set of replicated measurements of the same measurand, the upcoming peaks can be forecast without any knowledge about preliminary observations or data collections, thus overcoming the main issue related to the Extreme Value Theory. In section 1.2, the metrological problem is formalized and an analytical *WCU* model is proposed. In section 4.1, a case study at CERN on a reference acquisition system for assessing the performance of a high-voltage pulsed power supply for the klystron modulators of the Compact LInear Collider (*CLIC*) is introduced. In particular, in section 4.2, the numerical results of performance analysis of the proposed model, aimed at confirming the validity of the underlying approximations, are reported. Finally, in section 7, the distribution approximated through the model is validated by comparison with experimental results obtained with the reference acquisition system for the *CLIC* klystron modulators.

#### 1.2 Worst-Case Uncertainty Theoretical Model

In this section, an approximated *pdf* of the type-A WCU is defined for Gaussian-noise measurement systems by deriving the exact *CDF* of replicated measurements, modelled as independent and identically distributed (*iid*) normal random variables. In particular, after stating the metrological problem, the WCU definition is given, by analysing the three random variables corresponding to its three main operations of difference, absolute value and maximum. Finally, the analytical model is derived, by leaving to the Appendix A the rigorous proofs of both its equation and the Gaussian noise approximation.

#### 1.2.1 Worst-Cacse Uncertainty Definition

In many situations, a periodic signal is to be acquired in a given time window, and measurements have to be taken in different periods. Among these periods, the measured instantaneous values at the *same* (in equivalent time) sampling instant can vary significantly owing to several uncertainty sources. In many research cases when custom-designed instruments have to be characterized, manufacturer's specifications are not available, thus Type-A methods have to be defined for determining *WCU*. In fact, this turns into the problem of characterizing the extreme values (e.g. the peaks) considered as the worst cases of a measurement system working under its nominal conditions [23].

If the measurand is assumed to be *ideal* and the measurement system has negligible instability within the signal period, then the measurement is affected only by the instrumental *noise*, defined according to the Standard IEEE 1057-07 [32] as: "Any deviation between the output signal (converted to input units) and the input signal except deviations caused by linear time invariant system response (gain and phase shift), a dc level shift, total harmonic distortion (THD), or an error in the sample rate".

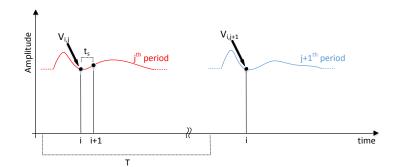

Hereafter, all the samples of the measurement system noise (and their random effect) are modelled as independent and identically distributed (*iid*) random variables. By acquiring  $N_s$  samples per period and a total number  $N_p$  of periods, the *WCU* can be defined as in equation 1.1, where three operations are carried out on each of the  $N_o$  pairs of acquired periods ( $N_o = N_p - 1$ ), (i) the difference, (ii) the absolute value, and (iii) the maximum:

$$WCU = max_i |V_{i,j} - V_{i,j+1}|$$

(1.1)

where  $V_{i,j}$  and  $V_{i,j+1}$  are the values of the  $i^{th}$  samples of the  $j^{th}$  and  $(j+1)^{th}$  acquired periods, respectively (Fig.1.1), with:

$$\begin{cases} 1 \le i \le N_s \\ 1 \le j \le N_o \end{cases}$$

(1.2)

In the following subsections, the three random variables, corresponding to the above operations, are analysed for deriving the WCU model equation.

#### The Difference Random Variable

For a given index j,  $N_s$  random variables  $Y_i = V_{i,j} - V_{i,j+1}$  with  $1 \le i \le N_s$  are defined. Actually,  $Y_i$  coincides with  $Y_{i,j}$ , therefore, in the following, the latter full notation will be used only when

Figure 1.1 – Worst-Case Uncertainty Definition ( $t_s$ : sampling period, T: signal period).

necessary for the sake of clarity. The generic  $V_{q,k} = \hat{V}_{q,k} + n_{q,k}$  is the sum of the deterministic sample of the ideal measurand  $\hat{V}_{q,k}$  and the random variable  $n_{q,k}$  which is a sample of the stationary stochastic process n(t) that represents the time-domain noise of the measurement system.

$$\hat{V}_{i,j} = \hat{V}_{i,k} \quad \forall \begin{cases} 1 \le i \le N_s \\ j,k \in N \end{cases}$$

$$(1.3)$$

#### The Absolute Value Random Variable

Under the assumption of statistical independence upon the index *j* (the issue of statistic dependence will be discussed in detail in the subsequent sections), the Cumulative Distribution Function (*CDF*)  $F_{|Y_i|}(x)$  is computed:

$$F_{|Y_i|}(x) = Pr(|Y_i| \le x) = Pr(-x \le Y_i \le x) =$$

$$= Pr(Y_i \le x) - Pr(Y_i \le -x) =$$

$$= F_{Y_i}(x) - F_{Y_i}(-x)$$

(1.4)

By assuming that each  $V_{i,j}$  is symmetrically distributed around its mean value, each  $Y_i$  is symmetrically distributed around zero:

$$F_{Y_i}(x) - F_{Y_i}(-x) = F_{Y_i}(x) - [1 - F_{Y_i}(x)] =$$

$$= 2F_{Y_i}(x) - 1$$

(1.5)

13

Finally, the absolute value is only defined for positive values of *x*:

$$F_{|Y_i|}(x) = \begin{cases} 2F_{Y_i}(x) - 1 & , x \ge 0\\ 0 & , x < 0 \end{cases}$$

(1.6)

The pdf is given by the derivative of the CDF:

$$f_{|Y_i|}(x) = \begin{cases} 2f_{Y_i}(x) & , x \ge 0\\ 0 & , x < 0 \end{cases}$$

(1.7)

#### The Maximum Random Variable

Let us consider now the maximum  $M_j$  between the  $N_s$  independent and identically distributed (i.i.d.) random variables  $|Y_1|, |Y_2|, ..., |Y_{N_s}|$  (taken from the  $j^{th}$  and  $j + 1^{th}$  periods). The dependence upon j has been already neglected, therefore  $M_j = M = max \{|Y_1|, |Y_2|, ..., |Y_{N_s}|\}$ . Given the i.i.d. assumptions, the *CDF* of M is expressed as [33]:

$$F_M(x) = Pr(M \le x) = Pr(|Y_1| \le x, |Y_2| \le x, ..., |Y_{N_s}| \le x) = \prod_{i=1}^{N_s} Pr(|Y_i| \le x) = F_{|Y_i|}^{N_s}(x) \quad (1.8)$$

The *CDF* of *M* can be now expressed as a function of the *CDF* of the underlying distribution  $Y_i$ .

$$F_{M_j}(x) = \begin{cases} \left[2F_{Y_i}(x) - 1\right]^{N_s} & , x \ge 0\\ 0 & , x < 0 \end{cases}$$

(1.9)

The *pdf* is simply given by the derivative of the *CDF*:

$$f_{M_j}(x) = \begin{cases} 2N_s f_{Y_i}(x) \left[2F_{Y_i}(x) - 1\right]^{N_s - 1} & , x \ge 0\\ 0 & , x < 0 \end{cases}$$

(1.10)

Equation (1.10) describes the distribution of  $WCU_j$ , as the maximum of the absolute value of the difference of all the samples between two consecutive periods (the index *j* is fixed).

14

#### 1.2.2 Analytical Model

Once the *WCU* was estimated for a given sample size  $N_o$ , the variability of *M* over the  $N_s$  periods is considered:

$$\begin{cases} WCU_{j} = M_{j} = max_{i}|V_{i,j} - V_{i,j+1}| &, 1 \le i \le N_{s} \\ WCU(N_{o}) = Z = max_{j} \{M_{j}\} &, 1 \le j \le N_{o} \end{cases}$$

(1.11)

Having assumed the independence on *j*, the *CDF* of  $Z = Z^{ind}$  can be computed straightforwardly by simply raising (1.9) to the  $N_o^{th}$  power:

$$F_{Z^{ind}}(x) = F_{M_j}^{N_o}(x) = \begin{cases} [2F_{Y_i}(x) - 1]^{N_s \cdot N_o} & , x \ge 0\\ 0 & , x < 0 \end{cases}$$

(1.12)

In the particular case of independent random variables, the analytical equation of the *PDF* of the *WCU* distribution is finally assessed by computing the derivative of the equation (1.12):

$$\begin{cases} f_{Z^{ind}}(x) = 2N_s N_o f_{Y_i}(x) [2F_{Y_i}(x) - 1]^{N_s N_o - 1} , x \ge 0 \\ 0 , x < 0 \end{cases}$$

(1.13)

So far, the validity of all the equations is guaranteed by assuming that: (i) all the variables  $V_{i,j}$  are symmetrically distributed around their mean value (or equivalently, each  $Y_{i,j}$  is symmetrically distributed around zero), and (ii) the dependence on j of  $Y_{i,j}$  can be neglected. Whereas the first assumption is very weak and fully realistic, the independence on j is very strong and not credible, therefore it must be dealt with properly. In Appendix A, the actual *WCU* distribution will be presented and discussed. In addition, it will be also proved that the distribution (1.13) is a worst case approximation of the actual distribution in the case of white and Gaussian noise n(t) of the measurement system. In section 4.2, it will be shown that the worst-case approximation accurately models simulation data, whereas in section 7, also the hypothesis of white Gaussian noise will be tested against experimental data of the case study.

### **2** The Reference Acquisition System

As already said, pulse measurement literature is mainly focused on fast systems with relaxed metrological requirements. In this chapter a new research trend on slower signals with stringent metrological requirements is explored. In particular, an acquisition system to characterize the flat-top of  $3\mu s$  rise-time trapezoidal voltage pulses, with bandwidth of 5MHz, repeatability of  $\pm 25 ppm$ , and noise *RMS* level in the order of 3 ppm, is proposed.

#### 2.1 Overview

In section 2.2, the requirements for the proposed acquisition system as well as the definition of the main target parameter, the Pulse-to-Pulse Repeatability (*PPR*), are defined. Afterwards, in section 2.3, the proposal of an analogue front-end for improving the measurement conditions is presented together with its design choices. It's important to clarify that the circuit presented in this section is just a proof demonstrator able to validate the feasibility and effectiveness of the proposed architecture. In section 5 and 8 respectively, the Pspice simulations and the experimental results of the proof demonstrator are presented in order to demonstrate a good match between the simulated demonstrator and the actual prototype. An important point is discussed in section 8.0.5 where a Differential Sensing Circuit (*DSC*) is presented. This circuit represents the interface to the upstream voltage divider (discussed afterward); therefore it will ensure a good decoupling between the voltage divider and its load, the presented acquisition system.

#### 2.2 Requirements for CLIC

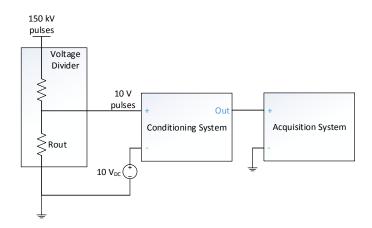

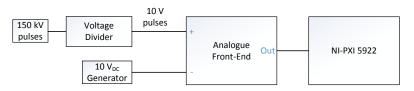

The complete measurement system consists of a high-precision high-voltage divider, able to convert  $150 \, kV$  pulses into  $10 \, V$  pulses [34], and a high-speed high-repeatability acquisition system. However, the interest of this work is limited only to the acquisition system; as a matter of fact, all the contribution of the upstream voltage divider are neglected so far, focusing only on the custom analogue front-end and the digitizer.

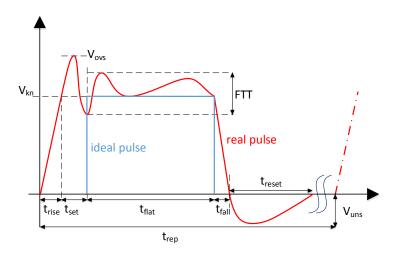

Figure 2.1 – Pulse Parameters Definition.

#### 2.2.1 Pulse-to-Pulse Repeatability

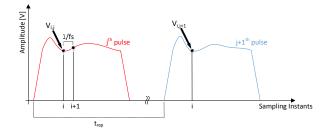

The Pulse-to-Pulse Repeatability (PPR) is defined as (Fig.2.2):

$$PPR = max|V_{i,j} - V_{i,j+1}|$$

(2.1)

By considering two consecutive pulses flat-tops and their instantaneous voltage values in the *same* (in equivalent time) sampling instant *i* within the waveform flat-top (Fig.2.2),  $V_{i,j}$  and  $V_{i,j+1}$ , the main goal of the measuring system is to verify that:

$$PPR \le PPR_{max} \tag{2.2}$$

ANSI/NCSL Z540-1-1994 states: (i) "*The laboratory shall ensure that calibration uncertainties are sufficiently small so that the adequacy of the measurement is not affected*" and (ii) "*Collective uncertainty of the measurement standards shall not exceed 25% of the acceptable tolerance*" [35], defining the Test Uncertainty Ratio (TUR) as 1 : 4. As a consequence, in order to adequately characterize the pulses with repeatability tolerance ( $PPR_{max}$ ) e.g. of  $\pm 100 \, ppm$ , the target repeatability of the measurement system should be better than  $\pm 25 \, ppm$ .

#### 2.2.2 The Acquisition System

The project CLIC of CERN requires the repeatability specification to be respected only during the pulse flat-top, for the range of frequencies (1 kHz, 5 MHz) [14]. To prove pulse-to-pulse

Figure 2.2 – Pulse-to-Pulse Repeatability Definition.

repeatability up to 5 MHz, the acquisition system has to sample at least at a rate of 10 MS/s according to the Nyquist criterion. In addition, if the acquisition system has a suitable stability within the repetition period of the pulses train (20 ms), the only factor that could affect *PPR* is noise (including quantization noise). By assuming a known distribution for the system's noise, a statistical relation between *RMS* noise and peak-based *PPR* exploits the concept of confidence interval (such as usual for type-A uncertainty in the ISO Guide of Uncertainty [20]). Furthermore, the resolution is often used as the first-approach index for evaluating the suitability of an instrument for a measurement. In this case, an instrument with an *LSB* greater than 25 *ppm* cannot ensure a *PPR* better than 25 *ppm*.For taking into account the actual non-ideality of the acquisition board, the *effective resolution* in terms of *ENOB* is considered (as usual in experimental physics under suitable assumptions about the actual quantizer model underlying the *ENOB* definition). Under these hypotheses, the specification on repeatability can be translated into a corresponding constraint on noise. In this case, for a direct sampling of the pulse with an input range of (0, 10) *V*, a necessary (but not sufficient) condition to assess signal variations in the order of 25 *ppm* is:

$$LSB = \frac{InputRange}{2^{ENOB}} = \frac{10V}{2^{ENOB}} < 25 \, ppm = 250 \, \mu V \iff$$

$$\iff ENOB > 15.3$$

(2.3)

19

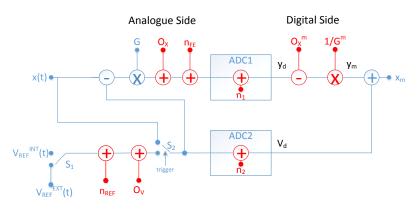

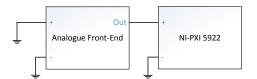

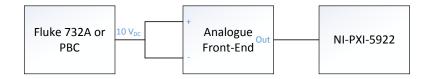

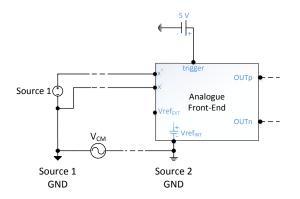

Figure 2.4 - Analogue Front-End Block Diagram.

## 2.3 Analogue Front-End

## 2.3.1 Basic Ideas

Nowadays, state-of-the-art acquisition systems on the market, operating at sampling rates equal or higher than 10 MS/s with a full scale of at least 10 V, do not exceed 14 nominal bits. Conversely, acquisition boards (such as NI-PXI-5922 from National Instruments) reach also 15 MS/s with a nominal resolution of 16 bits, but with a maximum input range of  $\pm 5 V$ . This does not allow direct measurements of the 10 V pulses, therefore an analogue pre-conditioning front-end is needed. The basic idea is to conceive a front-end that subtracts the nominal value of the flat-top from the pulse and amplifies the resulting signal (Fig. 2.3). This allows the requirements of the digitization to be relaxed, by amplifying the most significant part of the input signal, the pulse flat-top. As a matter of fact, the repeatability specification (PPR) has to be verified only during the flat-top of the pulse; by placing the flat-top around zero, the analogue front-end improves the dynamic range of the digitization system. However, this conditioning circuit introduces a certain amount of noise, much higher than the quantization noise of the acquisition board which needs to be carefully minimized in the design.

#### 2.3.2 Concept Design

The architecture of the front-end is outlined in Fig.2.4. The upper input buffer provides veryhigh input resistance to the preceding high-voltage divider, while the lower buffer centers the 10 V pulse flat-top around zero, in order to improve the dynamic range of the digitization. The subsequent gain stage amplifies the pulse flat-top, in order to best fit the acquisition board range  $\pm 5 V$ . The clipping stage avoids saturation of the subsequent acquisition board input circuitry. This ensures all the devices of the circuit work in their linear region of operation, in order to assure their long-term performance. The range  $\pm 5 V$  is used because the  $\pm 1 V$ is not compatible with the adopted clipping strategy. In fact, clipping with levels as low as  $\pm 1.25 V$  is unfeasible owing to the over-voltage handling of the NI PXI-5922, that shows an unexpectedly long recovery time. Lower clipping rails would reduce the useful range and give rise to high non-linearity arising from the diodes behavior in the clipping region. With a  $\pm 5 V$ full-scale, the clipping levels are set to about  $\pm 4.7 V$  dedicating a useful range of  $\pm 2.5 V$  for the flat-top. The flat-top tolerance of about  $85 mV_{pp}$  is fit into the  $\pm 2.5 V$  range by means of a total amplification of about 50 V/V.

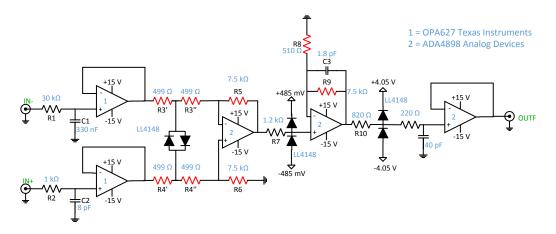

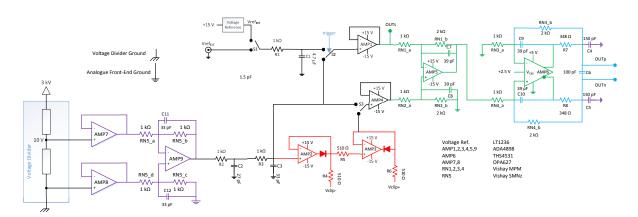

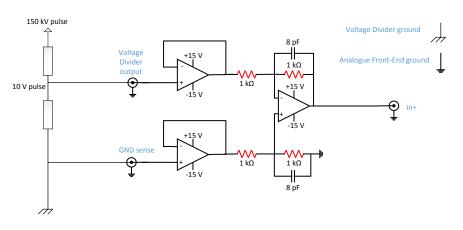

#### 2.3.3 Physical Design

A circuit performing the above mentioned tasks is depicted in Fig.2.5. The overall gain of about 50 V/V, chosen for the above mentioned reason, is realized by two separated stages since no adequately low-noise operational amplifiers have a bandwidth of at least 5 MHz for such gain. In the proof demonstrator the two input signals are firstly filtered through two simple RC low-pass filters in order to reduce the input noise (indeed the final version of the system will be equipped by the mentioned interface to the voltage divider discussed in 8.0.5); the  $10 V_{DC}$  channel is heavily filtered (16 Hz) whereas the input pulse channel needs to be wide-band (20 MHz). The two buffers (model OPA627 of Texas Instruments) have the following characteristics:

- Supply voltage range up to  $\pm 18V$  ( $\pm 15V$  rails were used in order to have an input voltage range of at least  $\pm 10V$ )

- High input resistance, in order to minimize input bias current (10 *pA* is the maximum input bias current specified on the datasheet);

- Low input capacitance (7 *pF* specified on the datasheet), in order to not affect the compensation of the voltage divider (taking into accout also the capacitance of the long connection cables in the order of hundreds of *pF*).

- A current noise spectral density of  $2.5 f A/\sqrt{Hz}$  and a voltage noise of  $4.5 nV/\sqrt{Hz}$ . At to date, the high-voltage divider has not been designed yet at CERN by the CLIC Team. Thus, the actual value of its lower-arm equivalent resistance is not available. In any case, even if an equivalent resistance of 100  $k\Omega$  is assumed, a voltage noise of  $0.25 nV/\sqrt{Hz}$  is achieved on the buffer, still negligible with respect to its voltage noise.

Figure 2.5 – Analogue Front-End Schematic.

• Very good dynamic performance, in order to have a bandwidth of at least 5 MHz, in particular for the positive input buffer (16 MHz at gain of 1 is declared).

Two fast diodes (model LL4148) in anti-parallel clip the input differential signal in order to not saturate the difference amplifier (nominal gain of 7.5) when the signal on the inverting input is zero (i.e., without pulse). In this stage, the input resistors (R3 and R4) are split in order to limit the current flowing through the diodes when they are active; in particular, R3' and R4' limit the current before and after the flat-top of the pulse. R3 = R3' + R3'' together with R5, as well as R4 = R4' + R4'' together with R6, set the gain during the flat-top (when the diodes are OFF). The voltage drop across the diodes, when they are ON, is conversely amplified by the ratio R5/R3'' = R6/R4''. Therefore, by choosing R3' = R3'' and R4' = R4'', the flat-top gain is half of the gain seen by the voltage drop across the diodes when they are active. Obviously, the same clipping operation has to be repeated at the output of the same stage. Also for this stage, the same fast diodes were chosen (model LL4148). The clipping voltage is conveniently set by means of two opposite rails in this stage. A non-inverting stage (nominal gain of 6.9) was chosen owing to its high input impedance, making resistor R7 ininfluent for the gain setting. Two identical amplifiers (model ADA4898 of Analog Devices) were chosen for the two amplifying stages owing to their excellent performance in terms of:

- Input noise  $(0.9 \, nV / \sqrt{Hz} \text{ declared});$

- Bandwidth (65 *MHz* at gain of 1 allows the 7.5 amplification assuring more than 8 *MHz* bandwidth);

- Supply voltage range of  $\pm 15 V$  allowed in order to have an input voltage higher than 10 V.

Finally, after the second amplification stage, a last pair of clipping diodes (same model LL4148) are needed to avoid over-range in the input stage of the subsequent acquisition board (the

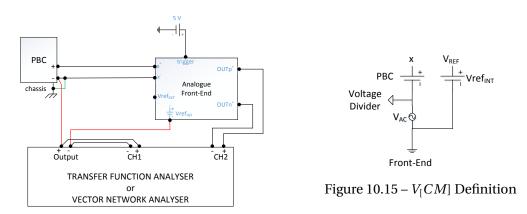

Figure 2.6 - The Enhanced Analogue Front-End

two rail voltages can be set according to the input stage limits). The last consideration is about the requirements on resistor quality; in Fig.2.5, all the resistors in red affect the overall gain stability and *CMRR* [36]. An array of 8 matched precision resistors can guarantee at the same time high gain stability (low temperature coefficient can easily be achieved) and high *CMRR* (low relative tolerances down to 0.01% can be specified). However, more stringent performance requirements arose from deeper investigations on the actual working conditions of the system and from *CLIC* requirements evolution. In particular, if an adequate *CMRR* value is not achieved, the differential stage (red dotted circle in Fig.2.6) would not perform an effective subtraction. Furthermore, given the harsh work environment, the dependency of system performance on environmental changes and conditions must also be investigated.

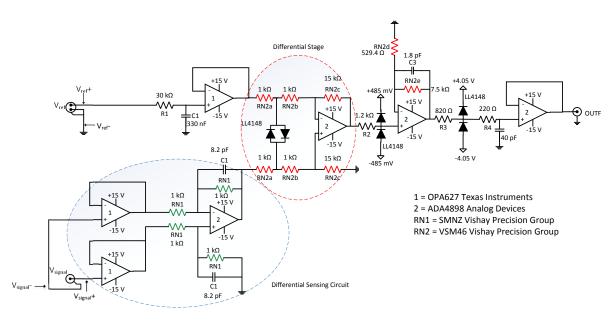

The final version of the reference acquisition system is composed of an improved analogue front-end (Fig.2.6), and the state-of-the-art acquisition board *NIPXI* – 5922.[5]

# 2.4 Design Enhancement

The new performance requirements were satisfied mainly by using the two circuits highlighted by dotted circles in Fig.2.6. The first circuit, highlighted in red, exploits an array (*RN2*) of matched resistors with 0.01% of relative tolerance with the following advantages:

- considerably enhance *CMRR* [36] by reducing the possible unbalance of the two branches of the differential stage (red dotted circle in Fig.2.6).

- stabilize gain by integrating all the temperature-sensitive gain-setting resistors into the same chip.

The second circuit, highlighted in blue, uses a differential sensing circuit on the input stage, with the following twofold advantages:

- rejection of the common-mode voltage between the analogue front-end and the upstream voltage divider, [5] which could arise from the ground loop between the two different grounds, by means of another high-precision resistors network *RN*1 with 0.01% of relative tolerances.

- complete decoupling of the voltage divider from the analogue front-end by means of two input buffers.

# **3** The On-line Acquisition System

## 3.1 Overview

In this chapter, the design of a  $\pm 18 \, ppm$  repeatable digitizer, with real-time delay less than  $1.2 \, \mu s$  and  $0 - 11 \, V$  full-scale range, is presented.

In particular, in section 3.2, the system requirements are defined, whereas in section 3.3, the working principle is discussed. In section 3.4, the design choices are detailed and the circuital realization of the prototype produced at *CERN* is presented. Then, in Chapter 6 (section 6), simulation tests aimed at verifying the design choices are presented. Finally, in Chapter 9 (section 10), the experimental results of an experimental proof of principle are reported and discussed.

# 3.2 Requirements for CLIC

In a real-time control of power converters for the last generation of particle accelerators, a digital control loop is exploited to guarantee the requested performance of the power system. In this section, the requirements of the real-time measurement sub-system for digital control loop are discussed with the specific case study of the new linear electron-positron particle accelerator currently under study at *CERN*, the Compact LInear Collider (*CLIC*) [11].

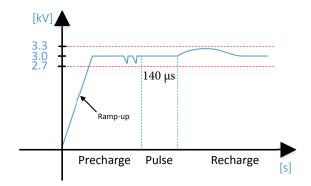

*CLIC* will allow collisions up to several TeV, exploring energy regions never reached before, thanks to its unprecedented combination of high energy and experiment precision. In order to reach the desired energy level, together with reasonable power consumption from the electrical grid, *CLIC* power converters [13] are demanded to deliver a pulsed power repeatable in the order of few tens of ppm [14]. To do that, a high-voltage modulator is currently under design by the laboratory for high-power electronics at *ETH Zurich (CH)* [16] and the *LEEPCI* Laval (CA) [17]. The latest topology of the ETH design is depicted in Fig.3.1. The modulator is composed by a charging system which, after a pre-charge phase, accumulates energy from the grid obtaining a nominal 3 *kV* output voltage. The switching unit allows the stored energy to be

released during 140  $\mu$ s, obtaining a pulse train on the primary side of a split-core transformer at a repetition rate of 50 *Hz*. The charging system output voltage is also regulated by an active bouncer for mitigating the effect of discharge of the capacitors bank during the pulses. Finally, on the secondary side, the pulses are amplified up to 180 *kV* directly feeding the klystrons. A high-voltage divider [34] is used to convert the 3 *kV* voltage into 10 *V* in order to be handled by a suitable real-time digitizing system. In this context, the system measures and provides a suitable adjustment value for the switching unit input voltage sketched in Fig.3.2.

#### 3.2.1 Measurand

The measurand signal is characterized by different phases: (i) an *initial ramp up*, in which the charging system reaches the nominal voltage, (ii) a *pulse*, during which the modulator generates the pulse ideally keeping the voltage constant, and (iii) a *recharge*, in which the nominal voltage out of the charging system is restored. The full performance specification concerns only the *Pulse* phase, though the measurement of the complete signal is required. This poses a crucial challenge on how to guarantee the required performance on the high-state, during the *Pulse*, while measuring a wide-range signal in real time. Furthermore, the switched-mode power converter generates a switching noise superposed on the measurand which must not jeopardize the final performance of the measurement system.

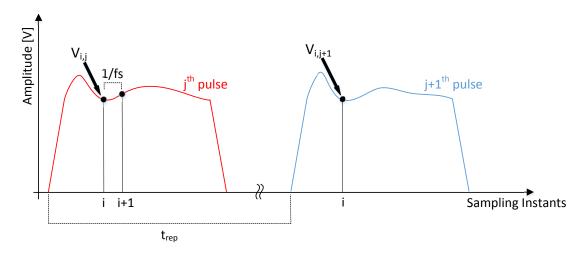

#### 3.2.2 Repeatability

The real-time measurement system will be used to guarantee a modulator repeatability in the order of  $\pm 50 \ ppm$  of full-scale during the pulse. The particular application, discussed in [5], defines a Pulse-to-Pulse Repeatability (*PPR*) as:

$$PPR = max|V_{i,j} - V_{i,j+1}|$$

(3.1)

where  $V_{i,j}$  and  $V_{i,j+1}$ , sketched in Fig.3.3, are the instantaneous voltage values in the *same* (in equivalent time) sampling instant *i* between two consecutive pulses on the secondary side of the modulator, namely  $j^{th}$  and  $j^{th} + 1$ . For the charging system this definition applies to the *Pulse* phase. In addition, to be able to properly measure and correct variations of 50 *ppm*, the

Figure 3.1 - Topology of the High-Voltage Modulator under design at ETH Zurich

Figure 3.2 – Switching Unit Input Voltage

Figure 3.3 - Pulse-to-Pulse Repeatability Definition.

system should have better repeatability performance. Thus, target instrument *PPR* was set to better than 50 *ppm*. It has been studied in [5] that if the instrument has a suitable stability within the pulses period, (20 *ms*), noise is the only factor affecting repeatability, thus all long term effects can be neglected (e.g. temperature drift).

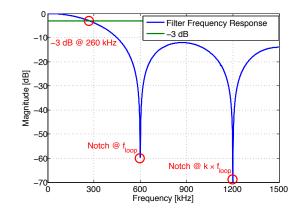

### 3.2.3 Throughput and Bandwidth

The digital control loop will run at a rate  $f_{loop} = 600 \ kS/s$  and the instrument must deliver one sample at each control loop period (*throughput* =  $f_{loop}$ ).

### 3.2.4 Delay

Delay is one of the most important parameters of a digital control loop. For this system, a total group delay  $d < 1.2 \ \mu s$  is specified for the whole measurement chain sketched in Fig.3.4 (high-voltage divider, analogue front-end, ADC, and digital filtering). In the following, for the sake of simplicity, the group delay at  $f = 0 \ Hz$  is called delay. This is a challenging specification when combined with an overall bandwidth of less than 300 kHz, as required by *CLIC* application.

In Table 3.1, the main requirements for the real-time measurement system are summarized.

Figure 3.4 - Definition of Delay in a Power Converter Real-time Data Acquisition

| Parameter                  | Symbol           | Value    |

|----------------------------|------------------|----------|

| Repeatability during Pulse | Rep <sub>p</sub> | 50 ppm   |

| Repeatability elsewhere    | Rep              | <1%      |

| Throughput                 | Т                | 600 kS/s |

| Bandwidth                  | BW               | >200 kHz |

| Delay                      | d                | < 1.2 µs |

Table 3.1 – Main Requirements

# 3.3 Design

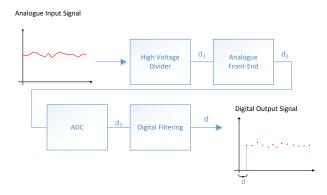

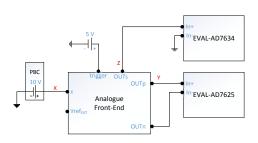

In this section, the design choices of the proposed instrument (Fig.3.5) are discussed with respect to the defined requirements.

## 3.3.1 Basic Principle

The 3 kV voltage is converted into 10 V by means of a high-voltage divider [34]. During the pre-charge phase, where no particular precision is required (<  $\pm 1$ %), the switch  $S_2$  allows subtracting the input signal from itself in order to obtain a *zero-signal* (ideally) on the upper branch of Fig.3.5. At the same time, a wide-range ADC, (*ADC*<sub>2</sub>) digitizes the input signal

Figure 3.5 - Measurement System Block Diagram

obtaining a coarse measurement of the initial ramp. When the ramp is over (this event will be identified by an external trigger provided by ETHz modulator), the switch commutates toward an internal reference 10  $V_{DC}$  voltage. This is subtracted from the signal in order to center its high-state around zero and then amplify only the part where high-precision is required by a factor *G* to best fit  $ADC_1$  range. Down-stream of these two operations, unwanted offset ( $O_x$  in Fig.3.5) and gain errors will arise from all the possible analogue components. All the nonideality effects will be processed digitally in order to properly reconstruct the original signal. A switch allows an external 10  $V_{DC}$  reference ( $Vref_{EXT}$ ) to be connected, for a direct calibration of the internal generated reference  $Vref_{INT}$ .

#### 3.3.2 Full-Signal Reconstruction

During normal working conditions, both the conditioned signal and the internal reference *DC* voltage are digitized ( $y_d$  and  $V_d$ , respectively, in Fig.3.5). These two signals are affected by the noise of (i) the front-end ( $n_{FE}$ ), (ii) the 10  $V_{DC}$  reference ( $n_{REF}$ ), and (iii) the two *ADCs* quantization, respectively  $n_1$  and  $n_2$ . In order to reconstruct the original input signal, offset and gain introduced into the analogue path as a whole have to be measured and digitally compensated. At this point, the resulting signals  $y_m$  and  $V_d$  are the digitized product of the original signal x:

$$x_{m} = \frac{[x - (V_{REF}^{INT} + n_{REF} + O\nu)] \cdot G + Ox + n_{FE} + n_{1} - Ox^{m}}{G^{m}} + V_{REF}^{INT} + n_{REF} + O\nu + n_{2}$$

(3.2)

Gain and offset can be accurately measured so that  $Ox^m = Ox$ ,  $G^m = G$  (full uncertainty estimation not discussed here) and:

$$x_{m} = x - V_{REF}^{INT} - n_{REF} - Ov + \frac{n_{FE} + n_{1}}{G^{m}} + V_{REF}^{INT} + Ov + n_{2} = x + \left(\frac{n_{FE} + n_{1}}{G^{m}}\right) + (n_{REF} + n_{2})$$

(3.3)

where all the deterministic errors have been already compensated.

In conclusion, particular attention should be paid to (i) accurately measure gain and offset for proper compensation, (ii) realize a low-noise front-end in order to keep  $n_{FE}$  as low as possible, (iii) heavily filter  $n_{REF}$ , and (iv) use high-resolution *ADCs* such that  $\frac{n_1}{G}$  and  $n_2$  meet the specs.

## 3.3.3 Sampling and Filtering Strategy

The digital control loop will run at 600 kS/s. To mitigate the ripple produced by power switching, an oversampling [37], filtering, and decimation strategy was adopted in this design. The sampling rate is defined as  $f_s = N \cdot 600 \ kS/s$ , where N is the oversampling ratio. In order to not produce significant aliasing, the instrument must be equipped with anti-aliasing

Figure 3.6 – Frequency Response of the Average 4<sup>th</sup> FIR filter

analogue and digital filters. Analogue filtering have to mitigate the effect of noise in the range of frequencies folding in base-band (above Nyquist frequency). In the current application, no relevant noise components are expected at high frequency (except from swithcing harmonics), thus an attenuation in the order of 10 *dB* at  $f_N = N \cdot f_{loop} - \frac{f_{loop}}{2}$  was considered for the design of the analogue front-end. It is worth noting that the upstream high-voltage divider, assumed as a first order filter at 1 *MHz*, already plays a role in the analogue anti-aliasing filtering strategy, accordingly introducing additional attenuation at  $f_N$ . For digital filtering, a simple average filter, belonging to the class of linear-phase *FIRs*, is foreseen. The frequency response of a 4<sup>th</sup> order filter, depicted in Fig.3.6 (N = 5 => sampling rate  $f_s = 3$  *MS/s*, and  $f_N = 2.7$  *MHz*) shows a notch at 600 *kHz* (and harmonics), with the important advantage of heavily mitigating the switching ripple of the power stage at those frequencies. The group delay introduced by this filter can be estimated as:

$$d_{digital} = \frac{N-1}{2Nf_{loop}} \approx 670\,ns\tag{3.4}$$

where *N* is the number of coefficients. In this case, a group delay in the order of 670 *ns* is calculated.

#### 3.3.4 ADC Noise vs Analogue Noise

Equation (3.3) states the dependence of the reconstruction quality of *x* on both the analogue  $(n_{FE} \text{ and } n_{REF})$  and the digital noise  $(n_1 \text{ and } n_2)$ . In [8], an analytical model for describing the statistical distribution of the worst-case *PPR*, namely the Worst-Case Repeatability (*WCR*), of an instrument affected by an Additive White Gaussian Noise (*AWGN*) was found. This happens typically when the analogue noise *AWGN* is adequately dominant with respect to the quantization noise of the ADC, assumed to be uniformly distributed between  $\frac{-\Delta}{2}$  and  $\frac{\Delta}{2}$ , where  $\Delta$  is the *ADC LSB*. On the contrary, if the quantization noise is dominant with respect to analogue noise, the *WCR* cannot be higher than  $\Delta$  itself.

In the following, the dominating noise contributions (analogue and digital) are discussed.

Quantization noise of  $ADC_1$ , which has to digitize the *high-state* signal. The high-speed ADC AD7625, declares a *SINAD* of 92 *dB*. The Effective Number Of Bits (*ENOB*) is calculated as:

$$ENOB = \frac{SINAD - 1.76}{6.02} \approx 14.9$$

(3.5)

The signal voltage swing *V*.*S*. is  $\pm 4 V$ , thus the *LSB* of *ADC*<sub>1</sub>, denoted by  $\Delta_1$ , can be obtained as:

$$\Delta_1 = \frac{V.S.}{2^{ENOB} G \times 10 \,\mu V} \approx \frac{246 \,\mu V}{40 \,\mu V} \approx 6.2 \,ppm \tag{3.6}$$

$n_2$

Quantization noise of  $ADC_2$  which has to digitize a 10  $V_{DC}$  voltage. As an example, the 18-bits AD7634 can be triggered to sample at 600 kS/s over an input voltage range of 10 V. In this conditions, AD7634 has a SINAD of 100 dB, thus its ENOB specification turns out to be  $\approx$  16.3 from (3.5) and, consequently, the LSB is about  $\Delta_2 \approx 12.4 ppm$ .

#### **Analogue Noise**

$n_{REF}$  is the noise arising from the *DC* reference voltage to be subtracted from the original signal. Since no bandwidth is required for this branch of the front-end, this voltage can be heavily filtered in order to reduce  $n_{REF}$ . Finally,  $n_{FE}$  is the noise of the analogue front-end. A low-noise solution for the front-end was indeed one of the main design constraints.

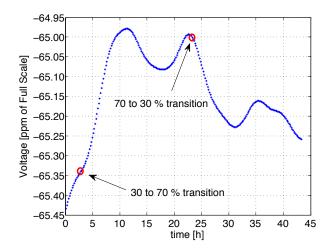

#### Worst-Case Repeatability

At the required bandwidth, the front-end's noise is expected to be lower than the quantization noises of the two ADCs. Under the assumption of uniformly-distributed quantization noises for the two ADCs, a deterministic superior bound for the *WCR* can be estimated. In fact, from (3.1), the worst-case condition is verified when the  $j^{th}$  acquisition is affected by the quantization noise  $\left(\frac{\Delta_1}{2} + \frac{\Delta_2}{2}\right)$  and the  $(j+1)^{th}$  by  $-\left(\frac{\Delta_1}{2} + \frac{\Delta_2}{2}\right)$ . Thus, the superior bound can be assessed as:

$$WCR = \Delta_1 + \Delta_2 \approx 18.6 \ ppm, \tag{3.7}$$

which is comfortably lower than the 50 *ppm* requirement. It is worth noting that, even if the low-noise feature of the analogue front-end is not critical in this application, by modifying the analogue filters parameters, the instrument can be adapted to applications where wider bandwidth is required, by accordingly taking advantage of the low-noise front-end.

$n_1$

Figure 3.7 - Analogue Front-End Schematics

# 3.4 Physical Design of the Analogue Front-End