UNIVERSITÀ DELLA CALABRIA

Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica

XXII ciclo

Tesi di Dottorato

Delivery the common sense of the time to synchronize Measurement Instruments co-operating into the DMS

> Francesco Lamonaca Frances es Sermonace

Coordinatore Prof. Luigi Palopoli

Supervisore Prof. Domenico Grimaldi

DIPARTIMENTO DI ELETTRONICA, INFORMATICA E SISTEMISTICA Settore Scientifico Disciplinare: ING-INF/07

To my parents.

### Abstract

This research is devoted to investigate the coordination in the time domain of the operations executed by the Measurement Instrument (MI) connected to the nodes of the Distributed Measurement System (DMS) by Hardware Interface (HI).

On the basis of the synchronization procedures of the node clocks of the DMS presented in the literature, the HIs can work on a synchronized modality. Nevertheless, the hardware and software architecture of the path involved in the communication HI-MI can randomly time delay the commands.

Often in the DMS the PC is used as HI. In this case two different aspects are taken into account: (i) the characterization of the hardware connection PC-MI offering the minimum time delay, and (ii) the criteria to modify and to set up the software to reduce the random time delay occurring in the processing steps performed into the PC.

The results of the research performed highlights that the main cause of random time delay is the concurrency of the processes running in the PC. In particular, the delay depends on: (i) number of concurrent processes, (ii) their priority, (iii) behavior of the kernel managing the concurrency.

In order to overcome the delay caused, the HI based on the Programmable Logic Device (PLD) is taken into account and proposed in the place of the PC. From the analysis of the operations executed on the PLD, operating conditions are shown, making random variation of the synchronization time delay of the MI to the node clock. In order to detect the causes of the random variation, the polling cycle is taken into account and analyzed. From this analysis the model of the uncertainty affecting the synchronization time delay is pointed out in order to evaluate the effects of each cause affecting the trigger check. The result of this evaluation furnishes: (i) information to point out the adequate strategy to reduce the random time variation of the detection of the trigger condition, and (ii) requirements to completely avoid the polling cycle. The experimental tests performed by using implemented embedded HI assess the efficacy of the presented HI to achieve sub-microsecond synchronization accuracy, according to the standard IEEE 1588. In the research the problem of the stand alone MIs is also taken into account. In some cases, indeed, synchronized measurement procedures must be performed in places where the node of the DMS are not reachable, or not convenient to reach, by wired or wireless connections. For this reason it is not possible to use standard synchronization protocol to synchronize the MIs. In these cases the use of the Personal Digital Assistant (PDA) is proposed to physically bring the common sense of time to the stand alone MI. In order to achieve synchronization accuracy in the order of sub-microsecond, it is presented the conjunct use of the PDA and the proper embedded HI. This solution meets the advantages of both the devices. The PDA permits the advantages of the high level programming languages in order to interface the MI and collect the data. The embedded HI guarantees high synchronization accuracy on the basis of the deterministic behavior of the proposed hardware architecture. Experimental tests confirm the suitability of the proposed solution to the requirements of the standard IEEE 1588.

#### VIII

### Sintesi

L'attività di ricerca è rivolta allo studio del coordinamento nel dominio del tempo delle operazioni eseguite dagli Strumenti di Misura (SM) connessi ai nodi del Sistema Distribuito di Misura (SDM), tramite Interfaccia Hardware (IH).

Sulla base delle procedure di sincronizzazione dei nodi del SDM presenti in letteratura, le IH possono operare in modalità sincrona. Tuttavia, le architetture hardware e software del collegamento tra IH e SM possono ritardare i comandi inviati allo SM.

Spesso nei SDM il PC è usato quale IH. In questo caso due differenti aspetti sono presi in considerazione: (i) la caratterizzazione della connessione hardware PC-SM che offre il minimo ritardo di comunicazione e (ii) il criterio per modificare e settare il software eseguito dal PC per ridurre l'aleatorietà del ritardo introdotto dall'esecuzione del processo di interfacciamento SM-SDM.

I risultati della ricerca hanno evidenziato che la principale causa di aleatorietà del ritardo è la concorrenza tra i processi che condividono le risorse del PC. In particolare, tale ritardo dipende: (i) dal numero dei processi concorrenti, (ii) dalla loro priorità di esecuzione, (iii) dal comportamento del kernel nella gestione della concorrenza. Al fine di ridurre l'influenza di tale causa di ritardo, è stata presa in considerazione l'IH basata su Programmable Logic Device (PLD) e proposta in sostituzione del PC. Dall'analisi delle operazioni eseguite sul PLD, sono state evidenziate condizioni operative che rendono aleatorio il ritardo di sincronizzazione introdotto da questo tipo di interfaccia. Al fine di rilevare tali cause è preso in considerazione ed analizzato il ciclo di polling per la verifica della condizione di trigger, cioè di inizio esecuzione della misura. Sulla base di tale analisi è stato messo a punto il modello matematico dell'incertezza associata al ritardo di sincronizzazione. Cio' ha consentito di valutare l'effetto di ogni causa che rende aleatorio il rilevamento della condizione di trigger. Il risultato di tale analisi fornisce: (i) informazioni per mettere a punto adeguate strategie per ridurre l'aleatorietà del tempo in cui è rilevata la condizione di trigger, e (ii) indicazioni per progettare ed implementare IH dedicata che eviti completamente il ciclo di polling. Test sperimentali

dimostrano che l'uso di IH dedicata garantisce livelli di sincronizzazione tra le misure distribuite nell'ordine del sub-microsecondo. Tale risultato soddisfa le specifiche dello standard IEEE 1588.

Nella ricerca è stato preso in considerazione anche il caso di SM isolati. Infatti, misure sincronizzate possono essere eseguite in luoghi dove non è presente e/o dove non è conveniente installare una rete di comunicazione wired o wireless. Per tale ragione non è possibile applicare le tecniche di sincronizzazione presenti in letteratura. Per questi casi è proposto l'uso del Personal Digital Assistant (PDA) per trasportare il senso comune di tempo allo SM isolato. Al fine di ottenere livelli di sincronizzazione inferiori del microsecondo, è proposto l'uso congiunto del PDA e IH dedicata. Tale soluzione si avvale dei vantaggi del PDA per quanto riguarda la facilità di realizzazione del software di interfacciamento dello SM tramite l'uso di linguaggi di programmazione di alto livello, e quelli dell' IH dedicata per quanto riguarda l'accuratezza di sincronizzazione. Test sperimentali confermano che la soluzione proposta soddisfa i livelli di accuratezza richiesti dallo standard IEEE 1588.

## Acknowledgments

I would like to express my gratitude to my tutor, Professor Domenico Grimaldi, for his academic guidance, critiques of my ideas, emotional support, suggestions, and encouragement. My research could not have been finished reasonably without insightful advice from him.

Special tanks to my friends En. Domenico Luca Carnì and En. Emanuele Garone with whom I spent several time in the laboratory and shared the burden of these years.

Thanks to all my friends, they are too many because I can cite all them.

Finally, I am deeply grateful to my family for its love, support, and patience during these years. This thesis would not have been possible without its support and confidence. This thesis is dedicated to my parents, Savino and Raffaelina and to my brother Antonio. They always encouraged and believed in me.

## Contents

| Ab       | strac                     | $\mathbf{t}$                                                    |

|----------|---------------------------|-----------------------------------------------------------------|

| Sin      | tesi .                    | IX                                                              |

| Ac       | know                      | ledgments XI                                                    |

|          | Cor                       | itentsXII                                                       |

|          | List                      | of FiguresXV                                                    |

|          | List                      | of Tables                                                       |

| 1        | <b>Intr</b><br>1.1<br>1.2 | roduction1Motivations and goals1Thesis outline5                 |

| <b>2</b> | $\mathbf{Syn}$            | chronization Techniques                                         |

|          | 2.1                       | Introduction                                                    |

|          | 2.2                       | Techniques to synchronize clocks                                |

|          | 2.3                       | Synchronization by using GNSS                                   |

|          |                           | 2.3.1 GPS                                                       |

|          |                           | 2.3.2 GLONASS 12                                                |

|          |                           | 2.3.3 GALILEO 12                                                |

|          |                           | 2.3.4 Limits of the synchronization techniques based on GNSS 13 |

|          | 2.4                       | Synchronization based on internet 14                            |

|          |                           | 2.4.1 NTP 14                                                    |

|          |                           | 2.4.2 IEEE 1588 15                                              |

|          | 2.5                       | Comparison among synchronization procedures 16                  |

|          | 2.6                       | The open questions                                              |

|          | 2.7                       | Conclusions                                                     |

| 3 | Dela           | ay in the Path PC-MI                                           | 21              |

|---|----------------|----------------------------------------------------------------|-----------------|

|   | 3.1            | Introduction                                                   | 21              |

|   | 3.2            | Mathematical model of the delay in the path PC-MI              | 22              |

|   | 3.3            | Features of the realized test beds                             | 24              |

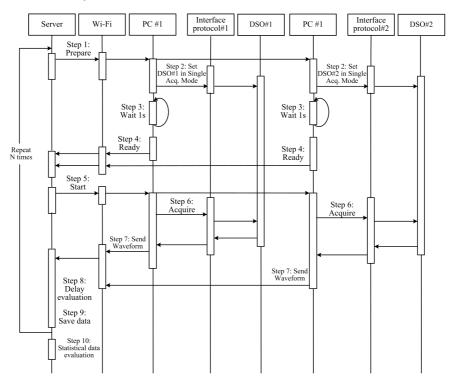

|   |                | 3.3.1 The reference signal                                     | 26              |

|   |                | 3.3.2 Operation performed in the DMS                           | 26              |

|   |                | 3.3.3 Consideration on the trigger event                       | 28              |

|   |                | 3.3.4 Consideration on the OS equipping the client PC          | 29              |

|   | 3.4            | Experimental tests to evaluate the connection PC-MI            |                 |

|   |                | assessing minimum time delay                                   | 29              |

|   |                | 3.4.1 First case study: Virtual GPIB and Windows OS            | 30              |

|   |                | 3.4.2 Second case study: GPIB-USB adapter and Windows          |                 |

|   |                | OS                                                             | 31              |

|   |                | 3.4.3 Third case study: GPIB-USB adapter and Linux OS          | 31              |

|   |                | 3.4.4 Fourth test: External Trigger and Linux OS               | 31              |

|   | 9 5            | 3.4.5 Discussion on the experimental results                   | 33              |

|   | 3.5            | Experimental tests to evaluate the delay caused by the DSOs .  | 34              |

|   | $3.6 \\ 3.7$   | Delay introduced by PCs<br>Conclusions                         | $\frac{36}{39}$ |

|   | 3.7            | Conclusions                                                    | 39              |

| 4 | Red            | uction of the Synchronization Time Delay by Linux              |                 |

|   |                | Setting Up                                                     | 41              |

|   | 4.1            | Introduction                                                   | 41              |

|   | 4.2            | Time delay analysis in the path PC-MI with wireless connection | 42              |

|   | 4.3            | Setting up of Linux OS                                         | 43              |

|   | 4.4            | Changes in the software driver of the WiFi receiver            | 46              |

|   | 4.5            | Performance analysis by Linux OS RT                            | 49              |

|   | 4.6            | Performance analysis by RTnet                                  | 51              |

|   |                | 4.6.1 RTnet                                                    | 51              |

|   |                | 4.6.2 Lan                                                      | 51              |

|   |                | 4.6.3 Lan Real Time                                            | 53              |

|   |                | 4.6.4 Wireless Lan                                             | 54              |

|   |                | 4.6.5 Wireless Lan Real Time                                   | 55              |

|   |                | 4.6.6 Discussion on the experimental results                   | 57              |

|   | 4.7            | Validation of the deterministic OS performances by using       | 50              |

|   | 1.0            | different MI                                                   |                 |

|   | 4.8            | Conclusions                                                    | 00              |

| 5 | $\mathbf{Syn}$ | chronization of MI by Using Industrial Hardware                | 63              |

|   | 5.1            | Introduction                                                   | 63              |

|   | 5.2            | Interaction between polling cycle and incoming trigger         | 64              |

|   | 5.3            | Model of the synchronization time delay                        | 65              |

|   | 5.4            | Software solutions reducing the execution time of the polling  |                 |

|   |                | cycle                                                          | 69              |

|   | 5.5            | Experimental tests                                             | 73              |

| Contents     | XV |

|--------------|----|

| 0.0110.01100 |    |

|     | 5.6          | Conclusions                                                 | 75       |

|-----|--------------|-------------------------------------------------------------|----------|

| 6   | -            | chronization of MI by Using Embedded Hardware               | 77       |

|     | 6.1          | Introduction                                                | 77       |

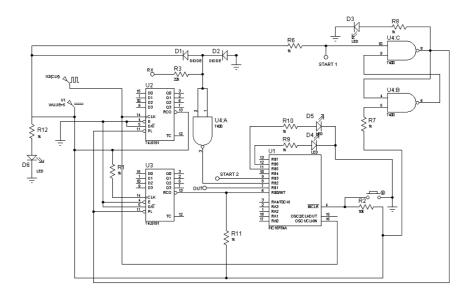

|     | 6.2          | Performed operation by proposed HI                          | 78       |

|     | 6.3          | Synchronization by means of proposed HI                     | 80       |

|     | 6.4          | Model of random variation of the synchronization time delay | ~ ~      |

|     | ~ -          | by using the proposed HI                                    | 80       |

|     | 6.5          | Actual realization of the proposed HI                       | 84       |

|     | 6.6          | Experimental tests                                          | 85       |

|     | 6.7          | Conclusions                                                 | 88       |

| 7   |              | iver the Common Sense of the Time by PDA to Stand           | 00       |

|     |              | ne MI                                                       | 89<br>80 |

|     | $7.1 \\ 7.2$ | Introduction<br>First synchronization procedure             | 89<br>91 |

|     | 7.2<br>7.3   | Outline of the optimized synchronization procedure          | 91<br>94 |

|     | 1.5          | 7.3.1 Synchronization phase                                 | 94<br>94 |

|     |              | 7.3.2 Operative phase                                       | 94<br>95 |

|     | 7.4          | Working by the optimized synchronization procedure          | 96       |

|     | 1.1          | 7.4.1 Shoot mode                                            | 98       |

|     | 7.5          | Experimental tests                                          | 98       |

|     |              | 7.5.1 Evaluation of the time stamp accuracy into PDA        | 98       |

|     |              | 7.5.2 Accuracy achievable by the two proposed               |          |

|     |              | synchronization procedures                                  | 101      |

|     | 7.6          | Conclusions                                                 |          |

| 8   | Sun          | chronizing Stand Alone MI by PDA and Embedded               |          |

| 0   |              | dware                                                       | 103      |

|     | 8.1          | Introduction                                                |          |

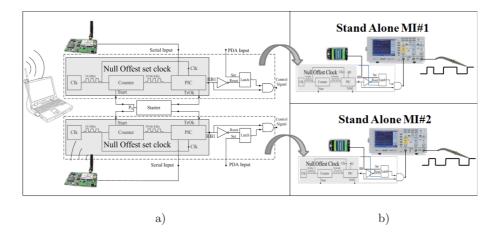

|     | 8.2          | Description of the proposed extended HI                     |          |

|     | -            | 8.2.1 Theoretical criteria to design ESH                    |          |

|     |              | 8.2.2 Actual realization of the ESH                         |          |

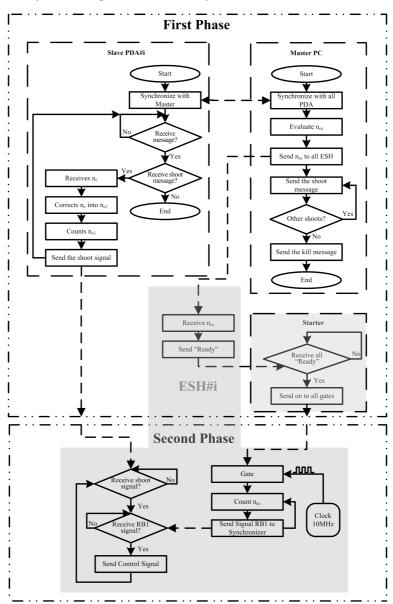

|     | 8.3          | Use of the extended HI                                      | 109      |

|     |              | 8.3.1 First phase: synchronization                          | 111      |

|     |              | 8.3.2 Second phase: measurement execution                   | 111      |

|     | 8.4          | Model of the synchronization time delay                     | 112      |

|     | 8.5          | Experimental tests                                          | 114      |

|     | 8.6          | Conclusions                                                 |          |

| Co  | nclus        | sions and Direction for Future Research                     | 117      |

| Ref | feren        | ices                                                        | 121      |

# List of Figures

| 2.1  | Clock time-keeping ability                                    | 9  |

|------|---------------------------------------------------------------|----|

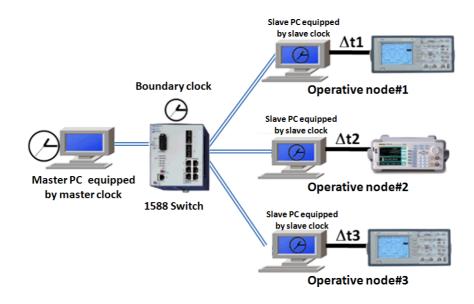

| 2.2  | Block scheme of synchronized DMS.                             | 17 |

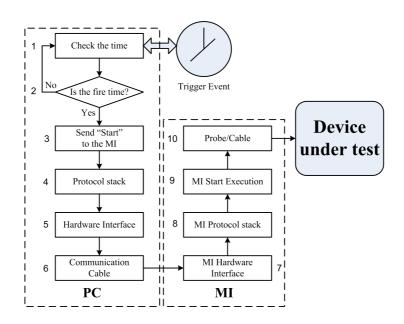

| 3.1  | Block scheme of the operation executed in the synchronized    |    |

|      | node of the DMS.                                              | 22 |

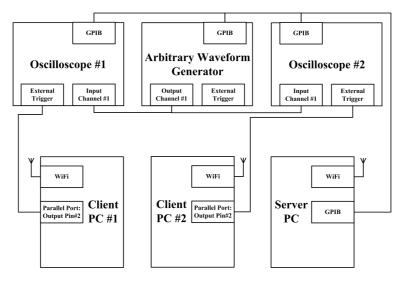

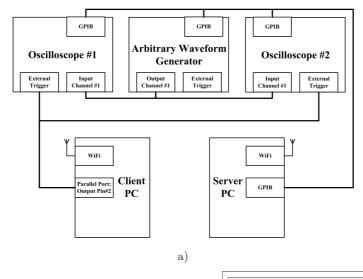

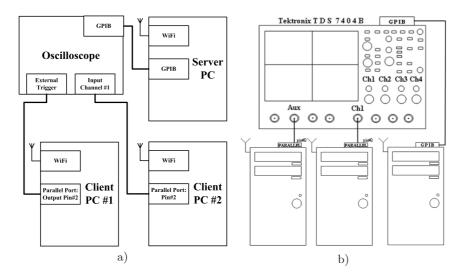

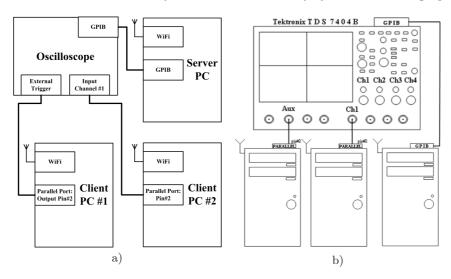

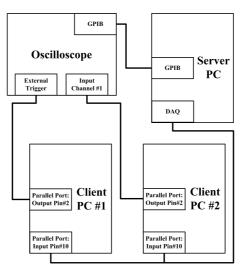

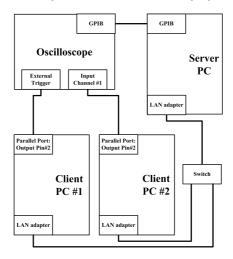

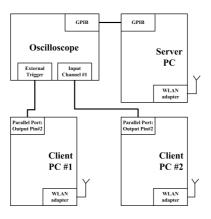

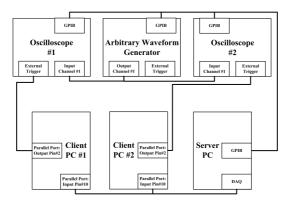

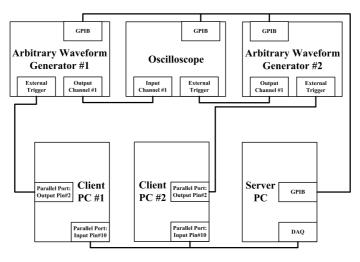

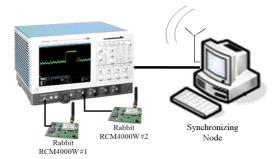

| 3.2  | Block scheme of the Wireless DMS realized in the laboratory   |    |

|      | to perform the experimental tests                             | 25 |

| 3.3  | Wireless DMS realized in the laboratory to perform the        |    |

|      | experimental tests.                                           | 25 |

| 3.4  | Common reference signal sent to the DSO to evaluate the       |    |

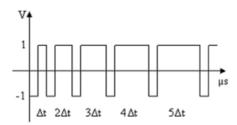

|      | synchronization time delay.                                   | 26 |

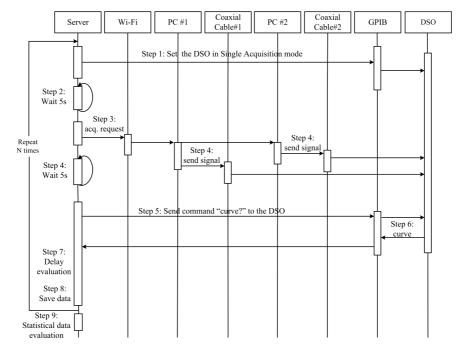

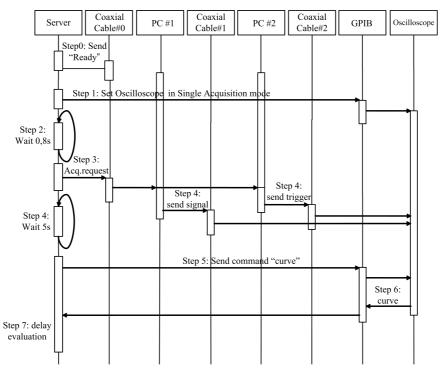

| 3.5  | Block scheme of the operations executed in the DMS            | 27 |

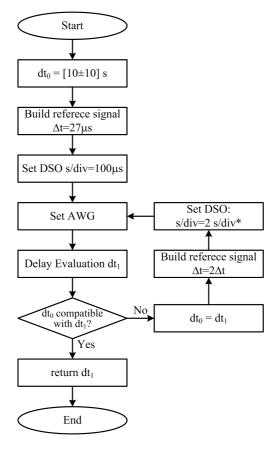

| 3.6  | Sequence of the operations executed in the DMS                | 28 |

| 3.7  | Block scheme of the DMS in which the communication            |    |

|      | between PC-MI is the Virtual-GPIB                             | 30 |

| 3.8  | Block scheme of the DMS in which the communication            |    |

|      | between PC-MI is the GPIB/USB hardware protocol converter.    | 31 |

| 3.9  | Block scheme of the DMS in which the communication            |    |

|      | between PC-MI is the GPIB/USB hardware protocol converter     |    |

|      | and both the slave PCs are equipped by Linux OS               | 32 |

| 3.10 | Block scheme of the DMS in which the communication            |    |

|      | between PC-MI is implemented via the External Trigger of      |    |

|      | the DSO and both the slave PCs are equipped with Linux OS     | 32 |

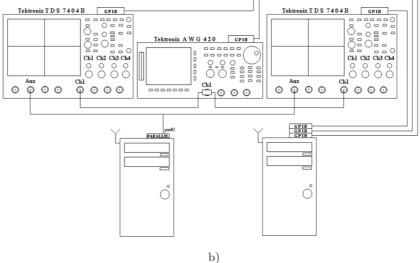

| 3.11 | a) Block scheme and b) actual realization of the experimental |    |

|      | set up to evaluate the delay caused by the hardware of the    |    |

|      | two DSOs                                                      | 35 |

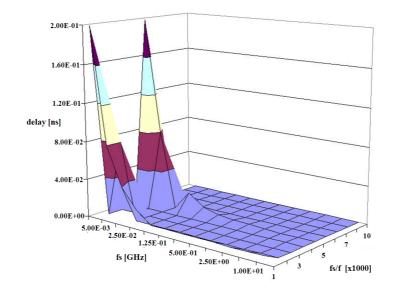

| 3.12 | Trend of the synchronization time delay versus fs and fs/f    | 36 |

| 3.13 | a) Block scheme and b) actual realization of the experimental |    |

|      | set up to evaluate the delay between the ramp generated at    |    |

|      | the $pin#2$ of the parallel port of each PC                   | 37 |

#### XVIII List of Figures

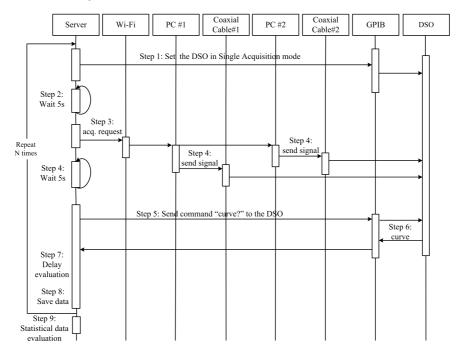

| 3.14 | Sequence of the commands planned to evaluate the delay<br>introduced by the PCs                                                                                               | 38         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

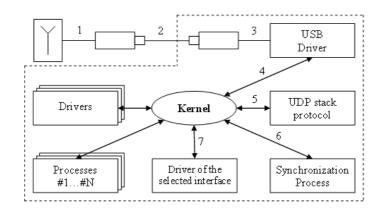

| 4.1  | Simplified block scheme specifying the delay sources in the communication process with the MI.                                                                                | 42         |

| 4.2  | a) Block scheme and b) actual realization of the experimental<br>set up to evaluate the delay between the ramp generated at                                                   | 72         |

| 4.3  | the pin $\#2$ of the parallel port of each PC<br>Sequence of the commands planned to evaluate the delay                                                                       | 44         |

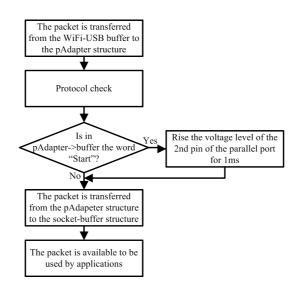

| 4.4  | introduced by the PCs<br>Processing block scheme of the signal received at the WiFi                                                                                           | 44         |

| 4.5  | interface                                                                                                                                                                     | $47 \\ 47$ |

| 4.6  | Experimental set up to evaluate the delay between the ramp generated at the $pin#2$ of the parallel port of each PC                                                           |            |

| 4.7  | equipped by Linux OS and Linux OS RT<br>Sequence of the commands planned to evaluate the delay                                                                                | 50         |

| 1.0  | introduced by the operating system Linux OS Knoppix Real<br>Time equipping the two PCs.                                                                                       | 50         |

| 4.8  | Experimental set up to evaluate the delay between the two<br>PCs, equipped by Linux OS and the UDP broadcast packet                                                           | 50         |

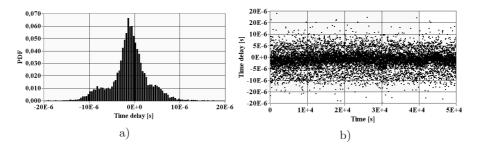

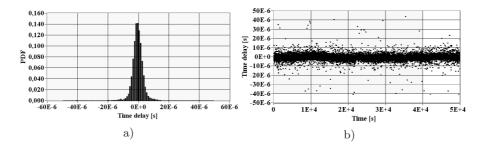

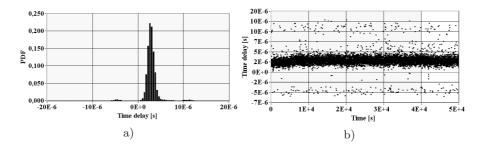

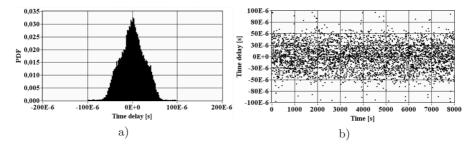

| 4.9  | sent by LAN is used as common trigger signal between node a) PDF and b) trend versus the time of the synchronization time dolay in the area the UDB broadcast packet is used. | 52         |

|      | time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the<br>transmission is by LAN and the occupancy of both the CPU   |            |

| 4.10 | nodes is 5%                                                                                                                                                                   | 52         |

| 4.10 | time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the                                                               |            |

|      | transmission is by LAN. The occupancy of one CPU is 5% and the other one is 100%.                                                                                             | 53         |

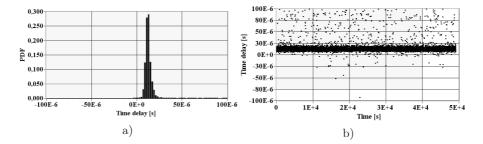

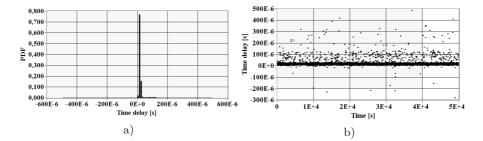

| 4.11 | a) PDF and b) trend versus the time of the synchronization<br>time delay in the case the UDP broadcast packet is used                                                         | 00         |

|      | as common trigger signal between nodes. Moreover the<br>transmission is by RT-LAN and the occupancy of both the                                                               |            |

| 4.12 | CPU nodes is 5%                                                                                                                                                               | 53         |

|      | time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the                                                               |            |

|      | transmission is by RT-LAN. The occupancy of one CPU is 5% and the other one is 100%.                                                                                          | 54         |

| 4.13 | Experimental set up to evaluate the delay between the two<br>PCs, equipped by Linux OS and the UDP broadcast packet                                                           |            |

|      | sent by WLAN is used as common trigger signal between node.                                                                                                                   | 54         |

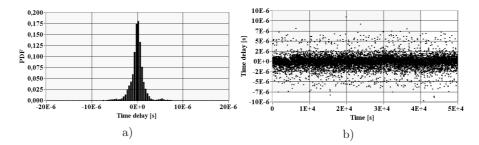

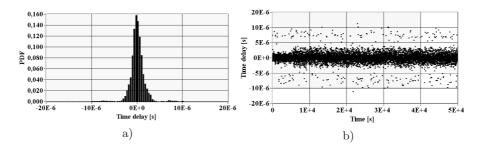

| 4.14       | a) PDF and b) trend versus the time of the synchronization<br>time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the                                                            |                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 4.15       | transmission is by WLAN and the occupancy of both the CPU nodes is 5%.                                                                                                                                                                   | 55               |

| 4.15       | a) PDF and b) trend versus the time of the synchronization<br>time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the<br>transmission is by WLAN. The occupancy of one CPU is 5% |                  |

|            | and the other one is 100%.                                                                                                                                                                                                               | 55               |

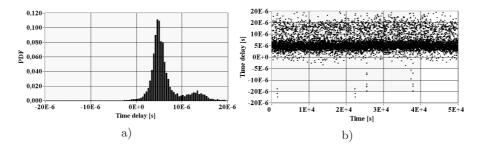

| 4.16       | a) PDF and b) trend versus the time of the synchronization<br>time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the<br>transmission is by WLAN. The occupancy of one CPU is 5% |                  |

|            | and the other one is 100%.                                                                                                                                                                                                               | 56               |

| 4.17       | a) PDF and b) trend versus the time of the synchronization<br>time delay in the case the UDP broadcast packet is used<br>as common trigger signal between nodes. Moreover the<br>transmission is by RT-WLAN. The occupancy of one CPU is |                  |

|            | 5% and the other one is 100%.                                                                                                                                                                                                            | 56               |

| 4.18       | Experimental set up to evaluate the delay between the two                                                                                                                                                                                |                  |

| 4 10       | PCs, equipped by Linux RT and connected to DSO.                                                                                                                                                                                          | 58               |

| 4.19       | Experimental set up to evaluate the delay between the two<br>PCs, equipped by Linux RT and connected to AWG                                                                                                                              | 60               |

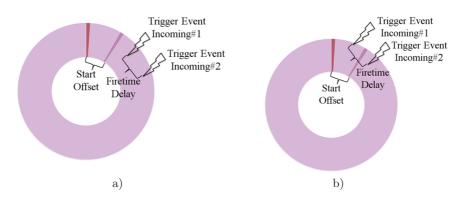

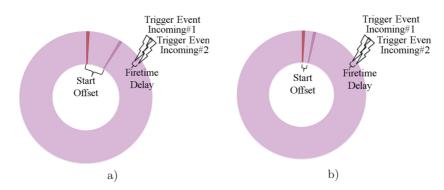

| 5.1        | a) Polling cycle on PLD#1 and PLD#2, respectively; b)                                                                                                                                                                                    |                  |

| 5.2        | overlap of the previous two polling cycles                                                                                                                                                                                               | 64               |

|            | case: the trigger occurs before the check on PLD#1 and after<br>on PLD#2                                                                                                                                                                 | 65               |

| 5.3        | a) Uncertainty reduction of the incoming trigger can reduce<br>the probability that the worst case, occurs, b) the reduction<br>of the Start Offset can reduce the probability that the worst                                            |                  |

| <b>.</b> . | case, occurs.                                                                                                                                                                                                                            | 68               |

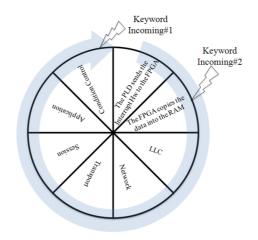

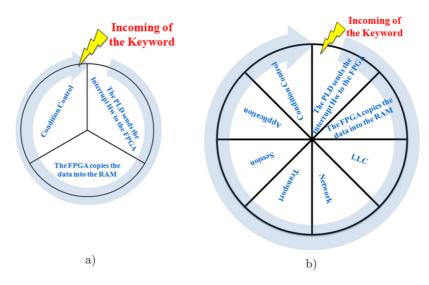

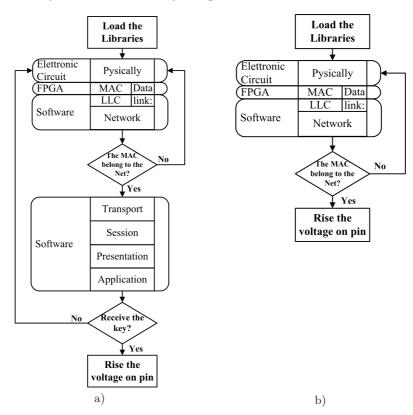

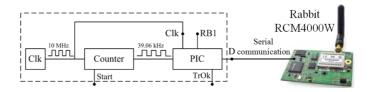

| 5.4        | Block scheme of the operations executed by the original control program running into the board Rabbit RCM4400W                                                                                                                           | 69               |

| 5.5        | Operations performed into the polling cycle                                                                                                                                                                                              | 0 <i>3</i><br>70 |

| 5.6        | Block scheme of the operations executed by the modified<br>control program running into the board Rabbit RCM4400W                                                                                                                        |                  |

|            | in order to reduce the time of the polling cycle                                                                                                                                                                                         | 70               |

| 5.7        | Operation executed when a) the worst case occurs, b) the best case occurs                                                                                                                                                                | 71               |

|            |                                                                                                                                                                                                                                          |                  |

#### XX List of Figures

| 5.8                                       | a) Block scheme of the operations executed by the control<br>program using the modified software driver. b) Block scheme<br>of the operations executed by the control program using the |          |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           | modified software driver in the case the sender signal is used                                                                                                                          | 70       |

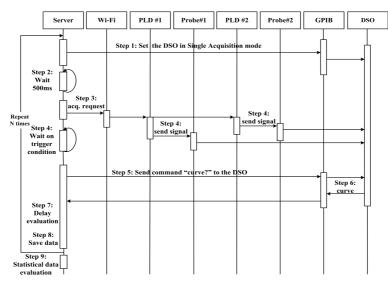

| 5.9                                       | only as wireless Trigger<br>DMS to evaluate the synchronization time delay introduced                                                                                                   | 72       |

| 0.5                                       | by the Rabbit RCM4000W                                                                                                                                                                  | 73       |

| 5.10                                      | Sequence of the commands planned to evaluate the delay                                                                                                                                  |          |

|                                           | introduced by the PLDs.                                                                                                                                                                 | 73       |

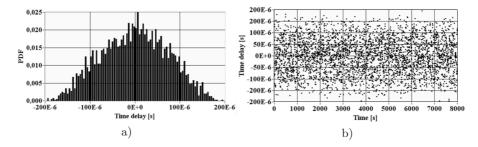

| 5.11                                      | a) Trend versus the acquisition time, and b) PDF of the synchronization time delay obtained applying the original                                                                       |          |

| - 10                                      | program.                                                                                                                                                                                | 74       |

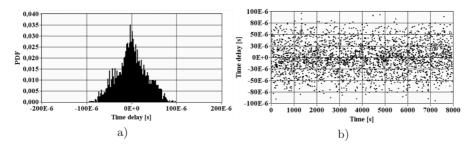

| 5.12                                      | a) Trend versus the acquisition time, and b) PDF of the                                                                                                                                 |          |

|                                           | synchronization time delay obtained applying the modified program.                                                                                                                      | 74       |

| 5.13                                      | a) Trend versus the acquisition time, and b) PDF of the<br>synchronization time delay obtained applying the modified                                                                    | 14       |

|                                           | software driver.                                                                                                                                                                        | 75       |

|                                           |                                                                                                                                                                                         |          |

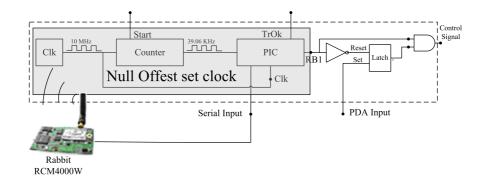

| 6.1                                       | Block scheme of the proposed HI architecture reducing the                                                                                                                               |          |

| <i>c</i>                                  | random time delay variation to check the trigger condition                                                                                                                              | 78       |

| 6.2                                       | a) Block scheme of the connection into the Synchronization<br>Bhase and b) block diagram of the performed expertion by                                                                  |          |

|                                           | Phase, and b) block diagram of the performed operation by<br>HI into the Synchronization Phase; c) block scheme of the                                                                  |          |

|                                           | connection into the Operative Phase for the synchronization of                                                                                                                          |          |

|                                           | two stand alone MIs, and d) block diagram of the performed                                                                                                                              |          |

|                                           | operation by HI into the Operative Phase                                                                                                                                                | 79       |

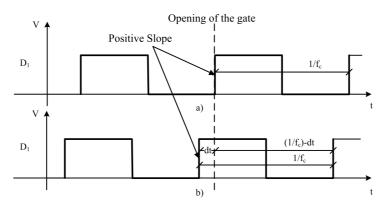

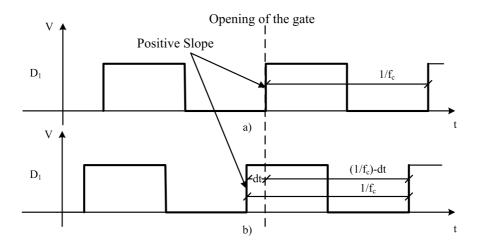

| 6.3                                       | Delay between the opening of the gate in the counter and the                                                                                                                            |          |

|                                           | effective start to count. In a) the best case occurs, and the                                                                                                                           |          |

|                                           | delay is zero. In b) the middle case occurs and the delay is                                                                                                                            | ~~~      |

| C A                                       | equal to $\frac{1}{f_c} - d_t$ .                                                                                                                                                        | 82       |

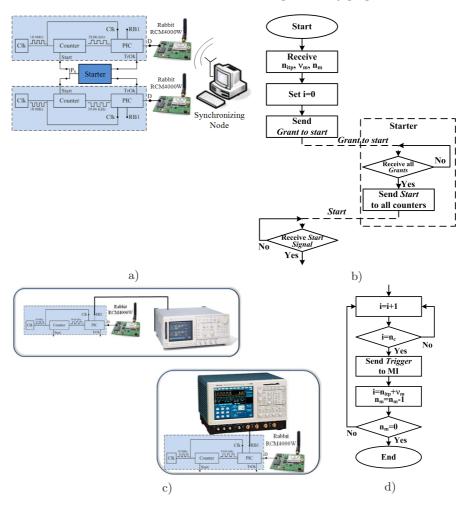

| $\begin{array}{c} 6.4 \\ 6.5 \end{array}$ | Block scheme of the HI<br>Block scheme of the HI and of the Starter Block                                                                                                               | 84<br>84 |

| 6.6                                       | Experimental set up to evaluate the delay between the trigger                                                                                                                           | 04       |

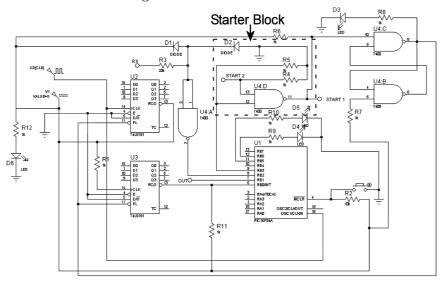

| 0.0                                       | signals generated by two HIs.                                                                                                                                                           | 86       |

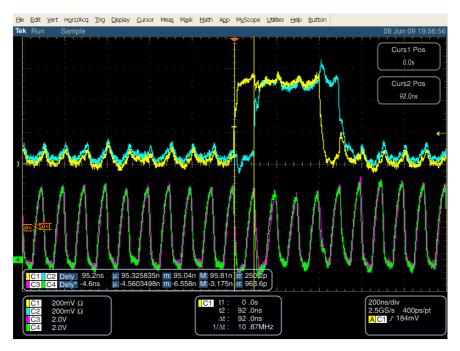

| 6.7                                       | Snapshot of the DSO to evaluate the delay between the trigger                                                                                                                           |          |

|                                           | signals generated by the HIs, in the case $f_{c1} = f_{c2}$ .                                                                                                                           | 87       |

| 6.8                                       | Snapshot of the DSO to evaluate the synchronization time                                                                                                                                |          |

|                                           | delay between the trigger signals generated by the HIs in the                                                                                                                           |          |

|                                           | case $f_{c1} \neq f_{c2}$ and a) $n_c = 574 * 10^7$ , b) $n_c = 582 * 10^7$ , c)                                                                                                        | 00       |

|                                           | $n_c = 600 * 10^7$ , d) and $n_c = 607 * 10^7$                                                                                                                                          | 88       |

| 7.1                                       | a) PDAs are synchronized to the synchronized node of the                                                                                                                                |          |

| • • =                                     | DMS, b) the PDAs bring the common sense of time to stande                                                                                                                               |          |

|                                           | alone MIs.                                                                                                                                                                              | 90       |

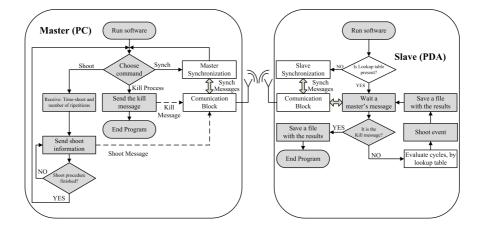

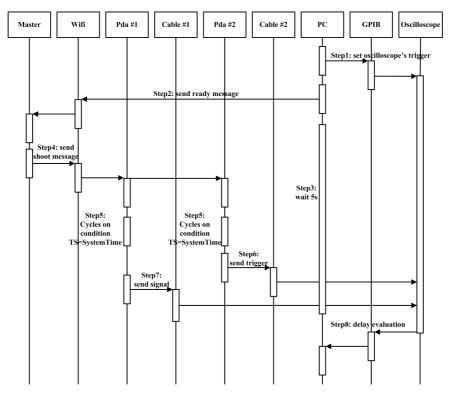

| 7.2 | Operations involving the Master PC, the PDA-Slave and the        |

|-----|------------------------------------------------------------------|

|     | interactions among them, on the basis of the first proposed      |

|     | synchronization procedure                                        |

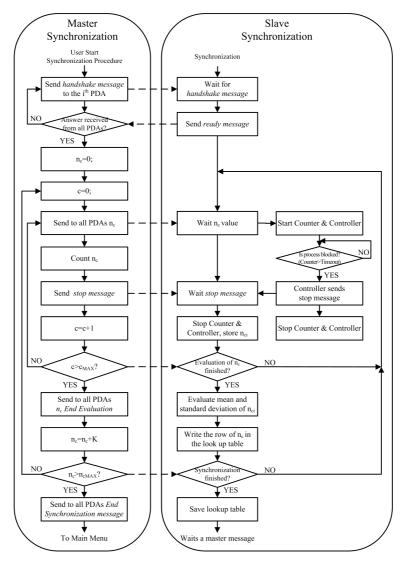

| 7.3 | Synchronization and unlock procedures                            |

| 7.4 | Block scheme of the interaction among the Master PC and the      |

|     | PDAs in order to perform the synchronization, and to operate     |

|     | in synchronized modality 95                                      |

| 7.5 | Synchronization procedure based on look up table and unlock      |

|     | procedures                                                       |

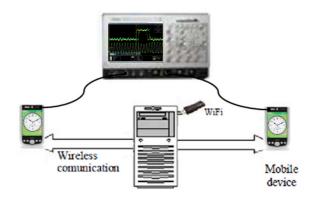

| 7.6 | Interaction among the two PDAs and the Master PC, and            |

|     | measurement of the time delay between the shoot time of the      |

|     | PDAs                                                             |

| 7.7 | Planned command sequence to evaluate the delay introduced        |

|     | by the two PDAs 100                                              |

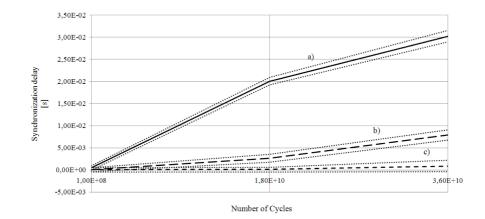

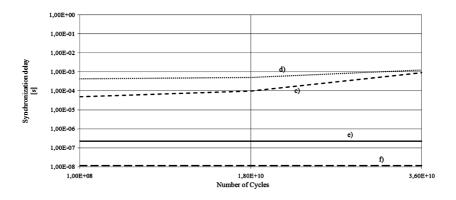

| 7.8 | Trend of the mean value and standard deviation of the            |

|     | synchronization time delay between the shoot time of the         |

|     | two PDAs versus the number of cycles (a) without the             |

|     | synchronization, (b) with the first synchronization procedure,   |

|     | and (c) with the optimized synchronization procedure 101         |

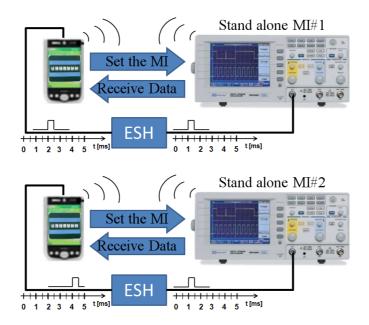

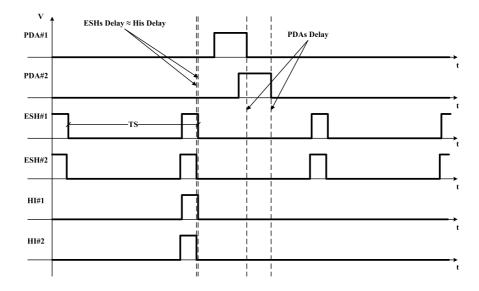

| 8.1 | Timing of the output signal of PDA#1, PDA#2, ESH#1,              |

| 0.1 | ESH#2                                                            |

| 8.2 | Timing of the Output signal of PDA#1, PDA#2, ESH#1,              |

| 0.2 | ESH $\#2$ , HI $\#1$ , HI $\#2$                                  |

| 8.3 | Timing of the output signal of $PDA\#1$ , $PDA\#2$ , $ESH\#1$ ,  |

| 0.0 | ESH#2, HI#1, HI#2. If the PDAs signals rises one before          |

|     | and the other after the rising signal of the two corresponding   |

|     | ESHs the worst case occurs and the HIs signals delay is equal    |

|     | at most to TS                                                    |

| 8.4 | Block scheme of the proposed ESH architecture                    |

| 8.5 | Block scheme of the proposed ESH architecture in the             |

| 0.0 | configuration corresponding to a) the First Phase in which       |

|     | the synchronization is performed and b) the second phase in      |

|     | which the HIs are used to interface the MI in order to perform   |

|     | the synchronized measure                                         |

| 8.6 | Block scheme of the performed operation by the proposed ESH. 110 |

| 8.7 | Delay between the opening of the gate in the counter and the     |

| 0.1 | effective start to count. In a) the best case occurs, and the    |

|     | delay is zero. In b) the middle case occurs and the delay is     |

|     | equal to $\frac{1}{t_c} - d_t$                                   |

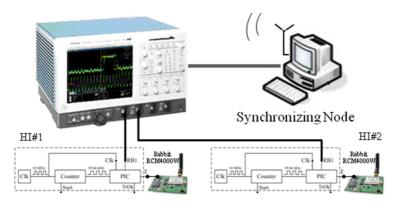

| 8.8 | Experimental set up to evaluate the delay between the trigger    |

| 0.0 | signals generated by the two HIs                                 |

|     | Signais generated by the two mis                                 |

#### XXII List of Figures

## List of Tables

| 2.1 | Comparison among synchronization procedures                                       | 16  |

|-----|-----------------------------------------------------------------------------------|-----|

| 3.1 | Experimental results obtained by changing OS and connection protocol              | 33  |

| 4.1 | THE TIME DELAY IN THE TEST OF FIG.4.2 BY DIFFERENT                                | 45  |

| 4.2 | SETTING OF THE OPERATION SYSTEM<br>EXPERIMENTAL RESULTS BY MODIFYING THE WIFI-USB | 45  |

| 4.2 | DRIVER                                                                            | 48  |

| 4.3 | Mean value and standard deviation of the time                                     | 10  |

|     | delay by different Linux OS and CPU occupancy                                     | 49  |

| 4.4 | Mean value and standard deviation of the time                                     |     |

|     | delay by different Linux OS, CPU occupancy and                                    |     |

|     | COMMUNICATION STANDARD                                                            | 57  |

| 4.5 | Mean value and standard deviation of the time                                     | 2.0 |

| 1.0 | DELAY BY CONSIDERING TDS220 DSO                                                   | 59  |

| 4.6 | MEAN VALUE AND STANDARD DEVIATION OF THE TIME                                     | 50  |

| 4.7 | DELAY BY CONSIDERING TDS7000 DSO<br>MEAN VALUE AND STANDARD DEVIATION OF THE TIME | 59  |

| 4.7 | DELAY BY CONSIDERING AWG INSTRUMENTS                                              | 60  |

|     | DELAI DI CONSIDERING AVVO INSTRUMENTS                                             | 00  |

| 5.1 | Evaluation of the synchronization time delay by                                   |     |

|     | USING THE ORIGINAL CONTROL PROGRAM OF THE BOARD                                   |     |

|     | Rabbit RCM4400W and the modified one. $\ldots$                                    | 75  |

| 6.1 | LIST OF THE COMPONENTS USED TO BUILD THE HI                                       |     |

| 0.1 | ACCORDING TO THE BLOCK SCHEME OF FIG.6.4 AND FIG.6.5.                             | 85  |

|     | ACCOLDING TO THE BLOOK SCHEME OF FIG.0.4 AND FIG.0.9.                             | 00  |

## Introduction

#### 1.1 Motivations and goals

The synchronization of co-operating processes is a new challenging requirement that emerges in the context of industrial automation, monitoring systems, inspection and management of strategic power plants, computer networks, and sensor networks applications.

The practical requirements of the synchronization, for measurement applications, concern with the correlation in the time domain of the measurements given by independent Measurement Instruments (MIs) connected to the nodes of the Distributed Measurement System (DMS) by proper Hardware Interface (HI). As a consequence, the following steps are involved: (i) implementation of protocols that guaranteeing the accurate synchronized operation at the node of the DMS, (ii) detection of the time delay among independent measurements, and (iii) compensation for the time delay.

The synchronization can be achieved by means of one of the following approaches: (i) sharing the common control signal, or (ii) sharing the common sense of the time.

The accuracy of the synchronization obtained with the first approach is strongly affected by the behavior of the communication network. Such inconvenience can be partially overcome by avoiding the packet collisions into the network.

Otherwise the synchronization based on sharing the common sense of time, because it requires that each node is equipped by the own clock, translates the problem into the minimization of the temporal drift between each node clock and one take as reference. In this case the accuracy strongly depends on the adopted clock synchronization policy.

Among the various procedures to share the common sense of time, those based on the Global Navigation Satellite Systems (GNSS) enable one to achieve, in established conditions, synchronization accuracy in the order of nanoseconds. The accuracy would satisfy the requirements of the measurement applications. In practice, due to the weakness and unreliability of the

#### 2 1 Introduction

satellite signal, relevant accuracy degradations may arise in several practical measurement contexts.

Moreover, the technical requirement to guarantee the free line-of-sight between the receiving antennas and the satellites makes the GNSS-based synchronization methods not suitable for indoor measurement applications. In many applicable scenarios these solutions are not employable or convenient, and synchronization procedures based on communication networks are used.

The Network Time Protocol (NTP), now established as Internet standard protocol, is used to organize and maintain the clock synchronization of the nodes in respect to the time reference. The fundamental advantage of the NTP is the fact that it includes the procedure to compensate the effects of statistical delay variations encountered in wide area networks. The NTP is designed for a large scale distribution network and can be advantageously used for the synchronization with millisecond accuracy. Often this accuracy is not adequate for some measurement applications.

In order to address the needs of the DMS, the standard IEEE 1588 introduce the Precise Time Protocol (PTP), specifically designed for the clock synchronization with microsecond or sub-microsecond accuracy in local networks.

It is worth remarking that this synchronization strategy does not operate on the MI but only on the clock of the HI. As a consequence, this synchronization strategy is not able to guarantee the measure synchronization by itself. In fact, even if the HIs at each node work in synchronized modality, the hardware and the software architecture involved in the communication with the MI can randomly time delay the commands.

The critical task remains to constrain the MI to operate on deterministic synchronized modality with respect to the clock of the HI.

The aim of this research is the characterization and the reduction of the random time delay between the trigger event instant, i.e. the time instant in which the MI should perform the measure and the effective start of the measurement operations by the MI.

Obviously, such analysis strongly depends on the nature of the HI and of the link between the HI and the MI.

In the DMSs many typologies of HIs may be employed, ranging from general purpose PCs to specialized embedded hardware, each one of them characterized by different features concerning with the causes introducing the random time delay. For such a reason suitably strategies for the random time delay reduction must be studied case-by-case accordingly with the adopted HI.

In particular, the following HIs are taken into account:

- General Purpose PC;

- Industrial Hardware;

- Embedded Hardware.

Each one of these HI permits implementation of a different accuracy level of synchronization time delay.

The PC is the typical interface to the DMS node. The main advantages of PC, used as HI, rely in its ability: (i) to use high level programming to drive the MI, (ii) to store high amount of data (hundreds gigabytes of data), (iii) to process the measurement data by means of proper processing capacity or by sharing the computational burdens among PCs belonging to a computer grid.

Fundamental disadvantage introduced by the PC is the time delay of the commands characterized by Gaussian distribution with high value of the standard deviation. The main reason of this behavior is that the procedure driving the MI is executed in concurrency with other processes. These last can be classified as (i) necessary to the PC functionality, e.g. the kernel; (ii) not strictly necessary to the PC functionality, e.g. the graphical user interface; and (iii) unwanted process, for example viruses, spywares, or malwares.

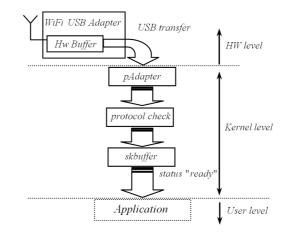

The execution time of each process is established by the kernel that, on the basis of the scheduling policy, satisfies the requests made by the active processes assigning the CPU for an established slot time.

Therefore, the time delay depends on: (i) the number of the concurrent processes, (ii) the scheduling policy, (iii) the kernel behavior.

In order to reduce the random time delay, the proper set-up of the software is the technique that should be examined. This technique consists of (i) the elimination of unnecessary and unwanted processes and (ii) the increase in priority of the ones involved in the drive of the MI (if allowed by the scheduler). Such an approach, even if revealed experimentally to be able to reduce "in practice" the time delays, does not give any theoretical guarantee on the achieved synchronization accuracy.

Another promising technique is based on the idea of translating the interaction between the PC and the MI at lower level than the user space. This technique imposes the low-level re-programming of the drivers of the MI in order to sensibly reduce both the mean and the standard deviation of the time delay avoiding the effects of the concurrence.

Moreover, the implementation of this technique with the real-time kernels can increase the determinism in the time execution of the processes.

Alternatively to the PC, the HI based on industrial hardware, as the Programmable Logic Device (PLD), is characterized by the absence of concurrency between processes, and could permit high level of synchronization accuracy.

Nevertheless, operating conditions of the PLD suggest further reduction of the standard deviation of the synchronization time delay that can occur. In particular, because the polling on condition is chosen as a technique to relieve the trigger event, two different conditions can occur:

• the trigger event occurs before the check operation in all the interfaces;

- 4 1 Introduction

- the trigger event occurs before the check operation in one device, after in other one;

In the last case the trigger will be detected after the time necessary to execute the polling cycle  $T_P$ . Therefore, by taken into account two PLDs, the synchronization time delay between their operation can varying between zero and  $T_P$ . In order to reduce the synchronization time delay, a promising technique is the reduction of the number of operations executed in the polling cycle. This goal can be achieved by changing the software architecture used by the PLD.

In order to overcome the inconvenience arising from the random time delay of the start time of the MI caused by the polling cycle, a different HI is taken into account to interface the MI to the node of the DMS. The architecture of this HI includes the PLD as wireless interface, and the Embedded Hardware designed and realized to reduce the random variation of the time delay and to avoid the polling cycle to check the trigger condition. In particular, the new HI is able to guarantee that:

- all the computational resources are devoted to detect the trigger event and to drive the MI;

- the trigger condition always occurs before the trigger check;

- the minimum number of operations is required to detect the trigger event and to drive the MI;

- the easy set-up of the parameters concerning the time execution measurement procedure:

- start time;

- number of repetitive measures to execute;

- time period among the measures.

On occasion, practical applications are required to perform synchronized measures among stand alone MIs not connected or not conveniently connectable by wired or wireless link to DMS. In these cases it is not possible to perform the synchronization by using the techniques presented in literature. In order to overcome these limitations it is possible that a Personal Digital Assistant (PDA) can be used to synchronize the operations executed by the stand-alone nodes.

The main idea consists of:

- select one DMS node as time references. The node is connected to the other ones and then synchronized with one of the techniques mentioned above;

- synchronize the PDAs to the reference node;

- use the PDA to bring "physically" the reference time to MI or another DMS inaccessible by the wired or wireless network.

The coarse resolution of the PDA clock is the first problem to be overcome in order to avoid the reduction of the synchronization accuracy. A valid solution is the use of the system cycle instead of the internal clock to "count" the time. Indeed, presently the PDA is equipped by CPU characterized by working frequency of hundred MHz. Therefore the achievable time resolution is in the order of ten ns.

Such accuracy would satisfy the requirements of most of the measurement applications but, in practice, the CPU working frequency can vary in respect to its nominal value. By definition, the PDA requires different time intervals to count the same number of system cycles.

To overcome this limitation it is proposed to estimate the real working frequency of the CPU and then change the number of system cycles to count in such a way that the same time interval is always employed.

In order to achieve high synchronization accuracy it is proposed that the conjunct use of the PDA and the Embedded Hardware are taken into account. The PDA permits the advantages of the high level programming languages in order to interface the MI and permits collection of the data. The Embedded Hardware permits the synchronization accuracy deriving by the deterministic behavior of the hardware.

Many are the applications requiring synchronized measurement procedures, and many are the operational conditions in which they are performed.

The goal of the research is to furnish theoretical and practical indications to choose a suitable solution in order to satisfy the synchronization accuracy requirements in an effective and efficient way.

#### 1.2 Thesis outline

The thesis is organized as follows.

After the first chapter containing the introduction to the research, the second chapter presents a brief overview of the main synchronization techniques. The analysis of their functioning highlights the problem of the degradation of the synchronization between MIs, due to the random time delay introduced by the HI connecting the MI to the node of the DMS.

In the third chapter the experimental characterization of this random time delay is performed by taking into account the PC as HI. The techniques to reduce this random time delay are proposed and experimentally investigated in chapter four.

In the fifth chapter the industrial hardware interface based on PLD is proposed to connect the MI to the node of the DMS. The complete absence of other processes sharing the computational resources, has highlighted other cause that make random the time delay of the software execution: the polling cycle to check the trigger event. Therefore two software procedures are proposed to reduce the standard deviation of the random time delay.

On the basis of the previous considerations, the sixth chapter presents the embedded hardware that avoids or reduces all the causes of delay.

#### 6 1 Introduction

The aim of the seventh chapter is the synchronization of stand-alone MIs, i.e. MIs not reached and not convenient to reach by wired or wireless link. In this case, it is not possible as per the application of the synchronization techniques presented in literature. Therefore, the PDA is used to physically bring the common sense of the time to the stand alone MI.

In order to achieve the same accuracy granted in the case of node of the DMS, in the eighth chapter the conjunct use of the PDA and the Embedded Hardware is proposed.

## Synchronization Techniques for DMS

Abstract - The brief review of the main synchronization techniques for measurement applications is reported. On the basis of the comparison among them and their practical uses in the Distributed Measurement Instruments (DMS) is highlighted the differences between the synchronization accuracy achieved by the Hardware Interfaces (HIs) connecting the Measurement Instrument (MI) to the node of the DMS, and the ones achievable by the MI. In particular it is highlighted that the HI introduces variable time delay in the communication with the MI.

#### 2.1 Introduction

In the literature the synchronization is a topical question considering that it is an important service in the distributing computer network [80], [11], [84] and in sensor network applications [102], [19], [95], [146]. It operates on the clock of the network nodes.

Today, precise timing is an inherent part of Global Navigation Satellite Systems (GNSS) [61] like the Global Positioning System (GPS) [88], GLONASS and Galileo [143]. These systems provide timing accuracy that, in established conditions, satisfy the requirements of measurement procedures in particular in the industrial contest. However, many are the causes of accuracy degradation that occurs in practical measurement contests.

In the Distributed Measurement System (DMS) the synchronization by network is preferred [28], due to the high stability of the working conditions and the use of preexistent communication structures.

Among the various procedures, the Network Time Protocol (NTP), now established as an internet standard protocol [29], is used to organize and maintain the clock synchronization of the PC to the time computer reference. Fundamental advantage of the NTP for application on DMS is the fact that its protocol includes procedure to compensate for the effects of statistical delay variations encountered in wide area networks and it is suitable for accurate

#### 8 2 Synchronization Techniques

and high resolution synchronization throughout the Internet. The numerous experimental tests performed show that, as a consequence of the clock drift of the PC, the synchronization interval is an influencing factor of both the accuracy and the stability of the synchronization [30]. Moreover, the NTP is designed for large scale distributed network and can be advantageous used for synchronization with millisecond accuracy.

In order to addresses the needs of the DMS, in the standard IEEE 1588 [31] a protocol designed for the clock synchronization with microsecond or sub-microsecond accuracy is proposed. In particular, the standard IEEE 1588 provides the protocol Precise Time Protocol (PTP) for synchronization among heterogeneous networked clocks requiring little network bandwidth overhead, processing power, and administrative setup.

Often the Measurement Instrument (MI) is interfaced to the DMS node by the PC and the synchronization procedure operates on the clock, internal or external, of this last. Therefore the PC can work on synchronized modality, but the hardware and software architecture of the path involved in the communication PC-MI can delay the commands.

#### 2.2 Techniques to synchronize clocks

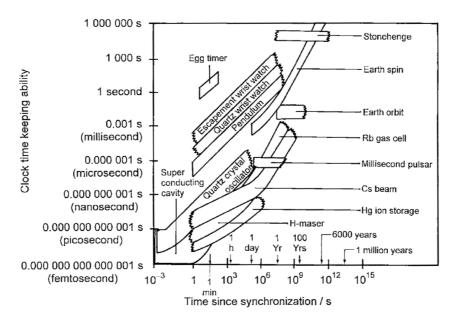

Over the years, the timekeeping community has used many different techniques and systems to help them with the task of synchronizing clocks or time transfer. Fig.2.1 shows the performance level of some of these systems. They include the use of:

- terrestrial communications systems, such as television and telephones (MODEMS);

- direct radio broadcasts (WWV [81] and WWVH [82]);

- navigation systems, such as Loran-C and Global Navigation Satellite Systems (GNSS);

- satellite communications systems such as Two-Way Satellite Time Transfer (TWSTT).

As clocks have become more precise and accurate, the timekeeping community has sought more precise and more stable systems to help them with synchronization. For the timekeeping community, GNSS is a significant contributor to solving the traditional problems of timekeeping. It is a reliable source of time and it is a reliable time-transfer system.

#### 2.3 Synchronization by using GNSS

The carrier signals broadcasted by Global Navigation Satellite Systems (GNSS) [61] disseminate precise time, time intervals, and frequency on wide

9

Fig. 2.1: Clock time-keeping ability.

geographic areas. The employment of satellite based timing signals could be particularly suitable since it could make possible the realization of accurate synchronization without requiring the deployment of primary time and time dissemination systems, assuring, at the same time, a set of intrinsic advantages such as wide area coverage, easy access to remote sites and adaptable to changing network patterns. The only user cost is for the receiver equipment, although fees may be levied in future satellite systems.

#### 2.3.1 GPS

The Global Positioning System (GPS) [103], [104], [73], [88] is a U.S. spacebased global navigation satellite system. It provides continuous reliable positioning, navigation, and timing services to worldwide users [94].

GPS is made up of three parts: between 24 and 32 satellites orbiting the Earth, four control and monitoring stations on Earth, and the GPS receivers owned by users.

GPS satellites broadcast signals from space that are used by GPS receivers to provide three-dimensional location (latitude, longitude, and altitude) plus the time [44].

The satellites are arrayed to provide a minimum worldwide visibility of four satellites at all times. GPS is steered by a ground-based cesium clock ensemble that itself is referenced to Coordinated Universal Time (UTC) [107], [78]. Each

#### 10 2 Synchronization Techniques

satellite provides a correction to UTC time that the receiver automatically applies to the outputs.

With this continuous adjustment, timing accuracy is limited only by short-term signal reception whose basic accuracy is  $0.2\mu s$ .

This baseline accuracy can be improved by advanced decoding and processing techniques [140].

GPS presently [61] provides two services, one for civilian users referred to as the Standard Positioning Service (SPS) and one available only to authorized users (primarily the U.S. military, and the militaries of U.S. allies) referred to as the Precise Positioning Service (PPS). In 1994, at one time, the accuracy of the SPS was intentionally degraded using a technique referred to as Selective Availability (SA), which was observed to be implemented as a pseudorandom dithering of the satellite clock that could be removed only by PPS receivers with knowledge of the generation algorithm and cryptographic keys [104]. On May 1, 2000, the intentional degradation of SPS performance due to SA was ceased [22]. More recently, in September 2007, the United States announced that the capability to implement SA will be removed from future GPS satellite procurements [105].

Since today, GPS is a navigation system that has proven itself to be a reliable source of positioning for both the military and civilian communities. But it is also an important and valuable utility to the timekeeping community [74].

In the following it is discussed briefly how GPS is used to propagate the common sense of the time.

As part of the navigation solution, the computer contained within the GPS receiver can determine the difference between the clock which is contained within the user receiver and either GPS time or the reference time for GPS, which is UTC (USNO), [44], [107], i.e., UTC as determined at the U.S. Naval Observatory.

The clock contained within a user's GPS receiver is usually a quartz crystal clock. However, in some cases, an external clock such as a rubidium frequency standard or a cesium beam frequency standard can be the local reference for a GPS receiver.

The local receiver can be programmed to display UTC(USNO), as broadcast by GPS, or GPS time since the navigation solution yields the difference between the local receiver clock and GPS time. It should be pointed out that UTC(USNO) is steered to UTC determined by the Bureau International des Poids et Mesures (BIPM) [78]. UTC(USNO) is usually kept to within about 10 ns of UTC.

One advantage the timing community has over the navigation community is the number of GPS satellites that it needs. The navigators need four satellites to determine their position: three to get their position and one to determine the offset of their local clock from GPS time.

Since the timekeepers are in fixed locations and know their position, they only need one GPS satellite to get the offset of their local clock from GPS time. Consequently, they have modified the algorithms in their timekeeping receivers to take advantage of this fact.

#### **GPS CV** techniques

The GPS Common View(CV) is the techniques with whom GPS Synchronize Clocks over Large Distances.

In the CV technique, two stations simultaneously observe the same GPS satellite. Each of the users at both stations must record the difference between his local clock or local time reference,  $T_a$  and  $T_b$  respectively, and GPS time at the same instant using the same satellite and using a GPS receiver known as a GPS Time-Transfer Unit (TTU). A GPS TTU is a special GPS receiver programmed to compute and display items of interest to the timing community [78].

Therefore, taken into account the two user A and B, it is :

$$User A observes : A = T_a - GPS time \tag{2.1}$$

$$User B observes : B = T_b - GPS time \tag{2.2}$$

It is essential that the two users observe the same satellite at the same instant in order to minimize the effects of some errors [6]. By computing the difference between the two sets of numbers:

$$A - B = T_a - GPStime - (T_b - GPStime) = T_a - T_b$$

(2.3)

one easily calculates the differences between the two local clocks because the common GPS clock drops out. This is a very simple but powerful process because it is independent of GPS time.

Over the years, significant progress has been made in improving the precision and accuracy of the time distribution and clock synchronization capabilities of GPS. Presently, we are at the 10-25 ns level in one-way time distribution with a coarse acquisition code receiver and at the 2-15 ns level in time synchronization.

A range of values is given for these estimates to indicate that experience has shown that what is achievable is dependent on the user and site specific. These values are representative of the results currently obtained by users in different fields such as telecommunications and metrology.

#### 12 2 Synchronization Techniques

#### Practical application of GPS in DMS

The application of GPS in the DMS was initially strongly limited by the Selected Availability (SA) mechanism [78], removed only in the 2000 [22], and by the high cost of the receivers. Today it is applied to disseminate the sense of the time between DMSs distributed on geographical areas and that can have at least one node equipped by a GPS receiver and that can "see" the sky. A practical application is for example the DMSs applied to monitoring volcanoes, earthquake, changing on the morphology of the territories, [128], etc. In these systems the coordination of the time between the nodes is fundamental to establish, for example, the position of the earthquake epicenter, and the accuracy of the position is depending on the accuracy of the synchronization between the node.

#### 2.3.2 GLONASS

The Russian GLObal NAvigation Satellite System (GLONASS) was inaugurated in 1982. The full constellation of twenty four satellites plus one spare satellite was completed on 18 January 1996 providing similar capabilities to GPS [77].

Because the GLONASS signal is free of intentional degradation [31] and available world-wide, it offers to the international time metrology community an additional tool for high accuracy time transfer.

However, the GLONASS satellites had a short design life (1 to 3 years [73]) and due to the Russian economical crisis, the constellation has decayed. Fortunately, the GLONASS program has been reinvigorated after that the Russian Federation passed the Decrete Number 587 (August 2001), and in the 2008 consists of only 13 operational satellites [61].

Therefore, because the GLONASS system has not reached its final configuration, today it is used in conjunction with the GPS to improve the timekeeping accuracy [77]. Indeed a single user could see a higher number of satellites, and the modern algorithms implemented in the dual receivers, GPS-GLONASS, improve the accuracy of the position and of the time [18].

#### 2.3.3 GALILEO

The European Space Agency (ESA) GALILEO system is the third global satellite time and navigation system to come on line.

It comprises a constellation of 30 satellites divided among three circular orbits at the altitude of 23222 km to cover the Earth's entire surface.

The Galileo system was born as the European answer to GPS and GLONASS, mainly because a return back to the SA techniques damages all the application and research fields strongly depending on the Satellite Time and Frequency Transfer, first of all the European timekeeper community. In [60] it is summarize the Galileo timekeeping infrastructure. The purpose of such infrastructure is to:

13

- generate a stable time scale (Galileo System Time, GST) to fulfil the needs of the core services (i.e. Open Service, Safety-of-Life Service etc.)

- provide UTC parameters for broadcast

- determine the GPS to Galileo Time Offset (GGTO) in order to facilitate the user's interoperability.

A description of the different time related actors and their corresponding roles within and outside the Galileo core infrastructure was given in [64]. The main elements are the Precise Timing Facility (PTF) [144], [143] being part of the Galileo Ground Mission Segment (GMS), the external Time Service Provider (TSP) [1] and the external GPS system for the provision of GPS to Galileo Time Offset. The core function of the PTF is to generate GST, including a physical realization, GST Master Clock (GST(MC)), for metrological purposes and for providing timing reference signals to all elements within the Galileo system. The main task of the TSP is to provide the GST to UTC mod 1 s steering corrections, and the offset between GST and UTC as required for the provision of the UTC time dissemination service.

Galileo will have an integrity signal to ensure the quality of the signals received and to inform the user immediately of any error. The GALILEO time precision in terms of time errors (95% confidence) for different signals ranges from 0.7-8.1 ns [86].

The higher accuracy granted, the absence of SA mechanism and the automatic detection of satellite errors, make Galileo a new promises for the DMS.

#### 2.3.4 Limits of the synchronization techniques based on GNSS

However many are the causes of not applicability of the synchronization based on satellites for practical DMS applications.

As above mentioned, the hardware receivers need to be reached by the satellite signal, therefore this techniques is not applicable for indoor applications.

Moreover, many are the causes of accuracy degradation in practical contests. The synchronization based on satellite requires the use of specific hardware to receive and elaborate the signal, and the achievable resolution strongly depends on the quality of this last [18].

Satellite based synchronization systems greatly relies on information transfer over the air interface. This wireless nature of satellite communications links and the weak power levels of GNSS signals make them vulnerable to radio frequency interference. Any electromagnetic radiation source can act as interference source, if it can emit potential radio signals in the satellite signals frequency bands.

The disruption mechanisms that could limit the GNSS performance can be classified as:

- 14 2 Synchronization Techniques

- Ionospheric effects: the sunspot activity causes an increase in the solar flux, charged particles and electromagnetic rays emitted from the Sun [101], [65].

- Unintentional Interference: when there will be restricted lines of sight to satellites (i.e. in urban areas, near or under foliage) the synchronization signal quality could deteriorate for short or long term.

- Radio Frequency Interference: It is caused by electronic equipment radiating in the GNSS frequency band (i.e. television/radio broadcast transmitters, mobile phones) [41].

- Intentional Interference: GNSS signals are extremely weak. Therefore they can be deliberately jammed by radio interference. The levels of interference needed to jam a typical consumer GPS receiver are quite low and jamming equipment can be small [41]. Further intentional interferences could be induced by:

- Spoofing Counterfeit Signals

- Meaconing Delay & Rebroadcast

- System Damage.

These problems strongly influencing the synchronization accuracy, and therefore can alter the overall measurement processes.

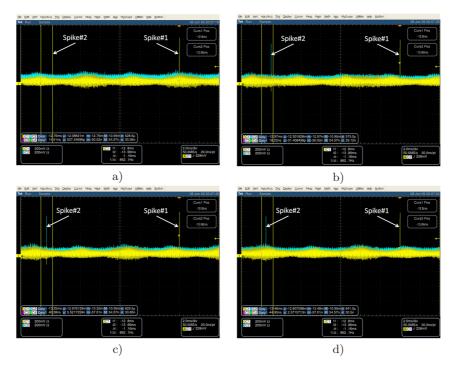

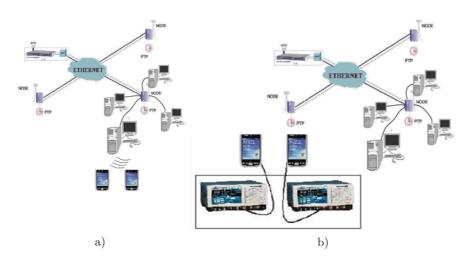

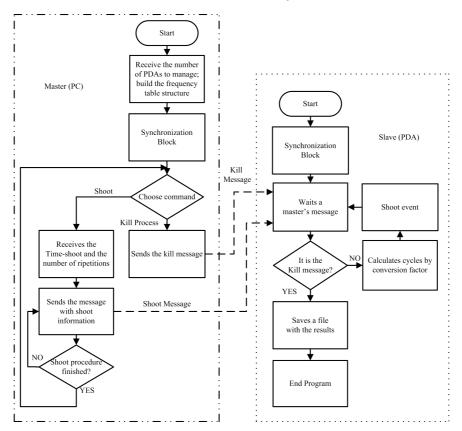

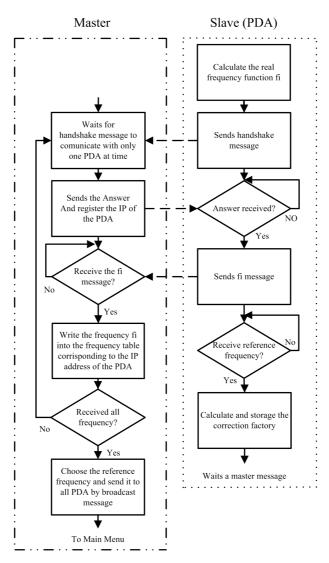

#### 2.4 Synchronization based on internet