# **BUILDING BLOCKS FOR SIGE BICMOS MULTICORE**

# CHIP FOR KA-BAND SATCOM ON THE MOVE

## **USER TERMINALS**

by

Alireza Shamsafar

A Thesis Presented in Partial Fulfillment of the Requirements of the Degree PhD Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica

UNIVERSITA DELLA CALABRIA

November 2013

#### UNIVERSITA' DELLA CALABRIA

Dipartimento di Ingegneria Informatica, Modellistica, Elettronica e Sistemica

#### Dottorato di Ricerca in

Ingegneria dei Sistemi e Informatica

#### CICLO

XXVI

## BUILDING BLOCKS FOR SIGE BICMOS MULTICORE CHIP FOR KA-BAND SATCOM ON THE MOVE USER TERMINALS

Settore Scientifico Disciplinare 09-ING-INF/02

**Coordinatore:**

Prof. S. Greco Firma\_ 5

Supervisore/Tutor: Prof. G.Amendola Firma Ing. L.Boccia Firm

Dottorando: Dott Alireza Shamsafar Firma

## UNIVERSITA DELLA CALABRIA

## THE GRADUATE SCHOOL Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica

**2013** Date

We hereby recommend that the thesis prepared under our supervision by

Alireza Shamsafar

## entitled **BUILDING BLOCKS FOR SIGE BICMOS MULTICORE**

### CHIP FOR KA-BAND SATCOM ON THE MOVE USER TERMINALS

be accepted in partial fulfillment of the requirements for the Degree of

#### Dottorato di Ricerca in Ingegneria dei Sistemi e Informatica

Prof. G. Amendola Prof. L. Boccia

Supervisor of Thesis Research Prof. S. Greco Head of Department DIMES Department

Recommendation concurred in:

Advisory Committee

**Approved:**

Approved:

Director of Graduate Studies

Dean of the Graduate School

Dean of the College

### ABSTRACT

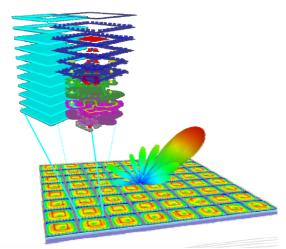

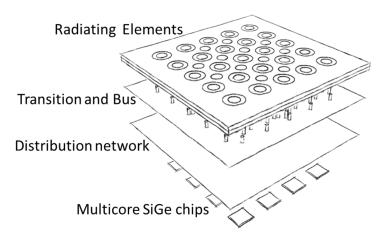

This project presents building blocks for an innovative configuration of reconfigurable Ka-band Tx/Rx SatCom user terminal antenna operating in the 29.5–30.8GHz and 19.7–21.0GHz bands. The proposed approach is based on a low-profile active phased-array implemented integrating a multilayer printed circuit with reconfigurable SiGe BiCMOS MMICs. The radiating part of the array is implemented employing dual band elements arranged in an interleaved configuration. Each radiating element is equipped with one complete Tx/Rx unit. Chips developed for this project are referred to as "intelligent pixels" as they integrate all the RF analogue, mixed-signal and digital control circuitry. Each multiple Tx and Rx cores which can independently operate amplitude and phase control, as it is required to implement 2-D beam steering arrays. Furthermore, power amplifiers, Power divider, vector modulator, switching network and low noise amplifiers are embedded into each transmit and receive core respectively to fulfill link budget requirements for Sat-Com applications. In the proposed configuration, each SiGe BiCMOS MMIC chip controls 2 Rx and 4 Tx antenna elements.

## APPROVAL FOR SCHOLARLY DISSEMINATION

The author grants to the Library of Universita Della Calabria the right to reproduce, by appropriate methods, upon request, any or all portions of this Thesis. It is understood that "proper request" consists of the agreement, on the part of the requesting party, that said reproduction is for his personal use and that subsequent reproduction will not occur without written approval of the author of this Thesis. Further, any portions of the Thesis used in books, papers, and other works must be appropriately referenced to this Thesis.

Finally, the author of this Thesis reserves the right to publish freely, in the literature, at any time, any or all portions of this Thesis.

Author Alireza Shamsafar

Date Nov 2013

# **DEDICATION**

This thesis is dedicated to my lovely wife Elnaz Abaei, my father Rasoul Shamsafar and my mother Nahid Baradaran Hossieni who they help me a lot during these years.

| TABLE OF CONTENTSABSTRACTiii                                 |

|--------------------------------------------------------------|

| APPROVAL FOR SCHOLARLY DISSEMINATION iv                      |

| DEDICATION                                                   |

| LIST OF FIGURES ix                                           |

| LIST OF TABLESxv                                             |

| ACKNOWLEDGMENTS                                              |

| CHAPTER 1 INTRODUCTION1                                      |

| 1.1 Introduction of Ka-band systems1                         |

| 1.2 Thesis organization4                                     |

| CHAPTER 2 Ka-band Satcom systems                             |

| 2.1 A Ka-band systems6                                       |

| 2.2 SatCom user terminal antennas                            |

| 2.2.1 Fully mechanical pointing11                            |

| 2.2.2 Electronic elevation and mechanical azimuth pointing   |

| 2.2.3 Other emerging trends                                  |

| 2.3 Objective of the thesis                                  |

| CHAPTER 3 IHP 0.13um SiGe BiCMOS process technology          |

| 3.1 MMIC Introduction                                        |

| 3.2 SG25H3 process                                           |

| 3.2.1 Active components                                      |

| 3.2.2 Passive components                                     |

| 3.2.2.1 Inductors                                            |

| 3.2.3 MiM Capacitors                                         |

| 3.2.4 Resistors                                              |

| CHAPTER 4 Satcom user terminal with electronic beam scanning |

| 4.1 Antenna array configuration                             | 37             |

|-------------------------------------------------------------|----------------|

| 4.2 Chip configuration and architecture                     | 45             |

| 4.3 Link budget and chip components specs                   | 47             |

| CHAPTER 5 Low noise amplifier                               | 51             |

| 5.1 Low-noise amplifier design strategy                     | 51             |

| 5.1.1 LNA requirements and preliminary performance analysis | 51             |

| 5.1.2 Schematic description                                 | 54             |

| 5.1.2.1 Stability analysis                                  | 56             |

| 5.1.3 LNA biasing                                           | 57             |

| 5.1.4 Layout generation                                     | 59             |

| 5.2 Measurement and results                                 | 51             |

| CHAPTER 6 Switching network on chip                         | 56             |

| 6.1 CMOS switch design                                      | 56             |

| 6.1.1 Single switch design                                  | 57             |

| 6.2 CMOS switching network design                           | 59             |

| 6.3 Measurements and results                                | 73             |

| 6.3.1 RX mode results                                       | 74             |

| 6.3.2 TX mode results                                       | 78             |

| CHAPTER 7 Vector modulator on chip                          | 32             |

| 7.1 Vector modulator concept                                | 32             |

| 7.2 Design of the 90° transformer hybrid                    | 32             |

| 7.3 Vector modulator design                                 | 36             |

| 7.4 Measured and simulated results                          | <del>9</del> 1 |

| CHAPTER 8 Broadband power divider-combiner on chip          | <del>9</del> 3 |

| 8.1 Wilkinson power divider-combiner on chip                | 93             |

| 8.2   | Broadband power divider-combiner design                   | 94  |

|-------|-----------------------------------------------------------|-----|

| 8.3   | Measurement and results                                   | 97  |

| CHAPT | ER 9 Diplexer network on chip                             | 101 |

| 9.1   | Diplexer design                                           | 101 |

| 9.2   | Layout generation                                         | 104 |

| 9.3   | Measurement and results                                   | 108 |

| CHAPT | ER 10 Test board design for experimental characterization | 112 |

| 10.1  | Test board design                                         | 112 |

| 10.2  | Measurement and results                                   | 117 |

| CHAPT | ER 11 CONCLUSIONS AND FUTURE WORK                         | 125 |

| 11.1  | Conclusions                                               | 125 |

| 11.2  | Future Work                                               | 126 |

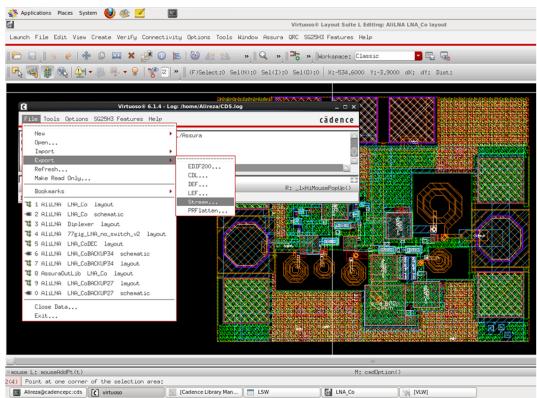

| APPEN | DIX A LAYOUT GENERATION                                   | 128 |

| A.1   | Cadence schematic                                         | 132 |

| A.2   | Layout generation                                         | 134 |

# LIST OF FIGURES

| Figure 1-1: Frequency spectrum                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1: HGA Coordinate System. ( www.matis.net)10                                                                                     |

| Figure 2-2: Mechanical Antenna pointing (www.kymetacorp.com)12                                                                            |

| Figure 2-3: Viasat aperture array antenna.(www.viasat.com)14                                                                              |

| Figure 2-4: System diagram of Viasat antenna.(www.viasat.com)15                                                                           |

| Figure 2-5: LTCC frontend antenna circuitries (IMST GmbH, Germany)16                                                                      |

| Figure 3-1: MMIC wafers. (www.microwave-eetimes.com)                                                                                      |

| <b>Figure 3-2:</b> Stack up of SG25H3 technology with 5 metal layers (www.ihp-microelectronics.com)                                       |

| <b>Figure 3-3:</b> Layout of ihp_npnH3shp16 bipolar transistor with 16 emitters as it is provided in the IHP SG25H3 design kit            |

| <b>Figure 3-4:</b> Planar spiral inductor layouts (a) Square (b) Octagonal (c) Hexagonal (d) Circular (www.vlsi.itu.edu.tr)               |

| Figure 3-5: Spiral inductor model                                                                                                         |

| <b>Figure 3-6:</b> L=0.4 nH spiral inductor HFSS model                                                                                    |

| <b>Figure 3-7:</b> Micro photo of 0.4nH rectangular spiral inductor shown in figure 3-627                                                 |

| <b>Figure 3-8:</b> Simulation and measurement results of the inductance of the 0.4nH spiral inductor shown in figure 3-7                  |

| Figure 3-9: Quality factor of simulation and measured 0.4nH spiral inductor29                                                             |

| <b>Figure 3-10:</b> Simulation and measurement results of the inductance of the spiral inductor shown in figure 3-7 without metal 1 below |

| <b>Figure 3-11:</b> Quality factor of simulation and measured spiral inductor without metal 1 below                                       |

| Figure 3-12: MiM capacitor realization in SG25H3 technology.                       | 31 |

|------------------------------------------------------------------------------------|----|

| Figure 3-13: Equivalent circuit model of capacitor                                 | 32 |

| Figure 3-14: HFSS model of 1pF MiM capacitor                                       | 32 |

| Figure 3-15: Micro photo of fabricated prototype of 1pF MiM capacitor              | 33 |

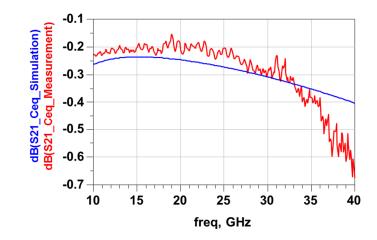

| Figure 3-16: S <sub>21</sub> of simulation and measurement of 1pF MiM capacitor    | 34 |

| Figure 3-17: S <sub>11</sub> of simulation and measurement of 1pF MiM capacitor    | 34 |

| <b>Figure 3-18:</b> Layout of (a) ihp_rsill (b) ihp_rpnd (c) ihp_rppd (d) ihp_rhgh | 36 |

| Figure 4-1: Antenna array layout.                                                  | 38 |

| Figure 4-2: 20GHz radiating element geometry.                                      | 39 |

| Figure 4-3: 30GHz radiating element geometry.                                      | 39 |

| Figure 4-4: Dual band radiator layout (FLEXWIN Deliverable D2.1).                  | 40 |

| Figure 4-5: Feeding of dual band radiating element (FLEXWIN Deliverable D2.1).     | 41 |

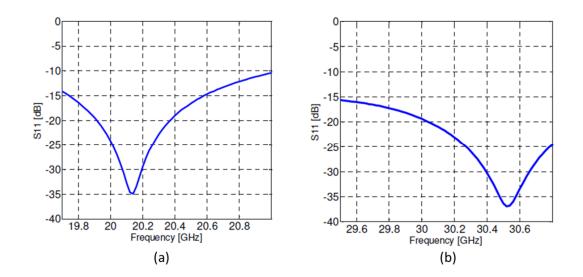

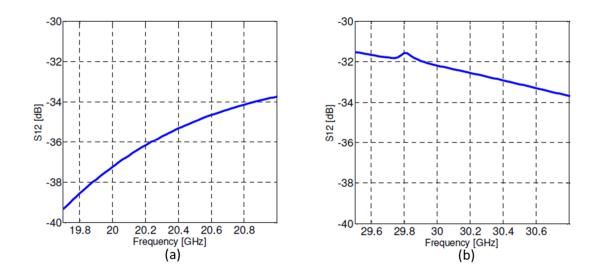

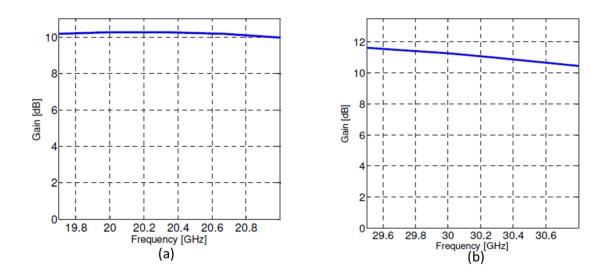

| Figure 4-6: Simulated S <sub>11</sub> at (a) RX port (b) TX port.                  | 41 |

| Figure 4-7: Simulated isolation in (a) RX band (b) TX band.                        | 42 |

| Figure 4-8: Simulated gain for 2×2 sub-array for (a) TX band (b) RX band           | 42 |

| Figure 4-9: Layout of antenna array.                                               | 43 |

| Figure 4-10: Antenna array feeding network with multicore SiGe chip                | 44 |

| Figure 4-11: Chip position and feeding lines to radiating elements                 | 44 |

| Figure 4-12: Block diagram of the chip and I2C control unit                        | 46 |

| Figure 4-13: Block diagram of multicore SiGe chip with RF blocks                   | 47 |

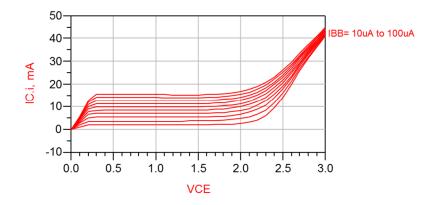

| Figure 5-1: DC behavior of the IHP_npnH3shp16 for different base currents          | 53 |

| Figure 5-2: (a) minimum noise figure (b) gain of IHP_npnH3shp16 for                | 53 |

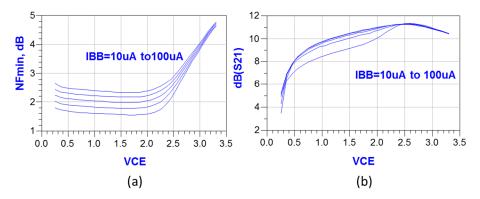

| Figure 5-3: Schematic of designed dual stage cascode LNA.                          | 54 |

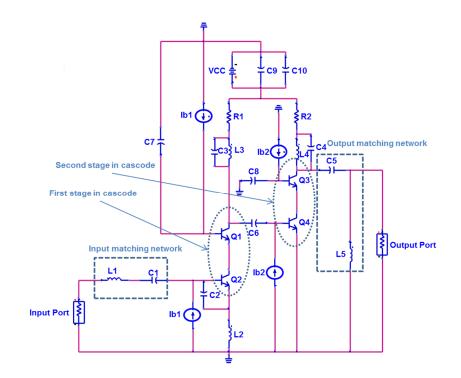

| Figure 5-4: Schematic of designed current mirror.                                  | 58 |

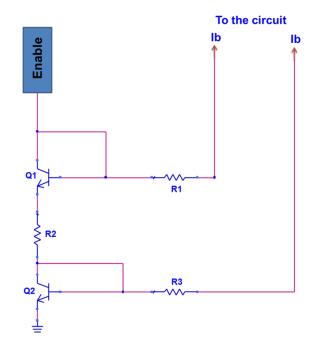

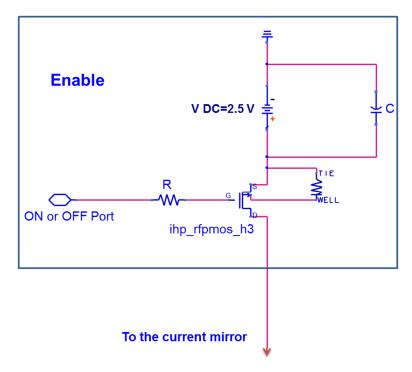

| Figure 5-5: Schematic of the enable circuit employed in the current mirror         | 59 |

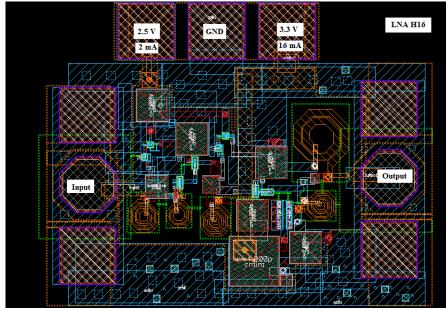

| Figure 5-6: Layout of 20 GHz LNA with RF and DC pads                                                                            | 60 |

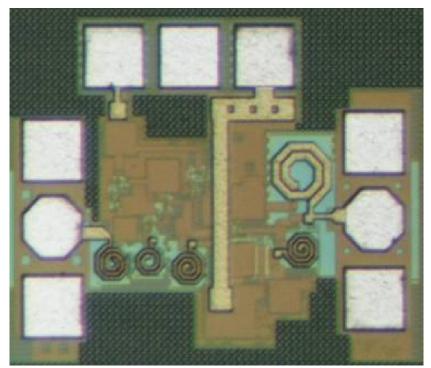

|---------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 5-7: Micro photo of fabricated 20GHz LNA prototype                                                                       | 60 |

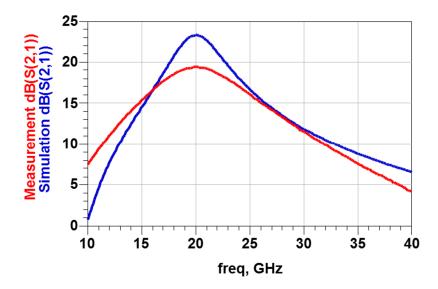

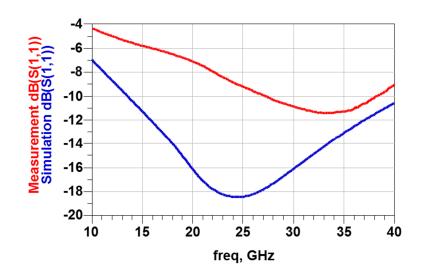

| Figure 5-8: Measured and simulated gain of designed LNA.                                                                        | 61 |

| Figure 5-9: Measured and simulated input matching (S <sub>11</sub> ) of designed LNA.                                           | 62 |

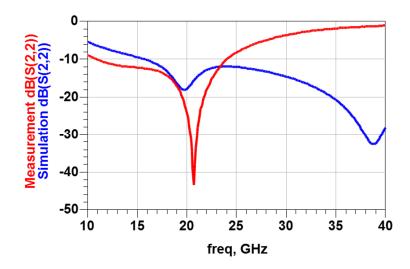

| Figure 5-10: Measured and simulated output matching (S <sub>22</sub> ) of designed LNA                                          | 62 |

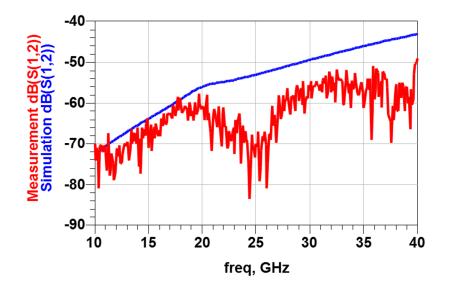

| <b>Figure 5-11:</b> Measured and simulated isolation (S <sub>12</sub> ) of designed LNA.                                        | 63 |

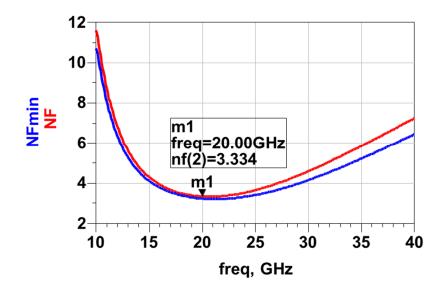

| Figure 5-12: Minimum nose figure and noise figure of designed LNA                                                               | 64 |

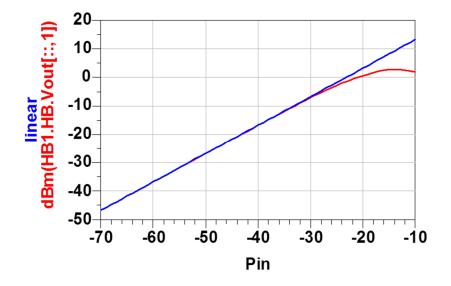

| Figure 5-13: 1dB compression point of the designed LNA                                                                          | 64 |

| Figure 5-14: Stability factor (K) of the designed LNA.                                                                          | 65 |

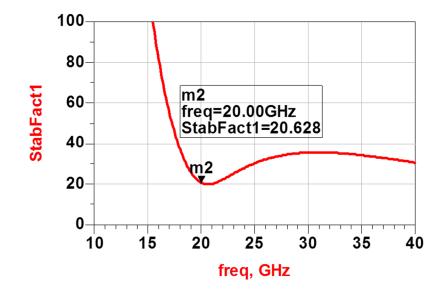

| Figure 6-1: NOMS electrical model for on and off stats                                                                          | 67 |

| Figure 6-2: Schematic of the single switch                                                                                      | 68 |

| Figure 6-3: Simulation results of the single switch in Rx mode (SW RX)                                                          | 68 |

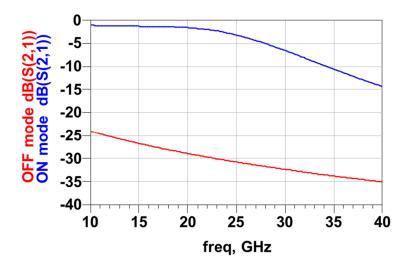

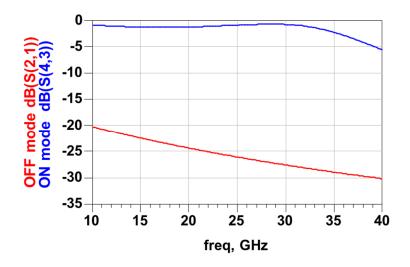

| Figure 6-4: Simulation results of the single switch in Tx mode (SW TX)                                                          | 69 |

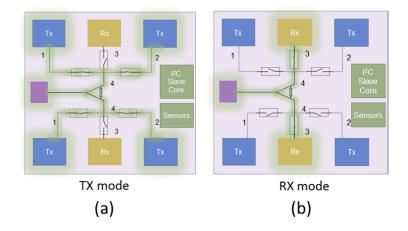

| Figure 6-5: Power flow in the chip on (a) TX (b) RX mode                                                                        | 70 |

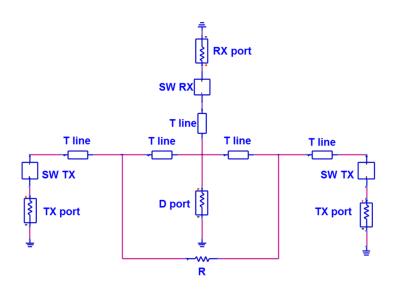

| Figure 6-6: Schematic of designed switching network.                                                                            | 71 |

| Figure 6-7: Layout of the 10 port device including all the inductors of the switching network.                                  | 72 |

| Figure 6-8: Layout of designed switching network                                                                                | 73 |

| Figure 6-9: Micro photo of fabricated switching network                                                                         | 73 |

| Figure 6-10: Measured and simulated results of insertion loss of the switching network in RX mode                               | 74 |

| <b>Figure 6-11:</b> Measured and simulated results of the switching network input (D port) matching in RX mode.                 | 75 |

| <b>Figure 6-12:</b> Measurement and simulation results of the switching network output matching (RX port) in RX mode.           | 76 |

| <b>Figure 6-13:</b> Measurement and simulation results of isolation between the switching network D port and RX port in TX mode | 76 |

| Figure 6-14: Measurement and simulation results of isolation between the switching network D port and TX port in RX mode. | .77 |

|---------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6-15: Measured and simulated results of the switching network insertion loss in TX mode.                           | .78 |

| Figure 6-16: Measured and simulated results of switching network input (D port) matching in TX mode.                      | .79 |

| Figure 6-17: Measurement and simulation results of switching network output matching (TX port) in TX mode.                | .80 |

| Figure 6-18: Measurement and simulation results of isolation between switching network D port and TX port in RX mode      | .80 |

| Figure 6-19: Measurement and simulation results of isolation between switching network RX port and TX port in TX mode     | .81 |

| Figure 7-1: HFSS model of designed 90 degree hybrid transformer                                                           | .83 |

| Figure 7-2: Circuit model of 90 degree hybrid transformer.                                                                | .84 |

| Figure 7-3: Simulated module of the S parameters of designed hybrid transformer                                           | .85 |

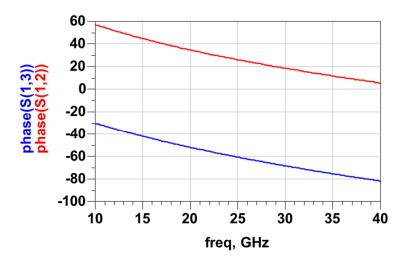

| Figure 7-4: Phase response of trough port and coupled port.                                                               | .85 |

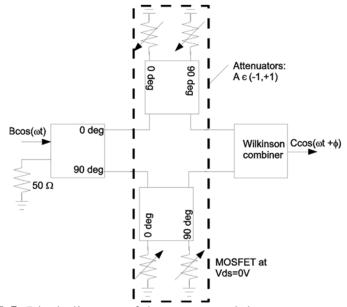

| Figure 7-5: Block diagram of the vector modulator                                                                         | .86 |

| Figure 7-6: Schematic of variable impedance that is shown in figure 7-5                                                   | .87 |

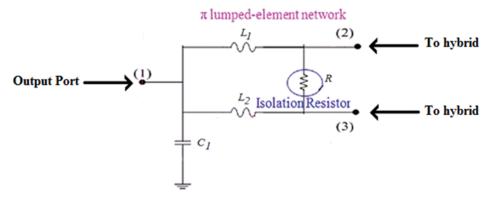

| Figure 7-7: Schematic of the power divider-combiner used in the 20 GHz vector modulator.                                  | .89 |

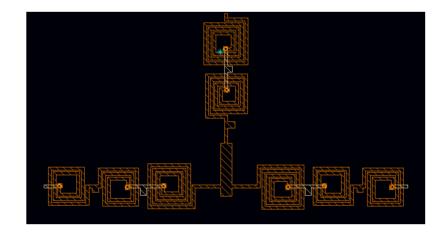

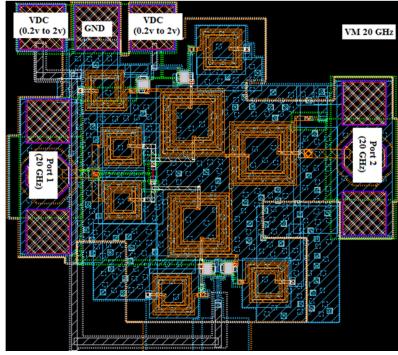

| Figure 7-8: Layout of the designed 20 GHz vector modulator                                                                | .90 |

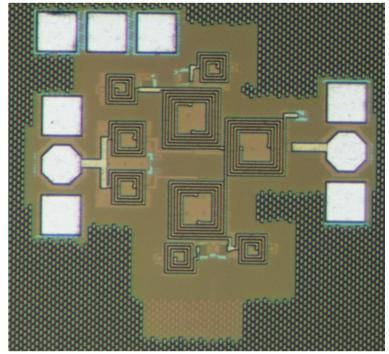

| Figure 7-9: Micro photo of the fabricated 20GHz vector modulator prototype                                                | .90 |

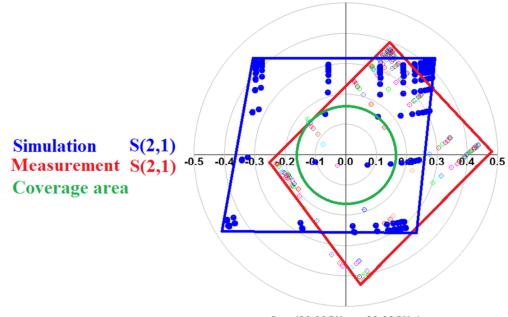

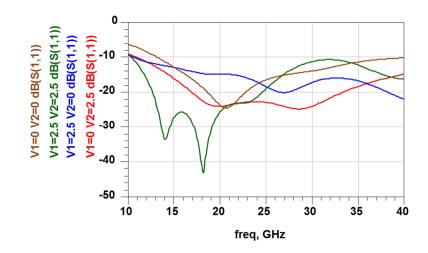

| Figure 7-10: Measured and simulated results of the 20 GHz vector modulator and the relative coverage area.                | .91 |

| Figure 7-11: Measured input matching of the vector modulator at four different bias conditions.                           | .92 |

| Figure 7-12: Measured output matching of the vector modulator at four different bias conditions.                          | .92 |

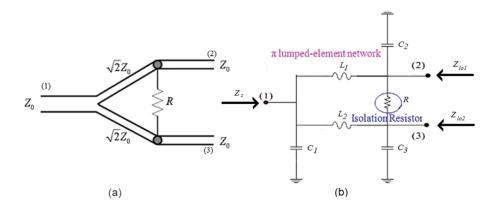

| Figure 8-1: A power divider based on: (a) distributed elements; (b) lumped components.                                    | .94 |

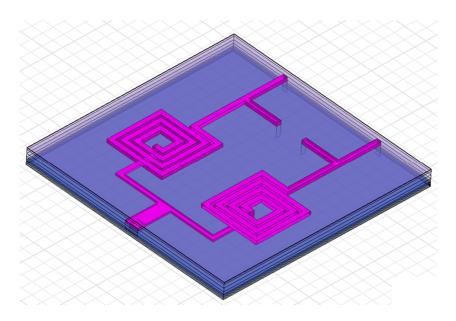

| Figure 8-2: Full wave model of the designed power divider-combiner.                                   | 96  |

|-------------------------------------------------------------------------------------------------------|-----|

| Figure 8-3: Layout of the designed power divider-combiner                                             | 96  |

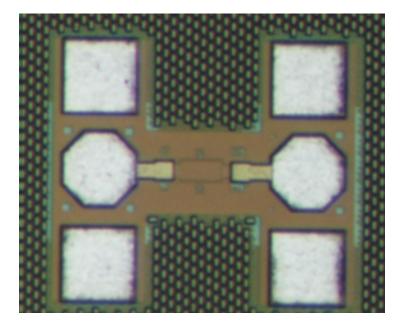

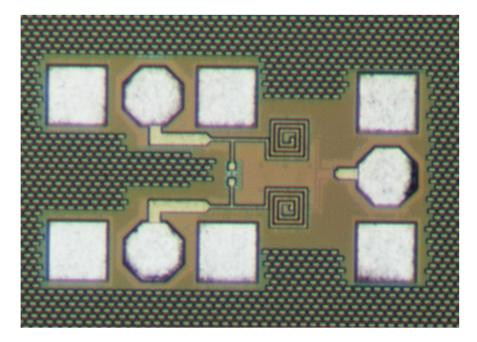

| Figure 8-4: Micro photo of the designed power divider-combiner                                        | 97  |

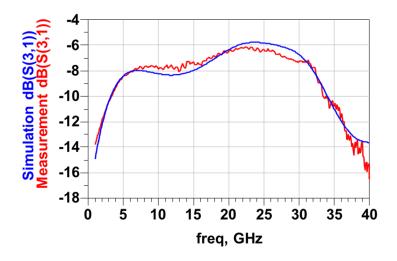

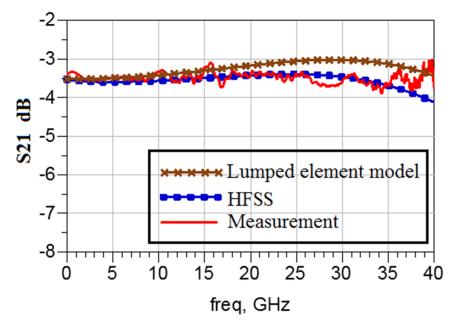

| Figure 8-5: Power division coefficient of designed power divider-combiner                             | 98  |

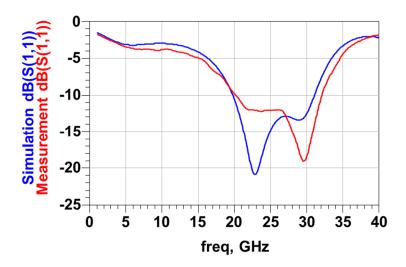

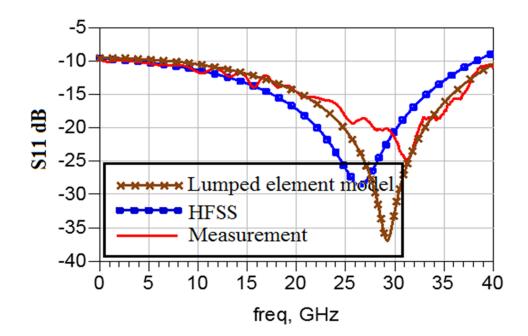

| Figure 8-6: Input matching of designed power divider-combiner                                         | 98  |

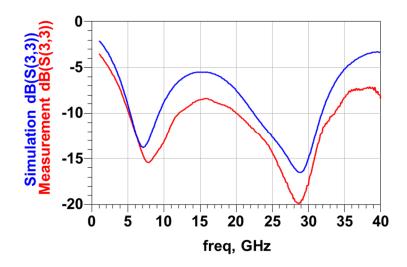

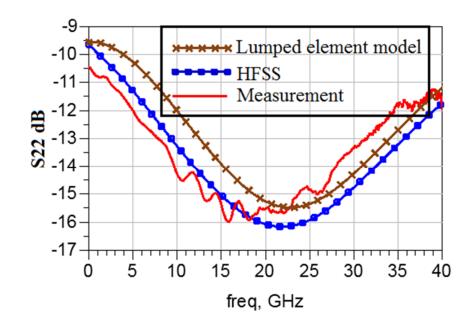

| Figure 8-7: Output matching of designed power divider-combiner                                        | 99  |

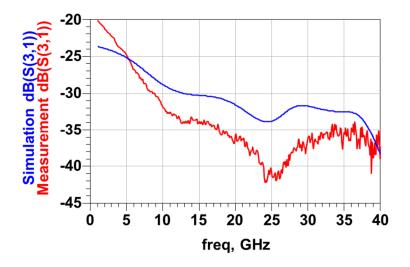

| Figure 8-8: Isolation of designed power divider-combiner.                                             | 99  |

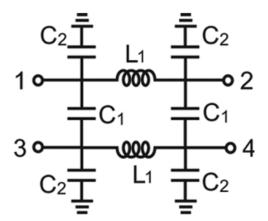

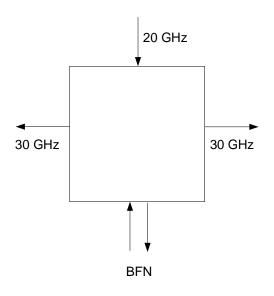

| Figure 9-1: Functional description of the diplexer network                                            | 101 |

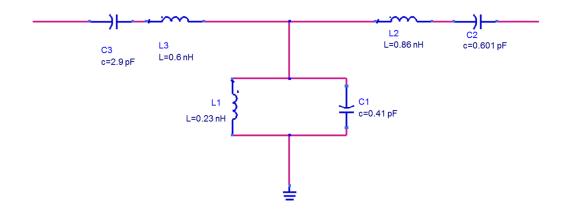

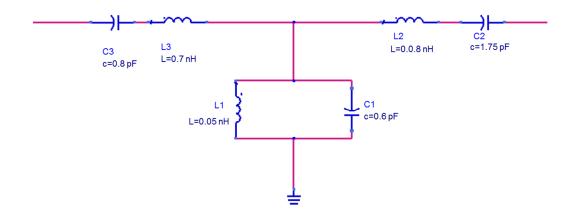

| Figure 9-2: Band-pass filter schematic for the two 20 GHz branch                                      | 102 |

| Figure 9-3: Band-pass filter schematic for the 30 GHz branches.                                       | 102 |

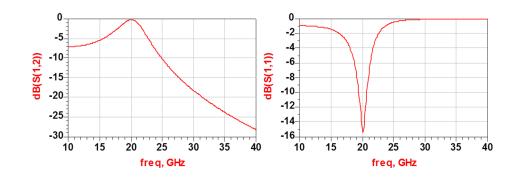

| Figure 9-4: Response of the 20 GHz lumped element band-pass filter                                    | 103 |

| Figure 9-5: Response of the 30 GHz lumped element band-pass filter                                    | 103 |

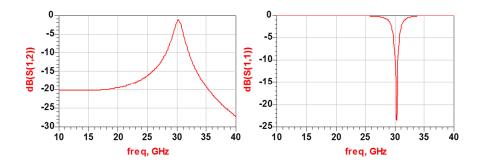

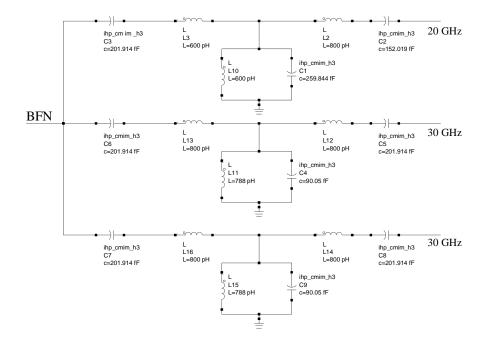

| Figure 9-6: Optimized schematic of the lumped element model of the diplexer                           | 104 |

| <b>Figure 9-7:</b> Simulated results of the diplexer schematic shown in Fig. 9-6 for the 20GHz branch | 105 |

| <b>Figure 9-8:</b> Simulated results of the diplexer schematic shown in Fig. 9-6 for the 30GHz branch | 106 |

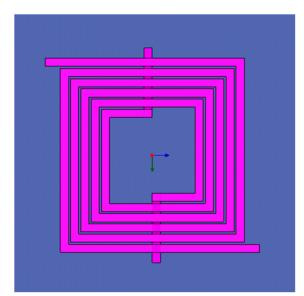

| Figure 9-9: Diplexer layout as it was simulated in HFSS: 3-D view                                     | 107 |

| Figure 9-10: Diplexer layout as it was simulated in HFSS: 2-D view                                    | 107 |

| Figure 9-11: Layout of the diplexer                                                                   | 108 |

| Figure 9-12: Micro-photo of the diplexer prototype                                                    | 109 |

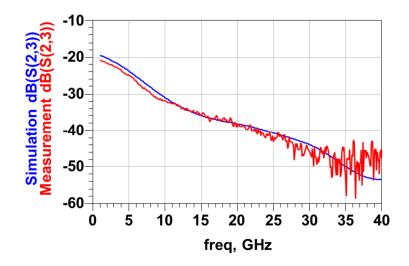

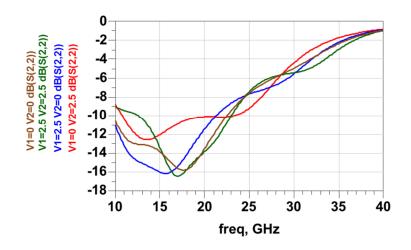

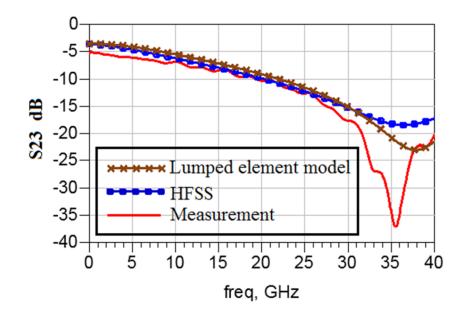

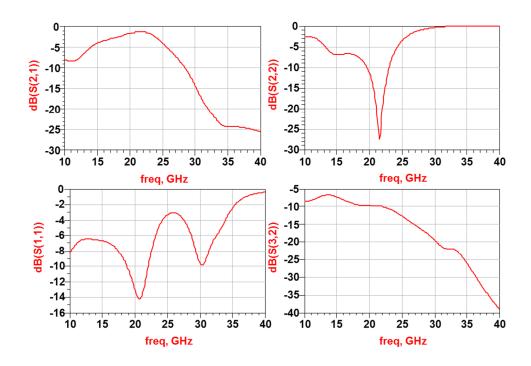

| Figure 9-13: Simulated and measured results of the diplexer network: 20 GHz branch.                   | 110 |

| Figure 9-14: Simulated and measured results of the diplexer network: 30 GHz branches.                 | 110 |

| Figure 9-15: Simulated and measured results of the diplexer network: isolation                        | 111 |

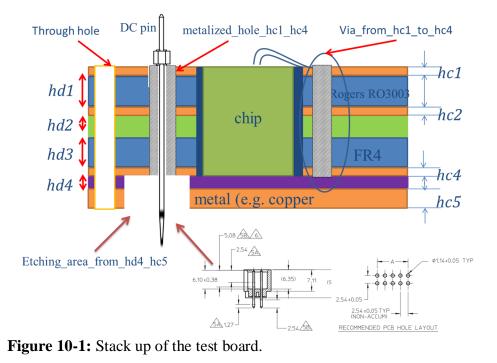

| Figure 10-1: Stack up of the test board                                                               | 113 |

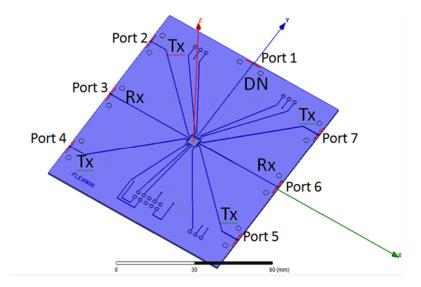

| Figure 10-2: The chip test board model                                                                                                     | 115 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

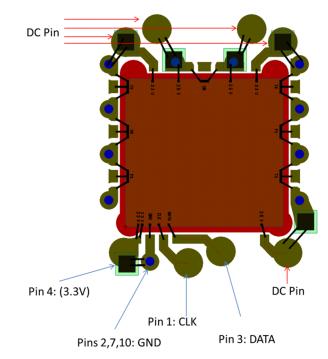

| Figure 10-3: Wire bonding and chip pins on the designed test board                                                                         | 115 |

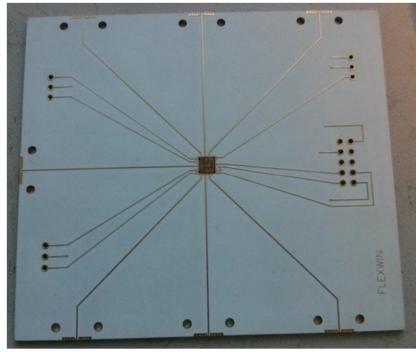

| Figure 10-4: Fabricated test board prototype with multi core chip mounted                                                                  | 116 |

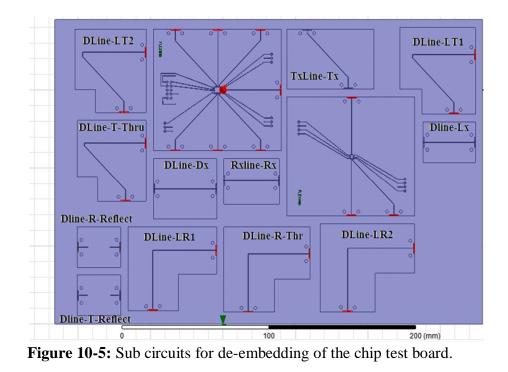

| Figure 10-5: Sub circuits for de-embedding of the chip test board                                                                          | 117 |

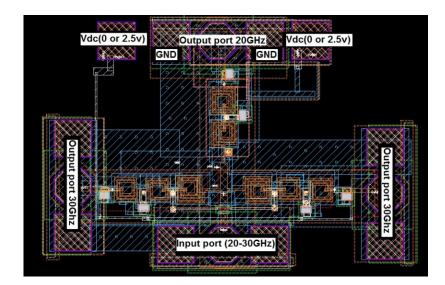

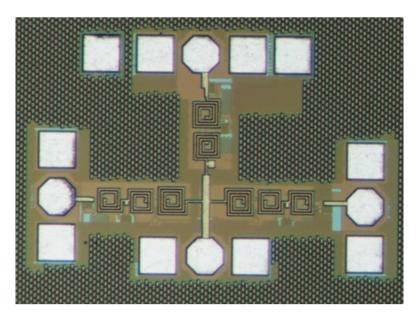

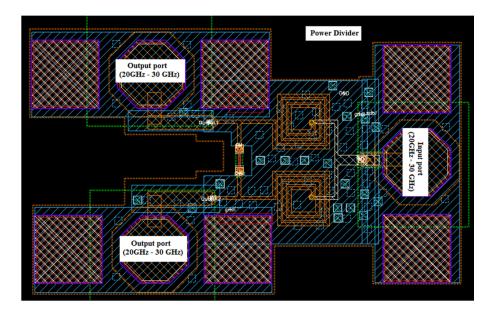

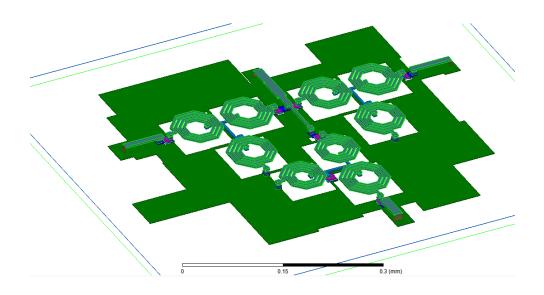

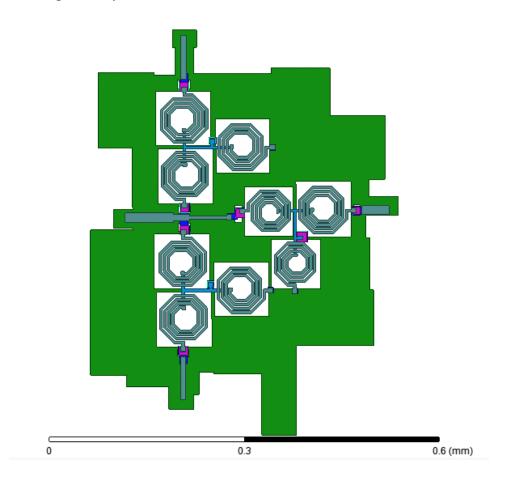

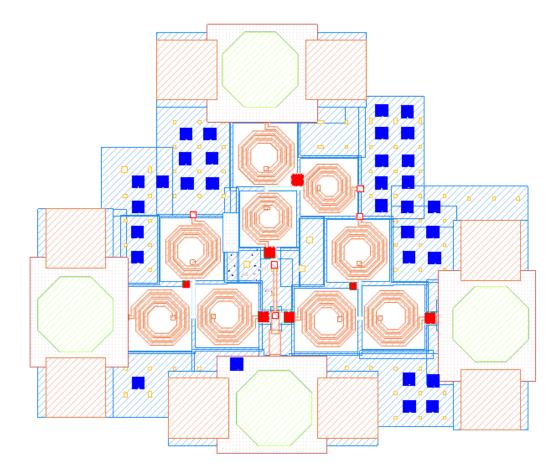

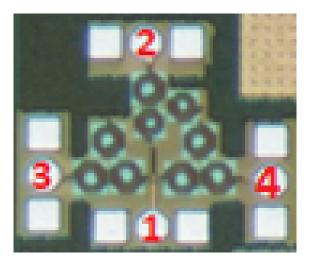

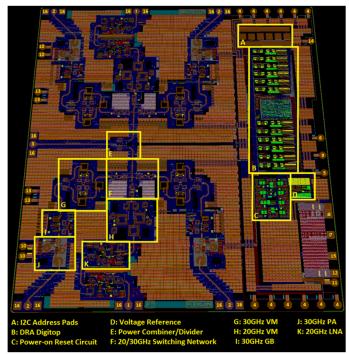

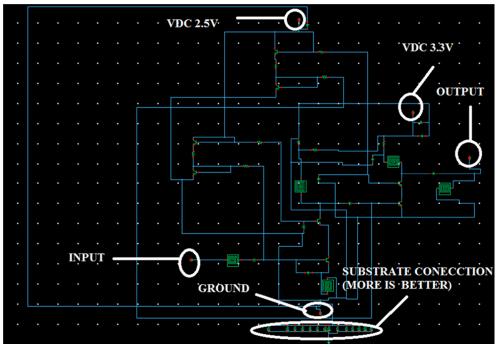

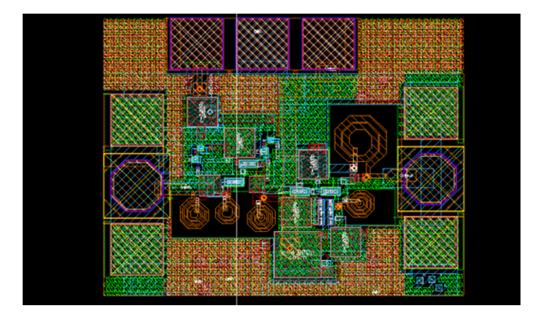

| Figure 10-6: Layout of multi core chip                                                                                                     | 118 |

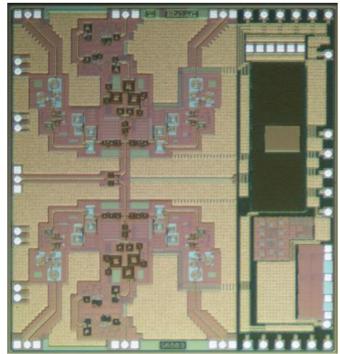

| Figure 10-7: Micro photo of multi core chip                                                                                                | 118 |

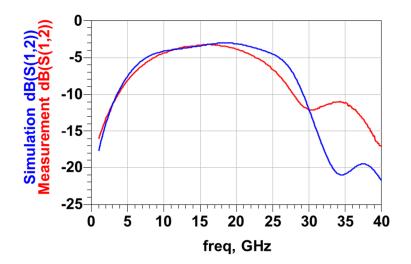

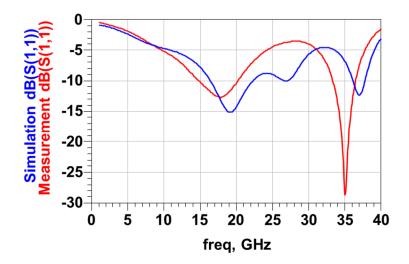

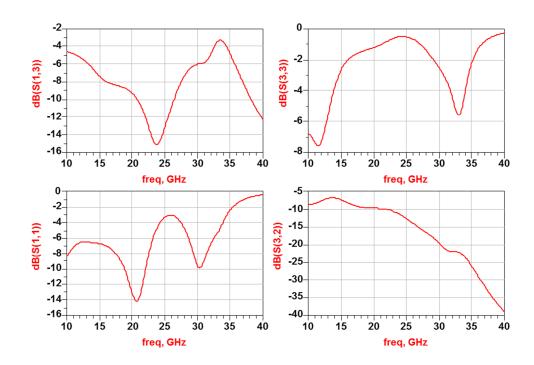

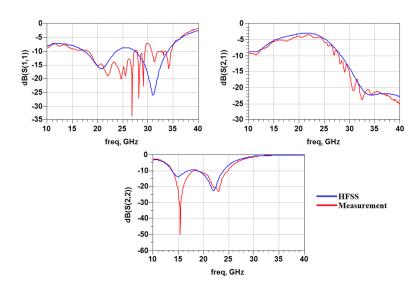

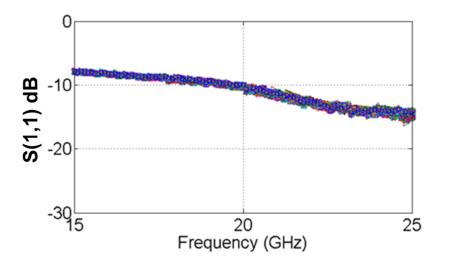

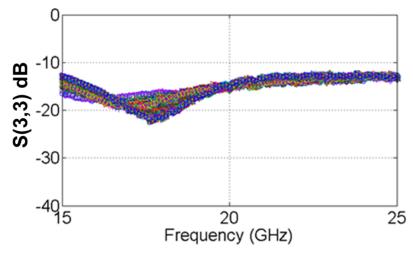

| <b>Figure 10-8:</b> Measured input matching $(S_{11})$ of the chip in RX mode                                                              | 119 |

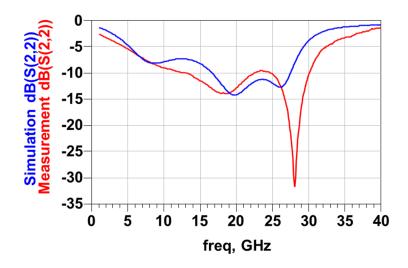

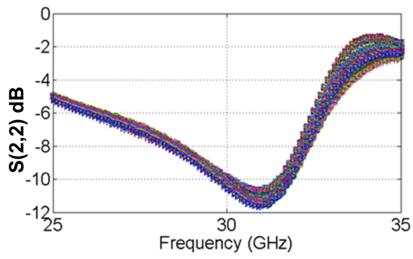

| Figure 10-9: Measured output matching (S <sub>22</sub> ) of the chip in RX mode                                                            | 120 |

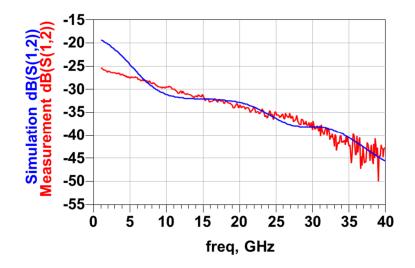

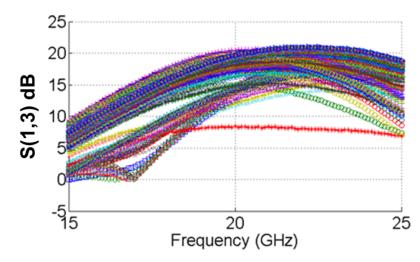

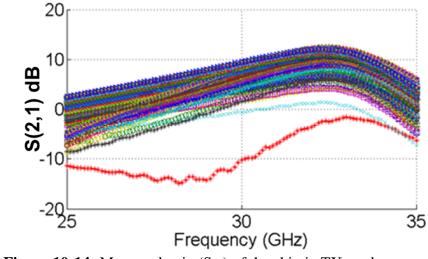

| <b>Figure 10-10:</b> Measured gain (S <sub>13</sub> ) of the chip in RX mode                                                               | 120 |

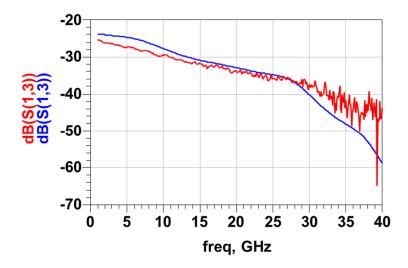

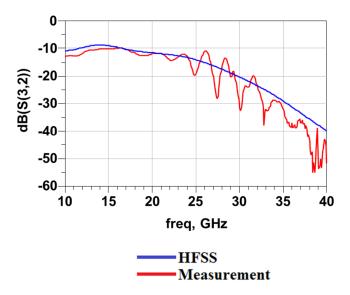

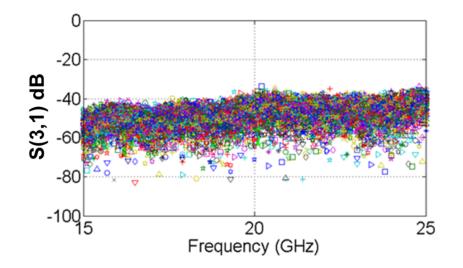

| Figure 10-11: Measured isolation (S <sub>31</sub> ) of the chip in RX mode                                                                 | 121 |

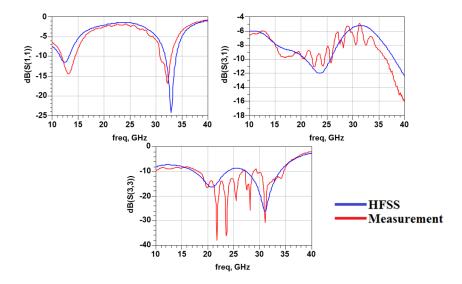

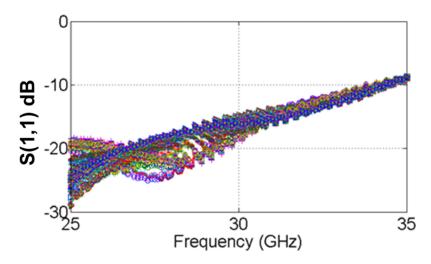

| <b>Figure 10-12:</b> Measured input matching (S <sub>11</sub> ) of the chip in TX mode                                                     | 122 |

| Figure 10-13: Measured output matching (S <sub>22</sub> ) of the chip in TX mode                                                           | 123 |

| Figure 10-14: Measured gain (S <sub>21</sub> ) of the chip in TX mode                                                                      | 123 |

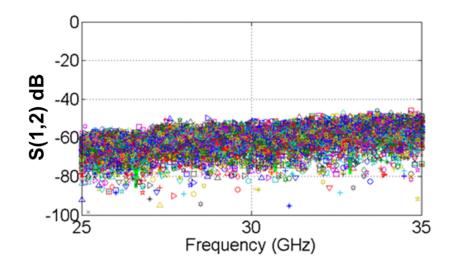

| Figure 10-15: Measured isolation (S12) of the chip in TX mode                                                                              | 124 |

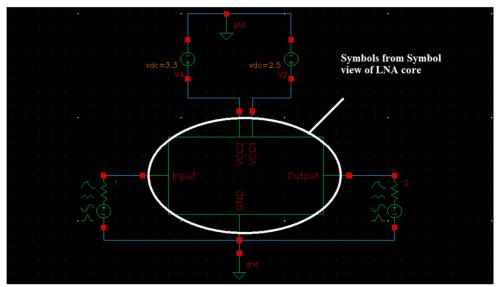

| Figure A-1: "LNA core" schematic created in Cadence.                                                                                       | 133 |

| Figure A-2: "LNA total" schematic. In the center of the schematic is located the symbol of the "LNA core" with RF ports and bias voltages. | 133 |

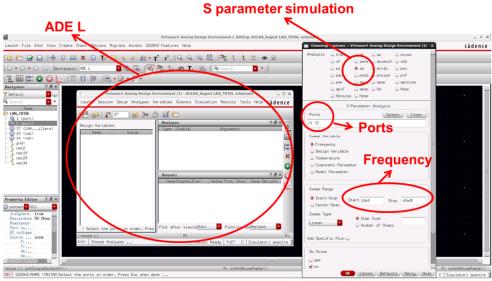

| Figure A-3: "ADE L" tool and options in Cadence.                                                                                           | 134 |

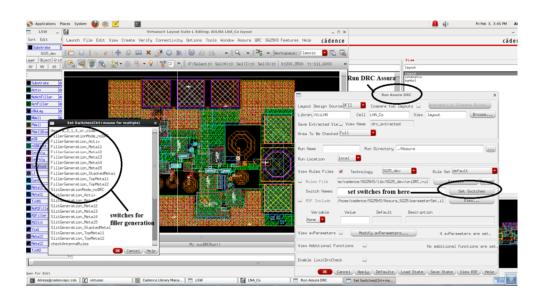

| Figure A-4: Assura DRC check.                                                                                                              | 137 |

| Figure A-5: Filler generation settings set-up.                                                                                             | 138 |

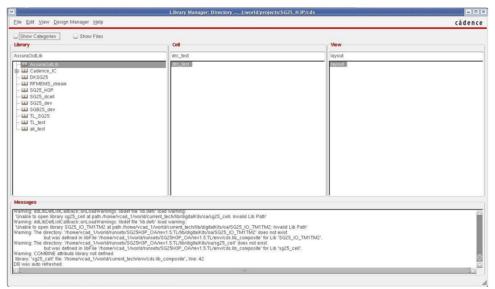

| Figure A-6: Library created automatically included the layout with fillers                                                                 | 139 |

| Figure A-7: DRC check switches in Assura.                                                                                                  | 136 |

# LIST OF TABLES

| <b>Table 3-1:</b> Physical characteristics of 0.4nH designed spiral inductor                          |

|-------------------------------------------------------------------------------------------------------|

| <b>Table 3-2:</b> Importanat parameters in piral inductor design                                      |

| Table 3-3: MiM capacitor design parameters.    31                                                     |

| Table 3-4: MMIC resistor design parameters.    35                                                     |

| Table 3-4: Resistor types and application    36                                                       |

| Table 4-1: Specifications for antenna array.    43                                                    |

| <b>Table 5-1:</b> Component values of the 20GHz LNA                                                   |

| <b>Table 5-2:</b> Components value for biasing ciruits of designed 20GHz LNA                          |

| <b>Table 7-1:</b> Geometrical parameters of the 90 degree hybrid coupler                              |

| Table 7-2: Values of the components used in the variable impedance loads.       87                    |

| Table 7-3: Components' values of the power divider-combiner shown in figure 7-789                     |

| <b>Table 8-1:</b> Initial and Optimized values of designed power divider-combiner         components. |

| Table 10-1: Stack up layers information of designed test board                                        |

| Table 10-2: Vias and drilling information of test board       114                                     |

| Table 10-3: Correspondences between measurement modes and de-embedding kits117                        |

# ACKNOWLEDGMENTS

We would like to thank the little people for making this document possible. Furthermore, we would like to thank the Academy, all of our families and friends,

## **CHAPTER 1**

### **INTRODUCTION**

#### **1.1** Introduction of Ka-band systems

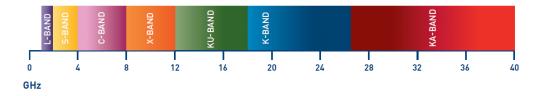

The Ka-band is the band that covers the frequencies of 26.5–40 GHz [1] [2] and it is part of the K band of the microwave band in the electromagnetic spectrum.

Figure 1-1: Frequency spectrum.

The 30/20 GHz band is used in communications satellites, uplink in either the 27.5 GHz -31 GHz bands. Ka-band has become the band of choice for many satellite operators due to its increasing capacity availability and its applicability for broadband services. The higher frequency enables the satellite spot beams to be much smaller than those typical of Ku-band. In turn, this enables the frequencies for each beam to be re-used in different spot beams without risk of interference. This significantly increases the capacity of the satellite. The latest Ka-band satellites have 38 times the data capacity of a comparable Ku-band satellite. The increasing interest for Ka-band satellite communications systems is mainly due to the following features:

- 1. **Large bandwidth**: this is the base reason for developing Ka-band satellite system in the time that lower frequency bands are congested.

- 2. **Small antenna size**: with respect to Ku-band systems, user terminal antennas can be designed to have a reduced size thus resulting in a reduction of the interference from adjacent satellite systems.

- 3. Larger system capacity: Ka-band satellites provide smaller spot-beams to increase the satellite power density and allow large frequency reuse, which help to have higher spectrum occupancy. Many user terminals can use the service simultaneously.

- 4. **Ubiquitous access**: accesses are available at any point inside the satellite footprint especially in locations where wired network are impossible or economically unfeasible.

- 5. Flexible bandwidth-on-demand capability: this characteristic maximizes the bandwidth and resource utilization, and decrease the cost to end users.

The main commercial applications operating in the Ka-band are the following[3]: emerging Voice over IP (VoIP)[4], tele-medicine, tele-education, voice, local television, VSATs, "home-use VSATs", satellite news gathering, and military intelligence. Such services are being implemented on different networks of satellites; some of them are already in orbit, such as:

- Astra 3B (2010, EADS Astrium), 4A, 1L (2007, Lockheed Martin);

- HotBird 6 (2002, Alcatel Space)

- O3b Satellite Constellation (2013-2014, Thales Alenia Space)

- Inmarsat 5 Global Xpress(2014, International Maritime Satellite Organization)

- Viasat-1 (2012, Viasat)

- Eutelsat 3D (2014, Eutelsat)

Some of the civil services that are already offered or will be offered in the near future in connection with these satellites include internet services (e.g. ViaSat, Astra2Connect, Tooway, InmarSat) or TV broadcasting (e.g. DVB-S2).

One of the most interesting and promising application of Ka-band sitcom systems is related to their use in mobile platforms such as airplanes, trains or trucks. In this context, one of the most critical aspects is related to the development of the phased-array antenna system. Indeed, as it will be clarified on Chapter 2, antenna requirements for Sat-Com user terminal are usually very challenging. Typically, it is required beam scanning over very wide angles, low interactions with the environment, dual band (Tx and Rx) operation, low-cost and low-profile.

In the most typical approach, these requirements are satisfied by employing two separated radiation apertures for the Rx and Tx channel. Pointing of the two dual-polarized antennas is usually mechanical in azimuth and electronically steered in elevation. This approach results in a complex antenna architecture which can be hardly mounted on vehicles or airplanes without affecting their aerodynamic and aesthetic profile. Furthermore, the cost of this solution remains high even for mass production. Arrays with full electronic beam scanning were proposed using customized GaAs (MMICs)[5][6]. Although this is a step in the right direction, it is still not enough to greatly reduce the cost of the user terminals. Indeed, independent silicon chips will be

required to control Tx and Rx modules and it is not possible to integrate multiples cores in the same MMIC with high yield.

This work introduces a new configuration of Ka SatCom user terminal antenna as it is being developed within the framework of the European FP7 project (FLEXWIN) [7]. The proposed configuration is based on highly reconfigurable RFIC components referred to as "intelligent pixels" combined with a quasi-planar antenna array. Each element of the array is therefore integrated with a multicore chip developed on the SiGe BiCMOS technology, where amplitude and phase control elements are integrated with environmental sensing and digital controls controlled through a I2C bus. The IHP (Innovations for High Performance Microelectronics) SiGe SG25H3 MMIC technology was employed in this work. This process provides a 0.25  $\mu$ m technology with a set of npn-HBTs ranging from a higher RF performance (fT/fmax= 110 GHz/180 GHz) to higher breakdown voltages up to 7 V.

In terms of re-configurability, this approach proposes to achieve a significant advance towards smart RF micro-systems enabling the realization of highly reconfigurable and multifunctional millimeter-wave building blocks which can be integrated with environmental sensing blocks and with digital controls.

#### **1.2** Thesis organization

In this thesis design and characterization of building blocks for a multicore chip for Sat-Com Ka-band applications will be presented. System driven requirements will be described in Chapter 2. MMIC process details will be given in Chapter 3 along with a description of passive and active components employed in the proposed designs. Satcom user terminal with electronic beam scanning and some details on the antenna array configuration will be reviewed in Chapter 4 along with link budget considerations. In Chapter 5 the design of Low Noise Amplifier (LNA) for Tx branch will be shown and the measurement results will be compared with simulations. CMOS switches and their design and limits for the application at hand will be presented in Chapter 6 introducing a new configuration for Rx/Tx switching network based on CMOS single switch. The ability to control amplitude and phase of each array element will be achieved using Vector Modulators (VM) which is presented in Chapter 7. The multicore configuration requires the use of on-chip Beam Forming Network (BFN) whose main building blocks are power combiners which will be presented in Chapter 8. As an alternative to switching networks, a diplexer network was designed and tested as shown in Chapter 9. For the characterization of the multicore chips specific test boards have been designed and prototyped as described in Chapter 10. This chapter will also provide a summary of the hexa-chip measurements.

## **CHAPTER 2**

## **KA-BAND SATCOM SYSTEMS**

#### 2.1 A Ka-band systems

The term Ka-band system is not just related to the operating band but it is recognized as a shorthand term for a new generation of communications satellites that encompasses a number of innovative technologies such as on-board processing (OBP) for multimedia applications[8], and switching to provide full two way services to and from small ground terminals[9]. To do this efficiently, multiple pencils like spot beams are employed and, in some cases, inter-satellite links are also used [10]. Apart from the conventional geo-stationary orbit; both low ground and middle ground orbit systems have been planned[11]. Ka-band satellite systems have also been known as multimedia satellites or ATM satellites or broadband switched and broadband interactive satellites. The multimedia and ATM are generally inaccurate as Ka-band satellites can be used for other applications than multimedia or ATM platform. The term "ATM Satellite" is also incorrect because on-board switching can involve either ATM switching or circuit switching or both. In other words on-board processing and switching are already employed in satellites providing mobile communications to handheld receivers.

There are several experimental Ka-band satellites such as ITALSAT (Italy), ACTS (US), DFS (Germany) and Olympus (European Space Agency), as well as commercial

communications systems, to help solving the problem of saturation of the available orbital slots at C and Ku-band and also to provide new services for different type of users[12].There are many challenges for using Ka-Band SatCom systems that depend on the application context. One of the most interesting Ka-band applications is related to the establishment of high capacity links for users in a mobile platform such as an airplane, ship, train or truck. For this application, the most critical element in the system is the user terminal antenna which must be designed to reach several critical requirements such as:

- interactions with the aircraft aerodynamics which mainly results in changes of drag and lift and which can be extremely critical with dish antennas;

- very wide angle scanning performance, e.g. operation on polar routes;

- uninterruptible communication links, whatever the trajectory, aircraft man oeuvres and flight attitude;

- operate at both frequency bands (up-link and down-link);

- costs due to antenna architecture (active phased arrays) or manufacturer monopoly.

An ideal antenna architecture, capable to meet all previous requirements, would consequently bring decisive advantages over existing solutions by combining the following capabilities:

- broadband data transmission capability in transmit and receive operation;

- low profile and low weight;

- big coverage areas enough to guarantee service availability on all main flight routes;

- advanced beam steering capabilities;

• low cost;

It is widely known that active phased array antennas are likely the most promising candidate to fulfill many of the above mentioned challenges, except for the cost aspect. Furthermore, the design of a compact, fully integrated phased array at Ka-band poses several technological challenges which have not been yet fully solved. For this reason, mechanically steerable parabolic reflectors are still used in many Ka-band systems, even on the move platforms. There are some efforts have been made to fabricate electronically or mechanically tracking terminals. As a result, there are three main options for the design of a Ka-band user terminal antenna:

- fully mechanical;

- electromechanical;

- fully electronic.

#### 2.2 SatCom user terminal antennas

Mobile SatCom systems introduce new complexities in the design of on move terminals antennas. The direct line-of-sight between antenna and satellite antenna requires the antenna to see from horizon to overhead (zenith -90) in elevation and 360 in azimuth angle, with total hemispherical coverage. This is actualized in the case of transceiver antenna through the application of moveable rotatable high-gain antennas to attain full coverage.

The moveable antenna itself imposes even more stringent requirements. Therefore, in spite of constant vibrating, pitching, rolling and yawing the Mobile SatCom antenna's narrow radiation beam must be pointed accurately to satellite.

Since 1970, satellite communications developed quickly aiming at replacing HF radio with the new Fltsatcom military mobile system. For instance, since this time several types of UHF antennas developed were used, such as the crossed-dipole array, its improved version and the so-called wash-tube similar to an SBF antenna and one type of SHF parabolic dish antenna. However, the first real global Mobile SatCom system was the Marisat system, which used SES and L-band antenna systems similar to current Inmarsat-A and B terminals.

Mobile antennas have to satisfy the requirements of some characteristics in relation to construction strength, easy installation and cost. Easy installation and appropriate physical shape are very important requirements in addition to compactness and lightweight. In the case of moveable SatCom antennas, the installation requirements are strongly depend on application and place to install for example to that of aircraft and cars is different with ships because even in small ships there is a enough space to install an antenna. Otherwise, the only problem is because all types of ships satellite antennas are sometimes under stress from vibration and sloping caused by storms, rolling and pitch or is subject to corrosion by salt. To avoid these problems, a ship's antenna has to be protected by plastic cover (radome) and properly installed on a strong mast, which is suitable for a certain size of antenna. However, in the case of road vehicles, especially small cars, low profile and lightweight equipment is preferred. In the case of aircraft, more conditions are required to satisfy standards. Such as low air drag that is one of the most important requirements for aircraft antennas. Vehicles and aircraft need smaller and more aerodynamic antenna. Several different type of antenna can be used in array to provide a desired radiation pattern. This type of antenna is called an array antenna that

consist of more than two elements; this can be done by different types of antennas, such as microstrip, cross-slot, cross-dipole, helixes or other antennas elements and is suitable for move able SatCom systems. Each element of an array antenna can be excited by different amplitude and phase to obtain desired radiation pattern.

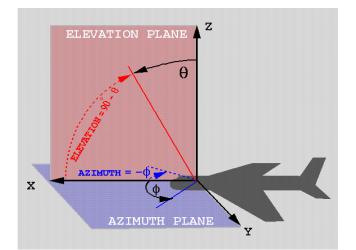

The pointing direction of the SatCom user terminal antenna can be defined in terms of azimuth and elevation angles:

- Azimuth Angle – The azimuth is the angle between North line and horizontal satellite direction as seen from the antenna, as shown in Figure 2-1. Thus, the actual azimuth angle for the various satellites due to the antenna's (airplane) plotted position can be found.

- Elevation Angle – The elevation angle is the satellite height above the horizon as seen from the antenna, as shown in Figure 2-1. In this case, the actual elevation angle for the various satellites due to the antenna's (airplane) plotted position can be found.

Figure 2-1: HGA Coordinate System. (www.matis.net)

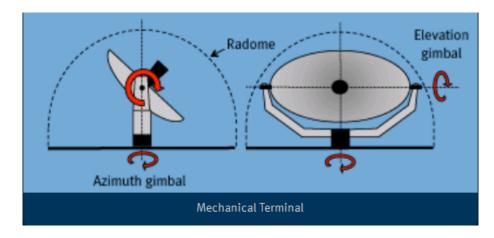

### 2.2.1 Fully mechanical pointing

In this category of antennas we put the type of the antennas whose beam is steered directions (elevation and azimuth). The main challenge is that these user terminals antennas need a precise mechanical pointing system to point precisely at a defined satellite in the sky [13]. The ITU (International Telecommunication Union), FCC (Federal Communications Commission), ETSI (European Telecommunications Standards Institute) and other regulatory agencies have very strict alignment requirements for satellite antennas in order to avoid interference. The pointing for Ka-band user terminal antennas require to point a target in the sky that is too small [14]. Despite these challenges, many companies have successfully developed "mechanical" antenna terminals that have been used on a wide variety of mobile systems. The first fully mechanical pointing is used usually for reflector antenna parabola antenna and etc. However they have some disadvantages that include:

- Cost

- Large form factor

- Weight

- Power usage

- Difficult to install

Figure 2-2: Mechanical Antenna pointing (www.kymetacorp.com).

The mechanical pointing systems that can be described by the following set of parameters

- Pointing resolution is defined as the minimum antenna beam movement step in azimuth or elevation;

- Sensitivity is defined as the beam changing in direction per unit of actuator adjustment;

- Hysteresis (backlash) span is defined as the difference between actual beam direction for a given actuator setting position after being approached with two opposite directions;

- Lock-down shift is defined as the azimuth-elevation vector changes when the locking fasteners are tightened after all final adjustments have been made.

The main error sources are:

- Absolute azimuth and elevation errors are defined as the difference between the scale readings and the absolute values of azimuth and elevation.

- Boresight-axis misalignment use to asymmetric antennas that is defined as the angular difference between the optical boresight and the skew axis of rotation that

may occur caused by a different factors such as reflector shape errors, accuracy of mounting points of the reflector, and feed position errors.

- Vertical plumb error is known as the difference between the azimuth axis of rotation and the local vertical axis. This usually occurs because of foundation or base pole being not perfectly leveled.

- Beam squint for circularly polarized antennas, is defined as plus and minus half of the difference between the LHCP and RHCP main beam directions. The squint angle is on the order of +/- 0.15° step for an antenna.[16]

- Moreover the above static errors, sources of dynamic error change by time. They include:

- Wind deflection. One of important physical design point of the antenna is stiffness against reflector wind load versus cost, weight, and complexity.

- Unequal solar heating of the reflector antenna. At different position of sun, the shadow of the edge of a large reflector can take a long time to traverse the width of the reflector. During this time, the sunlit portion of the reflector dissipates greater solar heat load than the shadowed portion.

- Foundation settling is known as changes vertical plumb error over time.

- Station keeping is defined as small changing of the satellite with respect to the earth.[17]

#### 2.2.2 Electronic elevation and mechanical azimuth pointing

One of efficient way to point the beam of the antenna in satellite communication is to use hybrid pointing methods (e.g. electromechanically steerable antennas). It means that in one direction the antenna can be routed mechanically and in other direction electronically. Mechanical routing to cover azimuth direction can be done by router or mechanical arm. In elevation beam steering can be done by changing the phase and amplitude of feeding. The goal of this procedure is to keep the beam direction on the desired satellite.

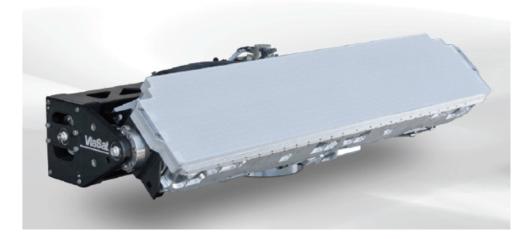

Viasat aero mobile terminal 2540/2532 is an example of this type of antennas that operate in Ka-band and can be mounted permanently on fuselage of aircraft. The array is Kaband dual polarized horn array and Rx/Tx integrated circuit embedded into the aperture to increase the gain of array as shown in figure 2-3.

Figure 2-3: Viasat aperture array antenna.(www.viasat.com).

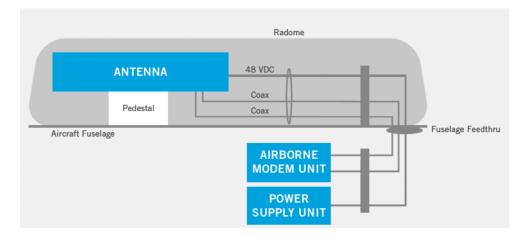

Maximum weight of this antenna is 34 kg and the maximum height is 0.22 m. It consume 180 W from the 48v DC power supply that cause antenna gain-to-noise-temperature (G/T) around 12.5 dB/K. Azimuth coverage of this antenna is from 0 to 360 degree and Elevation coverage is from 0 to 75 degree. Tx mode frequency band is 28.1-30 GHz and Rx operate from 18.3 to 20 GHz. The overall antenna cover with plastic cover (radome) and connected to power supply and modem unit as shown in figure 2-4.[18]

Figure 2-4: System diagram of Viasat antenna.(www.viasat.com).

#### 2.2.3 Other emerging trends

One of the emerging need for SatCom on the move systems is related to the possibility to have a user terminal antenna flat, easy to fabricate and to calibrate and less expensive than the systems currently in use. The configuration which is most well suited for these requirements is based on fully-electronically scanned antenna arrays. Electronic pointing has some advantages that are listed below:

- high gain width less side lobes;

- ability to switch the beam to from one target to other target in a few microseconds;

- ability to provide an directive beam under computer control;

- free eligible Dwell Time.

On the other hand fully electronically beam pointing has some limits and disadvantages that are:

- the coverage is limited to constant degree steps in azimuth and elevation;

- deformation of the beam in the case of deflection;

- low frequency agility;

- very complex structure (processor, phase shifters);

- still high costs;

Example of existing electronically beam pointing is a VICTS antennas with digital beam forming network. Thin Kom's VICTS antenna technology provide a broadband, low profile, and effective cost for on -the-move connectivity challenges. Thin Kom's VICTS antennas can steer 360° in azimuth and 90° in elevation, allow us to have continuous and reliable tracking for all users' needs and is compatible with DBS providers. Satellite internet and other satellite data streaming needs can be realized with thin Kom's VICTS antenna technology. The VICTS antenna is shown in Figure2-5. [19]

Figure 2-5: LTCC frontend antenna circuitries (IMST GmbH, Germany).

### 2.3 **Objective of the thesis**

In this thesis, a fully electronic beam scanning solution for Ka-band user terminals is investigated. The proposed configuration is based on printed radiating elements combined with multi-core SiGe core chips which enable full control of amplitude and phase on each element of the array.

For many years, the main emphasis of SiGe MMIC development was on demonstrating individual function blocks, showing that typical GaAs MMIC components such as low-noise amplifiers, up- or down-converters can also be fabricated on Silicon substrates. However, it turns out that for small and medium volumes, the cost of Silicon-based MMICs is actually higher than for their GaAs counterparts. This has to do with the more complex technology and hence larger number of mask levels, with the larger sizes of Si wafers (which can be a curse for small markets), and also the higher minimum number of wafers per batch in Silicon processing.

The true advantage of Silicon-based MMICs appears when increasing complexity. Here, Si/SiGe BiCMOS as well as RFCMOS benefit from

- The higher processing maturity and yield,

- The higher thermal conductivity of Silicon vs. GaAs (1.5 vs. 0.46 W/cmK at 300K) which allows much denser on-chip packing of active components.

- Suitable for low noise applications such as LNAs due to better noise behavior vs GaAs

## **CHAPTER 3**

### **IHP 0.13UM SIGE BICMOS PROCESS TECHNOLOGY**

#### **3.1 MMIC Introduction**

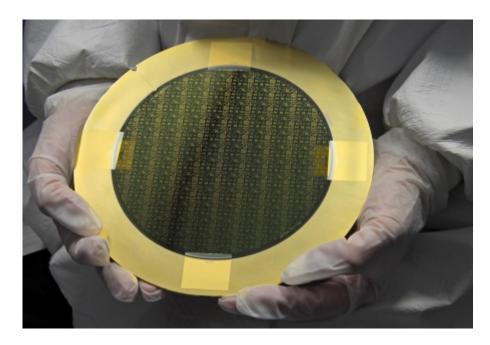

A Monolithic Microwave Integrated Circuit or MMIC is an integrated circuit (IC) operating at microwave frequencies (300 MHz to 300 GHz) which active and passive components are fabricated on one semiconductor substrate. Due to monolithic characteristic, MMICs as fabricated as small parts of whole semiconductor wafer. MMIC wafer is shown in figure 3-1. The process of the wafers is forming of micrometric or even nanometric features on their surface. Because of this reason fabrication process is costly and time consuming. MMIC technology provides the core components for many applications of microwave and telecommunication. There are some advantages of applying MMIC technology that listed below [20]:

- Cheap in large quantities, especially for complex circuits

- Good reproducibility

- Small

- Light

- Less parasitic

- Larger bandwidth

MMICs were usually fabricated using gallium arsenide (GaAs), an III-V compound semiconductor. GaAs has two advantages as compare as Silicon (Si), the usual material for IC realization: device (transistor) speed and another one is semi-insulating substrate. Both of them help to design of Microwave frequency circuit functions. However, the speed of SiGe-based technologies has increased as transistors feature sizes have reduced and MMICs can now also be fabricated in SiGe technology. The advances in silicon transistor performance from 1998 to 2004, for both the MOSFET and the Silicon Germanium (SiGe) HBT processes, coupled with the high integration density of five to seven metal layers, have allowed high performance MMICs to be developed at microwave and even millimeter-wave (mm-wave) frequencies. For the SiGe technology, the transistor maximum (unity gain) frequency ft in standard commercial runs increased from 40 to 50 GHz in 1998 to >200 GHz in 2004 [21]. By 2005, M/A-COM completed the development of an automotive SiGe 24-GHz radar transceiver with 2 GHz of instantaneous bandwidth [22], and IBM demonstrated a 60-GHz short-range communication system capable of handling more than 3 Gb/s [23]. In 2003 and in 2005, Army Research Laboratories and Defense Advanced Research Projects the Administration (DARPA) asked [24]: Silicon RFICs be used to lower the cost of phased arrays for defense applications, especially at X/Ku/K-bands and also at mm-wave frequencies, while still maintaining all the functionality (noise figure (NF), power, bandwidth, etc.) of phased arrays are challenging.

In order to design MMICs, it is necessary to have precise characterization/ modeling of elements (mainly FETs) and impedance analysis based upon it, circuit design suitable to

monolithic integration, and element and device fabrication technology appropriate to microwave frequencies and above [25].

Figure 3-1: MMIC wafers. (www.microwave-eetimes.com).

In this chapter, we'll briefly present the most relevant elements of the SG25H3 IHP (Innovations for High Performance Microelectronics) SiGe BiCMOS technology which is currently used in many research and industrial projects to develop RF circuits for wireless telecommunications and broadband communications, aerospace, automotive, security and automation applications [26]. In this project, IHP SiGe BiCMOS technology has been used for realization of the multi-core RFIC chip and related sub-circuits.

## 3.2 SG25H3 process

SG25 is the basic 0.25  $\mu$ m CMOS process. It provides NMOS, PMOS, isolated NMOS and passive components such as poly resistors and MIM capacitors. In addition to the

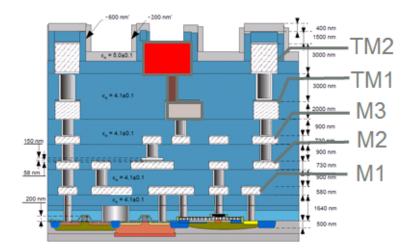

basic CMOS process 3 frontend options and 2 aluminum backend options are offered. The IHP SG25H3 0.25  $\mu$ m microwave bipolar complementary metal oxide semiconductor (BiCMOS) process offers high-performance technology with SiGe hetero junction bipolar transistors (HBT) up to fT/fmax = 110 GHz /180 GHz and HBTs with higher breakdown voltages up to 7 V. The technology is suited for applications between 24 GHz and 60 GHz, making it especially useful for the designers of wireless, broadband and radar products. SG25H3 is one of a 0.25  $\mu$ m and 0.13  $\mu$ m BiCMOS technology set with HBTs up to 300 GHz fmax that IHP offers customers for Multi Project Wafer and Prototyping Services. The standard backend option offers 3 thin metal layers and two Top Metal layers (Top-Metal1 - fourth 2  $\mu$ m thick metal layer, TopMetal2 – fifth 3  $\mu$ m thick metal layer) and a MiM layer. Together with a high dielectric stack this enables increased RF passive component performance. In next sections we will provide more detailed information about this technology. Stack up of SG25H3 technology with 5 metallization layers illustrates in figure 3-2.

**Figure 3-2:** Stack up of SG25H3 technology with 5 metal layers (www.ihp-microelectronics.com).

## **3.2.1** Active components

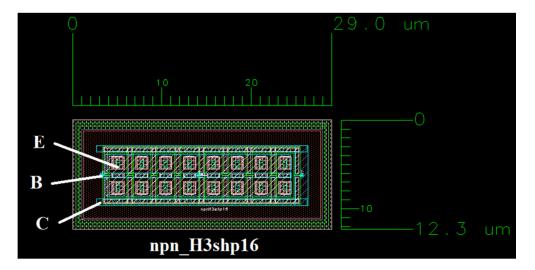

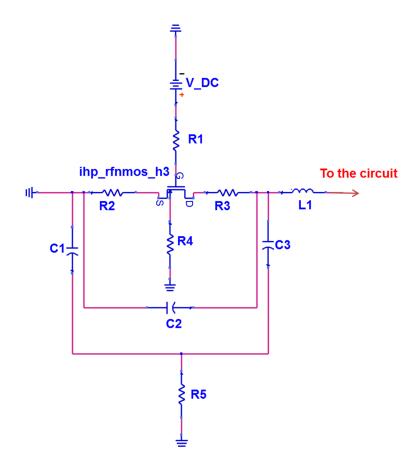

Active components provided in SG25H3 technology are divided in two main categories: bipolar (BJT) devices and CMOS (FET) devices. There are several types of BJT included in the SG25H3 Design Kit (DK). The basic selection parameters are related to the number of collector and to the maximum current handling. For instance, the BJT component ihp\_npnH3shp1 can handle a collector current of 2mA while the ihp\_npnH3shp2 can handle 4mA. The maximum current handling capabilities are obtained with the ihp\_npnH3shp16 (figure3-3) that can operate until a maximum of 32mA. This type of components is widely used in the design of Low Noise Amplifiers and in power amplifiers. CMOS devises also divided to 2 main groups: NMOS and PMOS. Each component has three main design parameters which are the width, the length and the number of gates. For an example ihp\_rfnmos\_h3 is the NMOS device that is frequently used in RFIC components design such as switches or vector modulators with different number of the gates.

**Figure 3-3:** Layout of ihp\_npnH3shp16 bipolar transistor with 16 emitters as it is provided in the IHP SG25H3 design kit.

#### **3.2.2 Passive components**

A lumped passive component in a microwave circuit is defined as microwave element whose size across any dimension is much smaller than the operating wavelength. In other words, in lumped elements there is no appreciable phase shift between the input and the output phase. Usually for good approximation the maximum dimension must be less than  $\lambda/20$  [27].

In the following sections it is reported a brief description of inductors (L), capacitors (C) and resistors along with their basic characteristics.

## 3.2.2.1 *Inductors*

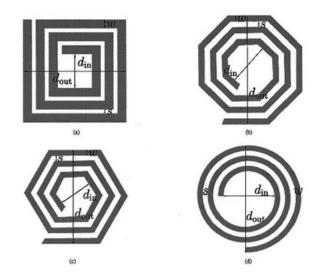

An ideal inductor stores or releases magnetic energy and does not store electric energy which is typically associated with capacitive effects. Ideally, an inductance does not dissipate any power because it does not have any resistive loss. Magnetic energy is stored as long as current flow remains through the inductor. However realizing inductor with low capacitance or resistance effect on SiGe chip is still challenging. Generally inductors can be realized in several ways such as wire bond, single loop or spiral. The printed spiral inductor can be used for on-chip applications because they are smaller than the other types and also their fabrication is easier. On the other hand, the inductance value of spiral inductors can be controlled by different geometrical parameters of the spiral. There are typically four geometries that can be used to create spiral inductors (figure3-4):

- Rectangular

- Hexagonal

- Octagonal

- Circular

**Figure 3-4:** Planar spiral inductor layouts (a) Square (b) Octagonal (c) Hexagonal (d) Circular (www.vlsi.itu.edu.tr)..

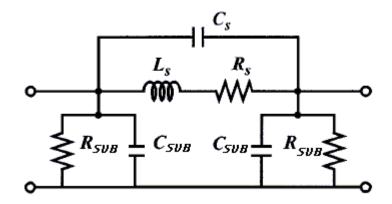

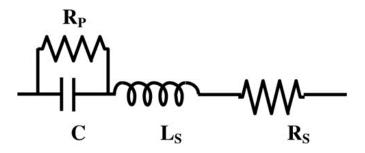

To satisfy the layout design rules that provided by IHP for SG25H3 technology, circular and hexagonal spirals cannot be used. Top metal 1 and Top metal 2 are used for realizing the inductor to increase the amount of the inductance while size reducing. In Metal 1 it is usually printed the inductor ground plane which can be a solid rectangle with slits, a rectangular ring or a periodic structure. Air bridges are realized by arrays of vias from Top Metal 2 to Top Metal 1. The use of arrays reduces the total resistance of the inductor and improves its reliability. The equivalent model of printed spiral inductors is shown in figure 3-5 and it consists of a capacitance between inductor and ground and capacitance between inductor input and output terminals. There is also series resistance,  $R_S$ , that models the losses in conductor and dielectric.

Figure 3-5: Spiral inductor model.

Important parameters that can effect of value of inductance are listed below.

- Number of turns (N)

- Spacing between turns (s)

- Turn width (W)

- Outer Diameter (dout)

- Inner diameter (din)

To obtain a certain amount of inductance at the desired frequency band, physical dimensions must be optimized. A first guess of the geometrical parameters can be obtained using an analytical expression [28]. However, in case of SG25H3 technology it is not possible to apply any closed formula because the thickness of the metals is considerable with respect to the substrate.

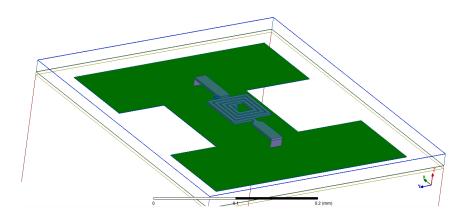

Usually, full wave EM simulations are used to fine tune the inductance value of spiral inductors [29]. An example of spiral inductor with inductance of 0.4 nH is shown in figure 3-6 and Physical characteristics are shown in table 3-1. Top metal 2 is used for main path and top metal 1 is used for under path to have maximum distance between inductor and reference plane in metal 1. The array of 9 vias from top metal 2 to top metal

1 used to decrease the overall resistance and, in turn, to increase the quality factor of the inductor.

Figure 3-6: L=0.4 nH spiral inductor HFSS model.

**Table 3-1:** Physical characteristics of 0.4nH designed spiral inductor.

| Number of turns        | 4     |

|------------------------|-------|

| Width of inductor line | 4 um  |

| Spacing between lines  | 2 um  |

| Width of spiral        | 68 um |

| Length of spiral       | 83 um |

The unwanted capacitance and parasitic effects usually occurs due to the small gap between turns. To reduce these effects the distance between turns can be increased. However this might significantly increase the overall size of inductor

Typically, several parameters are considered to design inductors as listed in table3-2.

| Effective inductance     | nominal inductance                         |  |

|--------------------------|--------------------------------------------|--|

| Impedance                | impedance of the inductance                |  |

|                          | ratio of energy stored to power dissipated |  |

| Quality factor           | in the inductor                            |  |

|                          | frequency that imaginary part of input     |  |

| Self-resonance frequency | impedance of inductance became zero        |  |

|                          | maximum current that inductor can          |  |

| Maximum current rating   | handle due to design role provided by ihp  |  |

|                          | SG25H3 technology                          |  |

**Table 3-2:** Importanat parameters in piral inductor design.

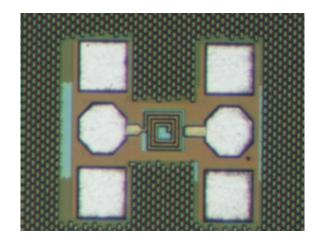

An example of fabricated 0.4nH spiral inductor is shown in figure 3-7.

Figure 3-7: Micro photo of 0.4nH rectangular spiral inductor shown in figure 3-6.

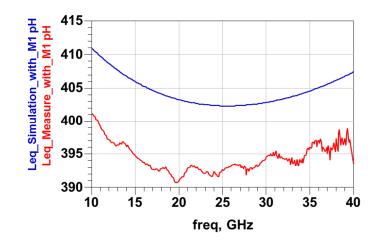

The effective inductance values obtained from simulations and measurements are shown in figure 3-8. As it can be observed, there is a very good agreement between the numerical and the experimental results. Furthermore, it can be noticed that the amount of the inductance remains stable over frequency.

**Figure 3-8:** Simulation and measurement results of the inductance of the 0.4nH spiral inductor shown in figure 3-7.

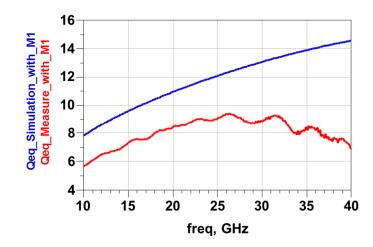

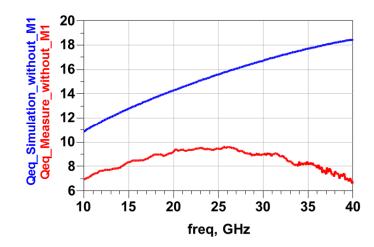

The measured and simulated quality factor of 0.4nH spiral inductor is shown in figure 3-9. As it can be seen, there is a small difference between the simulation and the measurement results which is mainly due to simulation inaccuracies The measured and simulated results of the same spiral inductor without ground plane located in metal1 are shown in figure 3-10 and figure 3-11. The quality factor and also the value of inductance of spiral inductor without ground plane in metal 1 is higher as compare as the case that metal 1 considered as a ground.

Figure 3-9: Quality factor of simulation and measured 0.4nH spiral inductor.

**Figure 3-10:** Simulation and measurement results of the inductance of the spiral inductor shown in figure 3-7 without metal 1 below.

**Figure 3-11:** Quality factor of simulation and measured spiral inductor without metal 1 below.

#### **3.2.3** MiM Capacitors

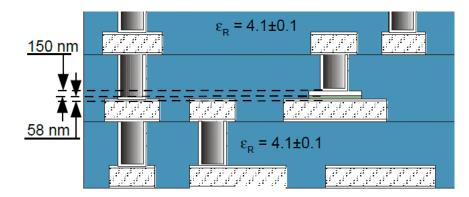

Capacitance is defined as the capacity to store energy in an electrical field between two conductors. The value of capacitance strongly depends on the area of the electrodes and on the dielectric material between the two electrodes. The capacitor might have two or more conductors (series or parallel capacitance). There are different methods to realize the capacitance that can be used in MMIC applications including MiM (metalinsulator-metal) capacitors, microstrip capacitors, inter-digital capacitors [30]. Generally, the most useful method in SiGe chips is to use MiM capacitors [31]. MiM capacitors are realized in SG25H3 technology by two very metal layers with an interlayer distance of 58nm. The lower layer is metal 2 and the upper layer is a very thin metal layer of thickness 150 nm that is connected to metal 3 with arrays of vias. In other words, the MiM capacitor is accessible from metal 2 and metal 3 as shown in figure 3-12. The MiM capacitor dielectric constant is 7.3 thus helping to reach higher values of capacitance in small areas

Figure 3-12: MiM capacitor realization in SG25H3 technology.

MiM capacitors main geometrical parameters are listed in table 3-3.

Table 3-3: MiM capacitor design parameters.

| Parameter             | Definition                                |  |

|-----------------------|-------------------------------------------|--|

| Capacitor value       | typical value for capacitance             |  |

| Effective capacitance | nominal capacitance value                 |  |

| Tolerances            | the accuracy provided by technology       |  |

|                       | ratio that shows the capability of energy |  |

| Quality factor        | storing in MiM capacitor                  |  |

|                       | maximum voltage that can be applied to    |  |

| Rated voltage         | capacitor terminals without destroying    |  |

|                       | dielectric or conductors                  |  |

| Rated current         | maximum current that MiM capacitor        |  |

|                       | conductor plates can handle               |  |

The most important parameter to obtain a determined value of capacitance is the conductor plate size that can provide minimum 29 fF up to maximum 4.7pF. The equivalent model of MiM capacitors, shown in figure 3-13, includes series and parallel resistance and small series inductance that came from conductor loss and dielectric losses.

Figure 3-13: Equivalent circuit model of capacitor.

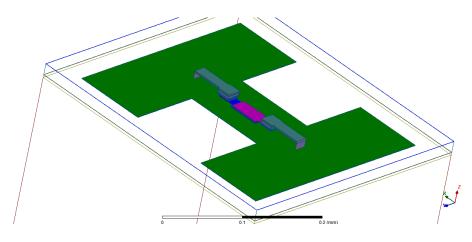

HFSS model of 1pF MiM capacitor is shown in figure 3-14. Metal 1 is considered as a reference plane for MiM capacitor and electrodes are accessible from metal 2 and metal 3.

Figure 3-14: HFSS model of 1pF MiM capacitor.

The approximate value of capacitance obtain from Eq.3-1

$$Ceq = \frac{\varepsilon A}{d}$$

Eq. 3-1

Where  $\varepsilon$  is the Permittivity of material between plates, A is the area of metal plate and *d* is the separation of the electrodes that in SG25H3 technology  $\varepsilon_r$  is 7.3 and *d* is equal to 58 nm. Micro photo of fabricated prototype is shown in figure 3-15.

Figure 3-15: Micro photo of fabricated prototype of 1pF MiM capacitor.

Simulation and measurement results of a 1pF MiM capacitor are shown in figure 3-16 and figure 3-17.

Figure 3-16: S<sub>21</sub> of simulation and measurement of 1pF MiM capacitor.

Figure 3-17: S<sub>11</sub> of simulation and measurement of 1pF MiM capacitor.

## 3.2.4 Resistors

Lumped element resistors are widely used in MMIC and RF IC applications. Resistors can be employed for several types of applications such as terminations, isolation resistors, feedback network resistor, impedance matching network or biasing networks [32].

The main parameters to be considered in the design of MMIC resistors are listed in table3-4:

| Parameter                             | Definition                              |  |

|---------------------------------------|-----------------------------------------|--|

| Resistance value                      | typical value for capacitance           |  |

| Maximum current handling capacity     | maximum current that MMIC resistor can  |  |

|                                       | handle                                  |  |

| Size of resistance                    | the physical dimensions of resistor     |  |

| Nominal tolerance                     | the accuracy provided by technology     |  |

| Temperature coefficient of resistance | the ratio that shows the resistor value |  |

|                                       | change by temperature changes           |  |

Table 3-4: MMIC resistor design parameters.

In SG25H3 technology resistances are realized by lossy material on a dielectric base that provides variable resistance depending on the size and the type of materials. Resistors in this technology are divided into four categories which cover different ranges of resistors and different maximum currents. The four types of resistors are listed in table 3-4.

| Table 3-5: Resis | or types and | application |

|------------------|--------------|-------------|

|------------------|--------------|-------------|

| Resistor type | Application                                        |  |

|---------------|----------------------------------------------------|--|

|               | used for small resistance value smaller than 500   |  |

| Ihp_rsill_h3  | ohm. Sheet resistance is 7 ohm                     |  |

|               | used for small and medium resistance value         |  |

| Ihp_rpnd_h3   | smaller than 4 K ohm. Sheet resistance is 210 ohm  |  |

|               | used for medium and big resistance value bigger    |  |

| Ihp_rppd_h3   | than 2 K ohm. Sheet resistance is 280 ohm          |  |

|               | used for big resistance value bigger than 5 K ohm. |  |

| Ihp_rhigh_h3  | Sheet resistance is 1.6 K ohm.                     |  |

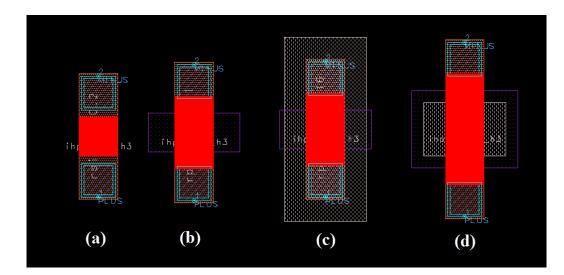

The layouts of the different types of resistance are shown in figure 3-18.

**Figure 3-18:** Layout of (a) ihp\_rsill (b) ihp\_rpnd (c) ihp\_rppd (d) ihp\_rhgh.

## **CHAPTER 4**

# SATCOM USER TERMINAL WITH ELECTRONIC BEAM SCANNING

#### 4.1 Antenna array configuration

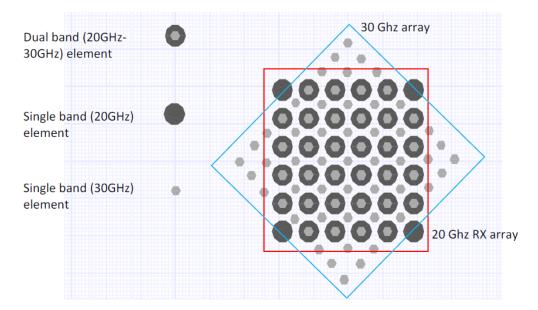

According to the SatCom specifications as given in chapter 2 we decided to use direct radiating array with electronic beam scanning. The direct radiating array is designed to have dual-band operation, i.e., 19.7 GHz – 21.0 GHz for receive and 29.5 GHZ – 30.8 GHz for transmit. It is expected that this array exhibits beam scan capability up to  $60^{\circ}$  in both elevation and azimuth planes. In order to avoid grating lobes, the distance between adjacent elements must be maintained at about  $0.5\lambda$ . Such characteristics can be obtained considering an array of dual band and single band elements interleaved in the array. Difficulties result from the RX-TX frequencies of operation which, for the application being considered, are in a ratio of 2/3. Two main issues must be tacked to account: 1) the identification of an array topology able to accommodate the elements in a way that they are spaced at about half a wavelength at both frequencies; 2) the design of a dual band element compact enough to be placed in the array. Furthermore, elements have to be designed reducing coupling between radiators and between feeding lines to a minimum, in particular coupling between RX elements, coupling between TX elements and coupling between TX and RX elements must be minimized.

Figure 4-1: Antenna array layout.

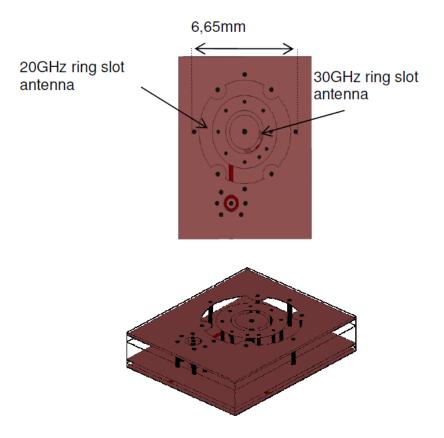

Due to the constraints given by the ratio between the TX and RX wavelengths, dual band elements cannot be placed at distances which are close to half a wavelength at both frequencies of operation. The large separation between the operating wavelengths can be balanced interleaving dual band elements with single band elements operating at the higher frequency. The principal planes of the RX and TX arrays are rotated by 45°. With this configuration, if the RX elements are spaced 0.5 wavelength at 20 GHz, the TX elements result to stay at 0.53 wavelength at 30 GHz. As it can be seen, other than dual band radiators, single band elements operating at 20 GHz and at 30 GHz have been employed.

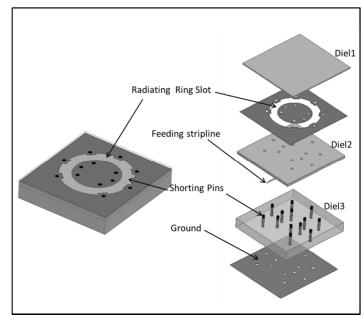

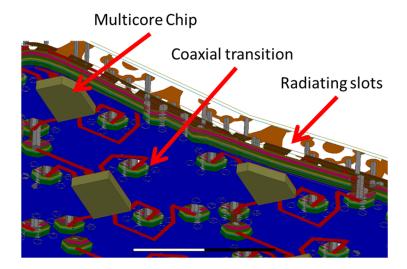

As it shown in figure 4-1 three type of radiating element are used in the antenna array, dual band radiator, RX single band radiator and TX single band radiator. Antenna elements have a multilayered structure and are fed by stripline. The radiating element is composed by an annular slot surrounded by vias for propose of increasing the isolation between adjacent elements. The inner border of the elements slot is also surrounded with vias forming a coaxial structure. In figure 4-2 and figure 4-3 are shown the 20GHz and 30GHz element geometry.

Figure 4-2: 20GHz radiating element geometry.

Figure 4-3: 30GHz radiating element geometry.

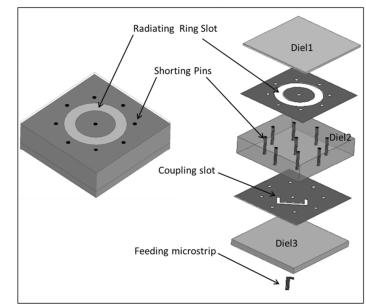

The two elements can be combined to form a dual band radiator as shown in figure 4-4.

Figure 4-4: Dual band radiator layout (FLEXWIN Deliverable D2.1).

Each radiating element is fed with different techniques. The RX ring is electromagnetically coupled to a stripline while the TX ring is fed by means of a slot. Feeding structure is shown in figure 4-5.

Figure 4-5: Feeding of dual band radiating element (FLEXWIN Deliverable D2.1).

Figure 4-6 shows  $S_{11}$  obtained from simulation for the dual band radiating element. Isolation between TX and RX port is shown in figure 4-7 for both frequencies band.

Figure 4-6: Simulated S<sub>11</sub> at (a) RX port (b) TX port.

Figure 4-7: Simulated isolation in (a) RX band (b) TX band.

Simulated gain is 3.8 dB at 20 GHz and 4.5 dB at 30 GHz. In order to investigate the element gain on the operational bands, simulations have been carried out for a 2×2 array. Figure 4-8 shows the element gain vs. frequency for the 2×2 configuration. Results are satisfactory over the entire bandwidth.

Figure 4-8: Simulated gain for 2×2 sub-array for (a) TX band (b) RX band.

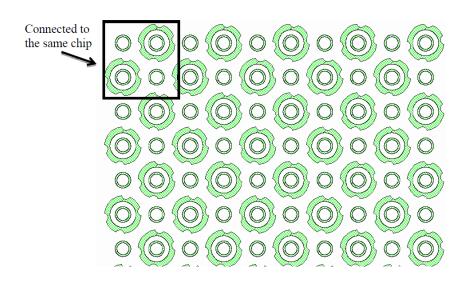

Figure4-9 illustrates the architecture of antenna array and shows the radiating elements connected to the same chip are highlighted.

Figure 4-9: Layout of antenna array.

The specifications for the antenna array derive from the final full-scale antenna specification and are listed in Table 4-1.

Table 4-1: Specifications for antenna array.

| Frequencies:                    | Receive: 19.7 – 21.0 GHz            |  |

|---------------------------------|-------------------------------------|--|

|                                 | Transmit: 29.5 – 30.8 GHz           |  |

| Polarization:                   | Single linear                       |  |

| Beam steering:                  | Electrical in azimuth and elevation |  |

| Coverage:                       | ±60°                                |  |

| Height:                         | less than 5 cm                      |  |

| Total output power per element: | 1.4 mW                              |  |

| Number of elements:                    | approx. 100  |  |

|----------------------------------------|--------------|--|

| Receiver noise figure per element:     | 5 dB         |  |

| Transmit/receive functionality switch: | BiCMOS based |  |

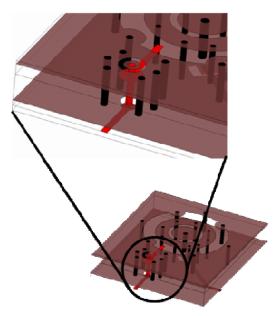

Chips are placed in the lower part of the array. Coaxial transition have been used to connect the chips to the feeding striplines as shown in figure 4-10 and figure 4-11.

Figure 4-10: Antenna array feeding network with multicore SiGe chip.

Figure 4-11: Chip position and feeding lines to radiating elements.

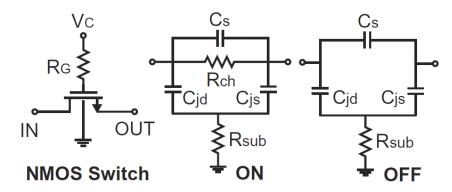

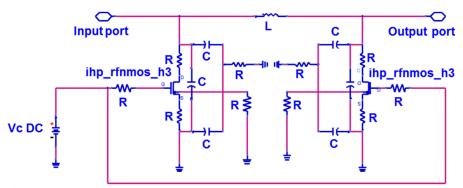

Each multicore SiGe chip feed six antennas as shown in figure 4-7. Two RX (20 GHz) antennas and four TX (30 GHz) antennas connected to one chip. This mean for approximately 100 elements we need at least 17 chips to feed them.

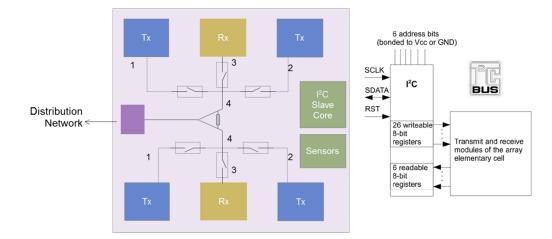

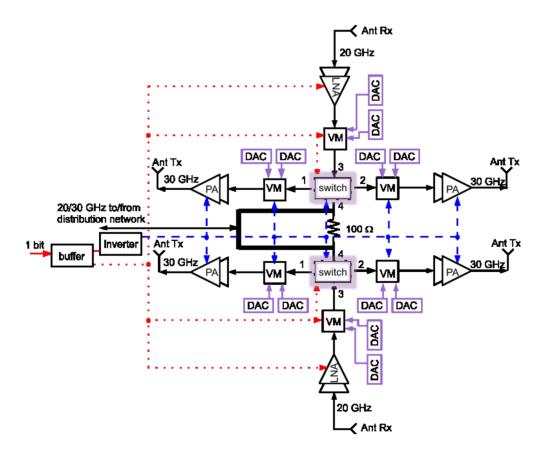

#### 4.2 Chip configuration and architecture

As discussed in pervious section each chip must provide 7 RF terminals. Two terminals for RX antennas that must operate at 20 GHz, four terminals for TX antennas that operate at 30 GHz and one terminal that musty operate at both frequencies that connect to distribution network. There are also I2C buses and data lines for controlling the voltages and functionality of the chip. To satisfy the specification required for antenna array, multicore SiGe chip is designed by employing of several RF blocks such as low noise amplifiers, power amplifiers, vector modulators, switches and power divider-combiner. Reconfigurability or in another word electronic beam steering is the characteristic gained by selectable and controllable components of the chip such as switches and vector modulators.

The architecture of the chip is based on different functionality that expected from chip. The main issues in TX mode are to minimize noise figure and have good matching in all terminals. On the other hand providing enough output power in RX mode is the main goal. For these reasons in RX mode LNA is used to decrease the noise figure and in TX mode PA is used to reach the maximum gain in output. Switching network (SW) is used to separate TX and RX mode and provide enough isolation between them. Vector modulators (VM) in both modes are employed to obtain variable output that cause reconfigurability. Wide band power divider-combiner (PW) provide the possibility to

divide and combine the power that comes or goes to distribution networks in to the different branches. Figure 4-12 shows the block diagram of chip and control units as well.

Figure 4-12: Block diagram of the chip and I2C control unit.

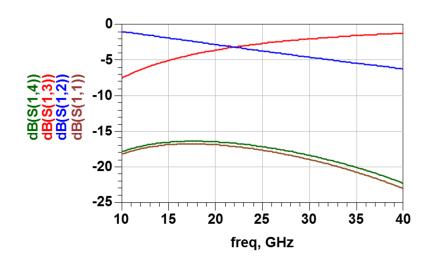

Figure 4-13 shows a detailed blocks and the connection between them, as shown in the main line come from the distribution network and then goes to wideband Wilkinson power divider, then each branch is connected to the switching network. Switching network has 1 input and 3 out puts, one of them is connected to RX radiating element, while remaining two are connected to TX radiators.

Figure 4-13: Block diagram of multicore SiGe chip with RF blocks.

Selecting transmit or receive mode is done by switching network while DACs control the voltage of vector modulators.

#### 4.3 Link budget and chip components specs

In this section is discussed the link budget and the related antenna performance analysis for Ka-Band SatCom applications based on the knowledge of existing satellite communication systems. Transmit and receive concern divided in two different parts that must be considered.

In the case of transmit antenna following parameters were considered:

• G/T (Antenna gain to noise temperature) of the receive antenna on the satellite

- required S/N(Signal to noise ratio)on the satellite

- available output power of the intelligent pixel chip