# Investigation of dimensionality effects on capacitorless memory and trench power MOSFET

Silvio Pierro

November 2011

The "Collegio dei docenti" of the Ph.D. in Fisica e Tecnologie Quantistiche

> Coordinator: Giovanni Falcone

Tutor: Antonello Sindona Calogero Pace

#### acknowledgement

My first thank is to my tutor Prof. Calogero Pace. He bring me advanced knowledge about power electronic devices, has always given me any equipment and instrument which I need to, and gave me the possibility to face this Ph.D.

Another thank to Prof. Felice Crupi and Ing. Gino Giusi that helped me by gaving some research ideas and suggestions.

Another thank goes to STMicroelectronics, in particular to Ing. Giuseppe Consentino and Vincenzo Cilia that followed me in my internship experience to learn power electronic devices.

Last but not the least, I wish to thank my parents, my family and my dolly Manuela. They were a constant support during these three years of PhD.

to my family

iv

### Contents

| Preface     ix |                         |                                                                                                                                                                   |    |  |  |  |  |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

| $\mathbf{Li}$  | st of                   | Pubblications                                                                                                                                                     | x  |  |  |  |  |

| In             | trod                    | action                                                                                                                                                            | xi |  |  |  |  |

| 1              | TC                      | AD Simulation setup                                                                                                                                               | 1  |  |  |  |  |

|                | 1.1                     | Drift-diffusion model                                                                                                                                             | 2  |  |  |  |  |

|                |                         | 1.1.1 Poisson equation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                    | 2  |  |  |  |  |

|                |                         | 1.1.2 Continuity equations $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                              | 2  |  |  |  |  |

|                |                         | 1.1.3 Density Of State                                                                                                                                            | 4  |  |  |  |  |

|                |                         | 1.1.4 Mobility model $\ldots$                                                                                                                                     | 6  |  |  |  |  |

|                |                         | 1.1.5 Impact ionization $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                   | 9  |  |  |  |  |

|                |                         | 1.1.6 Band To Band Tunneling                                                                                                                                      | 9  |  |  |  |  |

|                | 1.2                     | Self-consistent Poisson-Shroedinger model                                                                                                                         | 10 |  |  |  |  |

|                |                         | 1.2.1 Shroedinger equation $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                                                                       | 10 |  |  |  |  |

|                |                         | 1.2.2 Statistic                                                                                                                                                   | 11 |  |  |  |  |

|                | 1.3                     | Numerical technique                                                                                                                                               | 12 |  |  |  |  |

|                |                         | 1.3.1 Mesh definition $\ldots \ldots \ldots$                                                       | 12 |  |  |  |  |

|                |                         | 1.3.2 Discretization method                                                                                                                                       | 13 |  |  |  |  |

| Ι              | Po                      | ver MOSFET device analysis 1                                                                                                                                      | 7  |  |  |  |  |

| <b>2</b>       | Pov                     | ver mosfet devices 1                                                                                                                                              | 19 |  |  |  |  |

|                | 2.1                     | Power diode                                                                                                                                                       | 20 |  |  |  |  |

|                |                         | 2.1.1 Basic p-n physics                                                                                                                                           | 21 |  |  |  |  |

|                |                         | 2.1.2 junction breakdown                                                                                                                                          | 24 |  |  |  |  |

|                | 2.2                     | Power MOSFET                                                                                                                                                      | 29 |  |  |  |  |

|                |                         | 2.2.1 $I-V$ characteristic $\ldots \ldots \ldots$ | 30 |  |  |  |  |

|                | 2.3 Trench Power MOSFET |                                                                                                                                                                   |    |  |  |  |  |

|                |                         | 2.3.1 Trench power MOSFET breakdown                                                                                                                               | 32 |  |  |  |  |

| 3        | Tre  | nch power MOSFET simulations                                                           | 35 |

|----------|------|----------------------------------------------------------------------------------------|----|

|          | 3.1  | Simulation setup                                                                       | 36 |

|          |      | 3.1.1 pn reference structure setup                                                     | 38 |

|          |      | 3.1.2 measurement setup $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 39 |

|          | 3.2  | pn structure simulations                                                               | 42 |

|          |      | 3.2.1 Parameter analysis                                                               | 43 |

|          | 3.3  | Trench structure simulations                                                           | 45 |

|          |      | 3.3.1 Pitch exclusion $\ldots$                                                         | 46 |

|          |      | 3.3.2 Drift region analysis                                                            | 48 |

|          |      | 3.3.3 Trench's shape analysis                                                          | 49 |

| 4        | Nov  | el Breakdown model                                                                     | 55 |

|          | 4.1  | Pn breakdown model                                                                     | 56 |

|          |      | 4.1.1 Model analysis                                                                   | 60 |

|          | 4.2  | Trench breakdown model                                                                 | 62 |

|          |      | 4.2.1 Electrical consideration                                                         | 64 |

|          |      | 4.2.2 novel breakdown model                                                            | 65 |

|          |      | 4.2.3 model synthesis $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 68 |

| II       | me   | emory device simulations                                                               | 71 |

| <b>5</b> | capa | acitorless device description                                                          | 73 |

|          | 5.1  | Memory device concepts                                                                 | 74 |

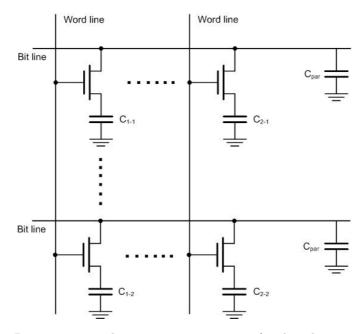

|          |      | 5.1.1 Dynamic RAM                                                                      | 75 |

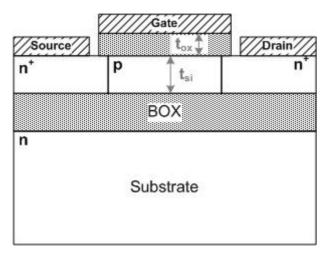

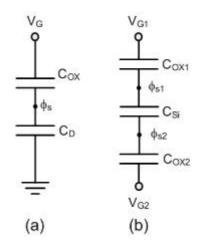

|          | 5.2  | SOI MOSFET devices                                                                     | 77 |

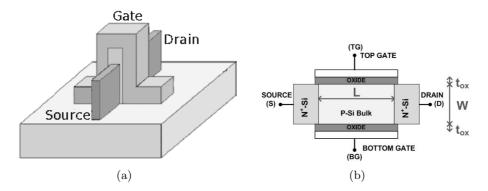

|          | 5.3  | FinFET devices                                                                         | 79 |

|          | 5.4  | Bipolar mode description                                                               | 80 |

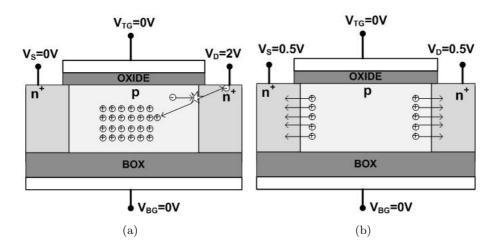

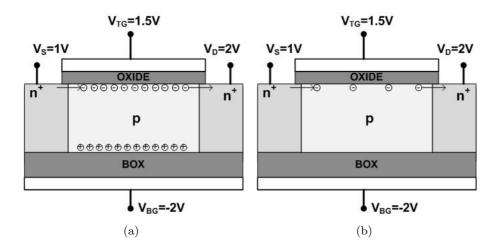

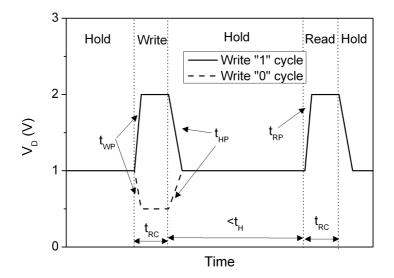

|          |      | 5.4.1 Write operation $\ldots$                                                         | 82 |

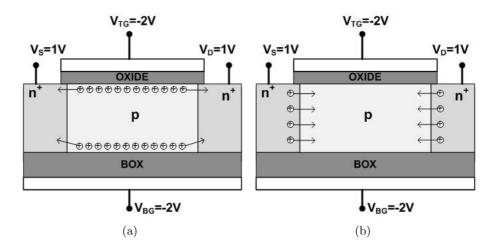

|          |      | 5.4.2 Hold operation $\ldots$                                                          | 83 |

|          |      | 5.4.3 Read operation $\ldots$                                                          | 84 |

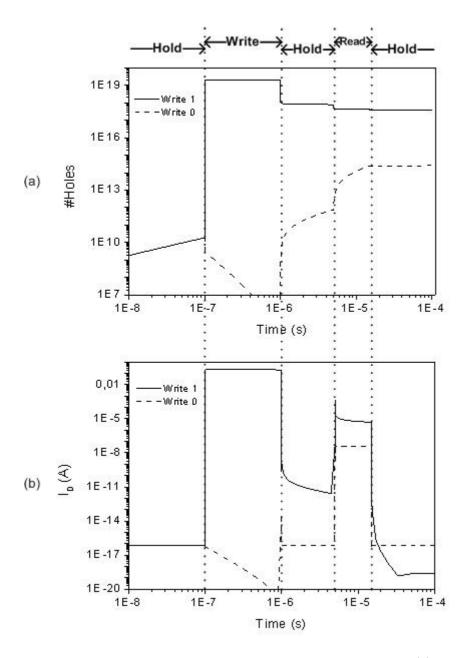

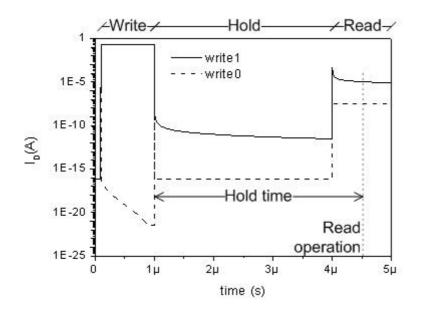

|          | 5.5  | transient analysis                                                                     | 86 |

| 6        | Cap  | acitorless simulations                                                                 | 89 |

|          | 6.1  | simulation setup                                                                       | 90 |

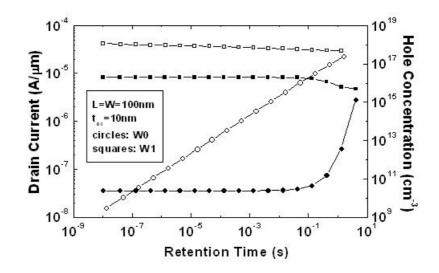

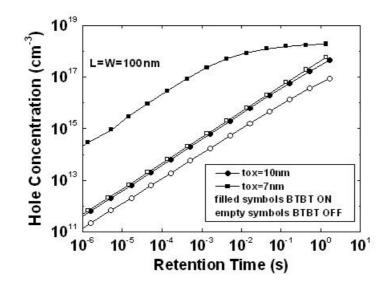

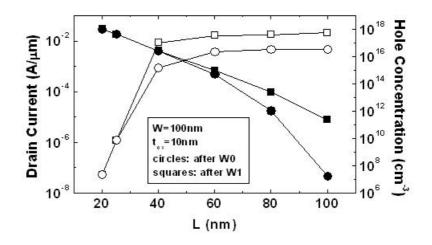

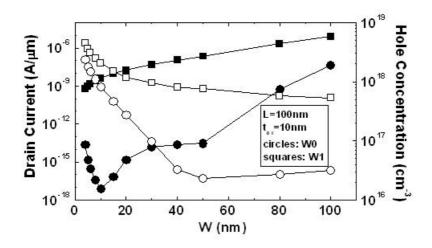

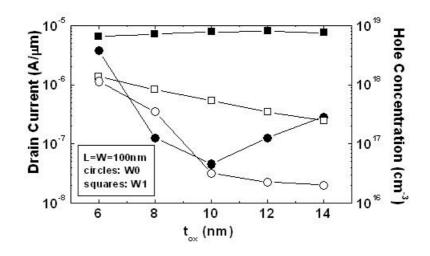

|          |      |                                                                                        | 91 |

|          |      |                                                                                        | 95 |

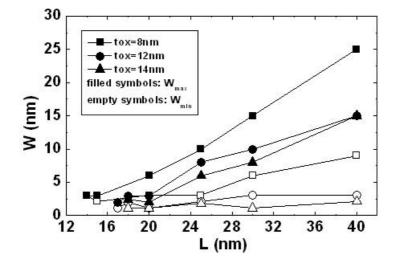

|          | 6.2  |                                                                                        | 96 |

|          |      | 8 8                                                                                    | 97 |

|          |      | 8                                                                                      | 98 |

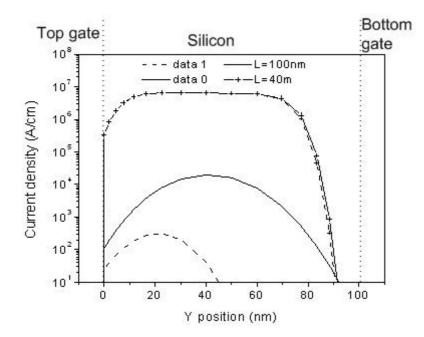

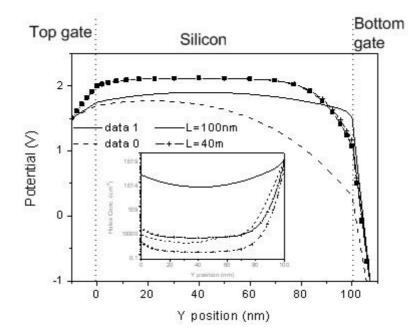

|          |      | 6.2.3 scaling considerations                                                           | 00 |

|          |      |                                                                                        |    |

| CONTENTS          | vii |

|-------------------|-----|

| B List of Symbols | 107 |

| Conclusions       | 109 |

| Bibliography      | 116 |

### Preface

Investigation of geometrical characteristics of novel device structures is a crucial activity in modern electronics. Due to its higher cost and to higher time to develop, it's not possible to make real device structures for large scale measurements. In order to obtain good results in lower time and with reasonable resources it's better to analyze the device characteristic's variations with a simulation setup and to extract model and trends with this simulation setup, and to use measurements for models check only.

With the simulation approach, since we are able to analyze the internal device electrical characteristics, it's easier to analyze device's electrical phenomena and so extract the model.

In my research activities this methodology has been robustly applied to electronics devices from memory low power device to high power MOSFET devices.

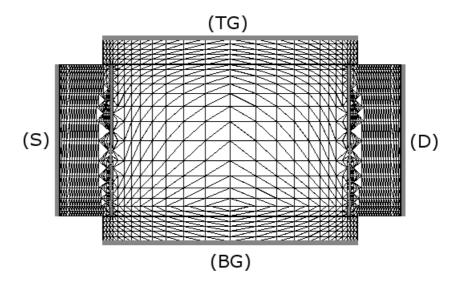

- My PhD study started with simulation study of novel semiconductor devices for memory application, that involves the use of self consistent Poisson-Schrodinger model in order to simulate very thin devices.

- The second year of study focused on power applications, with particular attention to breakdown voltage analysis on MOSFET devices and its literature model.

- The last PhD year started with a collaboration with ST Microelectronics and a small stage period of two months, which focused attention to a new power MOSFET architecture called Trench power MOSFET on which has been made a breakdown characterization as a function of device's characteristics.

#### List of Pubblications

- MAGNONE P., SUBRAMANIAN V., PACE C., CRUPI F., AND PIERRO S. "Gate voltage and geometry dependence of the series resistance and of the carrier mobility inn FinFET devices", Microelectronic engineering, Vol.85, issue 8, Elsevier, 2008.

- [2] GIUSI G., ALAM M., CRUPI F., AND PIERRO S. "Bipolar Mode Operation and scalaility of Double Gate Capacitorless 1T DRAM Cells", IEEE Transactions on electron devices, Vol.57, issue 8, pp.1743-1750, 2010.

#### Conference paper

[3] PACE C., PIACENTE A., VESCIO F., PIERRO S., AND SIGH B.G. "An Ultra-Low-Noise Source-Measuring Unit for Semiconductor Device Noise Characterization", I2MTC 2010, Austin TX, USA, 3-6 May 2010.

#### Submitted paper

[4] PIERRO S., CILIA V., COSENTINO G., AND PACE C. "Novel Avalanche Breakdown Calculation Model for Trench Power MOSFETs", Submitted on Microelectronics Engineering 2011.

### Introduction

The characterization of electronic devices is a crucial step for understanding device properties and their use in applied electronics; in particular it helps to know how to change the structure to obtain better performance, or how to reduce production costs and produce devices more competitive in the market.

The main device characterization technique involves measuring the electrical characteristics of the device according to the different geometrical parameters to extract the dependencies of electrical parameters over geometric variations of device. The production of standard MOS devices allow us to realize devices with a large number of different geometric characteristics on a single wafer with the same process step, for example, you can create arrays with wide range of devices with different gate length, called Larray or variable width, called Warray.

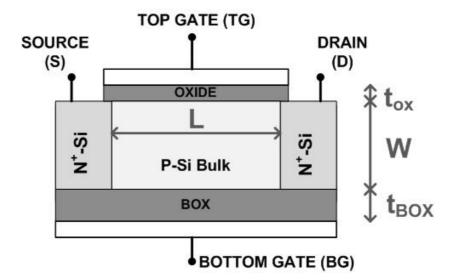

For standard MOS devices it's possible to perform this analysis, but for innovative devices is not always possible to change geometrical parameters in order to realize device arrays because theese parameters are set by the technological processes, or set by wafer characteristics. An example of a limitation due to the characteristics of the wafer is shown in Figure 1a, where we present a SOI MOSFET, which is a MOSFET made on a semiconductor layer bottom isolated by a field oxide, the semiconductor depth is determined during the SOI wafer production, and therefore cannot be changed.

Another example is trench power MOSFET device, the process flow cannot allow to change the depth of drift region, realized by a deposition process, and therefore must be constant throughout the wafer, it is not possible to realize trench lengths arbitrary, since it would require separate etching processes for each device.

For these kind of devices, the realization of device arrays to be studied is virtually impossible, so the previous method of device characterization is inapplicable.

Fortunately, the modern computing power and deep knowledge of semiconductor physics allow you to make any kind of simulation of electronic devices even in stationary state than in time domain; The software that allow us to perform these simulations are so called Technology Computer Aided device simulators (TCAD), and allow us to simulate any device with doping and size arbitrary chosen and fit for any value of voltage applied to his contacts.

This technique allows us to draw many different technological devices with lengths and to obtain realistic simulations of these devices in a similar way to the measurement setup made on real devices, with the advantage of obtain also the device's electrical characteristics, such as electrostatic potential and carrier concentration, this feature is very useful to explain the macroscopic phenomena of the device.

The use of a TCAD simulator involves the transition from a real device to simulation of the same device, then we need to make a series of checks to ensure the accuracy of the results, in particular, check that the device has been made correctly, that the number of device's simulation points is a good trade-off between good results and simulation times, and that includes all physical phenomena that occur in the device.

This characterization method was applied to evaluate the electrical characteristics of a Trench power MOSFET device, in particular to extract a model taking into account the device breakdown to obtain the breakdown voltage. In addition it was used to characterize a double-gate FinFET memory device in order to check the validity of capacitorless memory and assess what might be future developments in terms of technology scaling.

This thesis make simulations of two different devices, so it was divided into two parts. The first part deals with the simulation of Trench Power MOSFET devices in stationary conditions, and the second part make timedomain simulations of capacitorless memory devices.

- Chapter 1 talk about the main physics phenomena that describes devices under study; In particular the drift-diffusion model and self consistent Schrodinger-Poisson models with its statistical models, mobility and impact generation models. Finally the numerical method used to solve differential equation is described.

- Chapter 2 starts discussion of trench power MOSFET devices by describing the main power MOSFET and power diode features with a particular attention on breakdown characteristics and a comparison with the equivalent low power device.

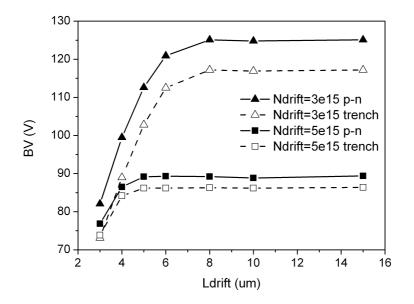

- Chapter 3 discuss massive simulation on trench power MOSFET and diode equivalent structure to describe the variation on breakdown voltage due to geometrical and doping variation and identify main trends on breakdown voltage versus main geometrical characteristics.

- Chapter 4 presents the physical model used to calculate the breakdown voltage in a power diode and compares the results with the simulations described in chapter 3 for the reference junction structure. Finally it uses the same method to derive the appropriate correction of equipment breakdown voltage in the trench structure using appropriate correction parameters.

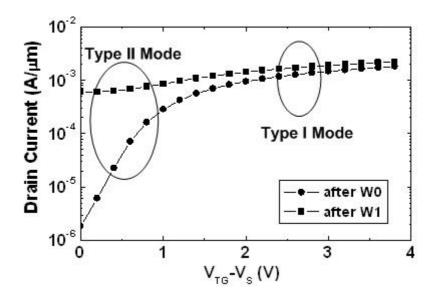

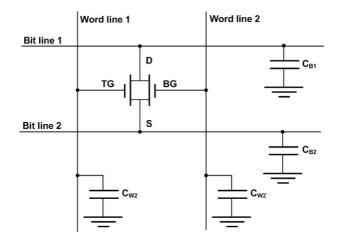

- Chapter 5 starts the study of storage devices, with an introduction to memory device, a particular attention to SOI MOSFET devices and its application to use as a volatile Dynamic RAM memory with the explanation of its bipolar mode operation, so called Type II.

- Chapter 6 briefly describes the simulation setup used on the memory storage structure from which begin the discussion on the technology scaling, with particular attention to the length scaling, the resulting problems and solutions to apply.

#### INTRODUCTION

## Chapter 1 TCAD Simulation setup

Physical phenomena in semiconductor devices are very complicated and, depending on applications, are described by partial differential equations of different level of complexity [1]. Coefficients and boundary conditions of equations (such as mobility, generation–recombination rate, material– dependent parameters, interface and contact boundary conditions) can be very complicated and can depend on microscopic physics, the structure of the device, and the applied bias; This knowledge of semiconductor physics and numeracy solution method allows us the use of a device simulation setup to obtain good estimates on the behavior of described devices.

This chapter describes the main characteristics of solid-state physics, with particular attention to the drift-diffusion model is under quasi stationary in the time domain, in addition to the model of self-consistent Poissonshroedinger. Finally, were considered out important techniques used to obtain numerical solutions of the previous physical models with their main characteristics.

#### 1.1 Drift-diffusion model

Derivations based upon the Boltzmann transport theory have shown that the current densities in the continuity equations may be approximated by a drift-diffusion model [2].

This kind of model is a good approximation to device physics for a very large devices, especially for mosfet with low power dissipation condition and with relatively large area (> 100nm). The model includes the Poisson equation and two transport equations for electrons and holes respectively. The model require also a mobility model, a generation model, and a boundary condition setup [3].

#### 1.1.1 Poisson equation

Poissons Equation relates the electrostatic potential to the space charge density:

$$\nabla(\epsilon \nabla \Psi) = \rho \tag{1.1}$$

where  $\Psi$  is the electrostatic potential,  $\epsilon$  is the local permittivity, and  $\rho$  is the local space charge density. The reference potential can be defined in various ways. The most used way to define it is the intrinsic Fermi potential  $\Psi_i$  which will be defined later. The local space charge density is the sum of contributions from all mobile and fixed charges, including electrons, holes, and ionized impurities. By replacing the local space charge density the previous equation becomes

$$\nabla(\epsilon \nabla \Psi) = q(p - n + N_D - N_A + G - R) - \rho_{trap}$$

(1.2)

where q is the elementary electronic charge, n and p are the electron and hole densities,  $N_D$  is the concentration of ionized donors,  $N_A$  is the concentration of ionized acceptors, G and R are respectively generation and recombination rates, and  $\rho_{trap}$  is the charge density contributed by traps and fixed charges.

The electric field is obtained from the gradient of the potential

$$\vec{E} = -\nabla\Psi \tag{1.3}$$

#### 1.1.2 Continuity equations

The continuity equations for electrons and holes are defined by equations:

$$\frac{\partial n}{\partial t} = \frac{1}{q} div \vec{J_n} + G_n - R_n \tag{1.4}$$

$$\frac{\partial p}{\partial t} = \frac{1}{q} div \vec{J_p} + G_p - R_p \tag{1.5}$$

where n and p are the electron and hole concentration,  $\vec{J_n}$  and  $\vec{J_p}$  are the electron and hole current densities,  $G_n$  and  $G_p$  are the generation rates for electrons and holes, and  $R_n$  and  $R_p$  are the recombination rates for electrons and holes. Normally, a drift-diffusion simulation includes both Equations (1.4) and (1.5). In some circumstances, like a unilateral diode, it is sufficient to solve only one carrier continuity equation.

In drift-diffusion model, the current densities are expressed in terms of the quasi-Fermi levels  $\phi_n$  and  $\phi_p$  as:

$$\vec{J_n} = -q\mu_n n \div \phi_n \tag{1.6}$$

$$\vec{J_p} = -q\mu_p p \div \phi_p \tag{1.7}$$

where  $\mu_n$  and  $mu_p$  are the electron and hole mobility. The quasi-Fermi levels are then linked to the carrier concentrations and the potential through the two Boltzmann approximations [4]:

$$n = n_i exp\left[\frac{q\left(\psi - \phi_n\right)}{kT_L}\right] \tag{1.8}$$

$$p = n_i exp\left[\frac{-q\left(\psi - \phi_p\right)}{kT_L}\right] \tag{1.9}$$

where  $n_i$  is the effective intrinsic concentration,  $T_L$  is the lattice temperature, and k is the Boltzmann constant. The first two quantities has been assumed to be constant for all simulations; and its value are respectively  $T_L = 300K$  and  $n_i = 9.38e^{19}cm^{-3}$  for Silicon.

These two equations may then be re-written to define the quasi-Fermi potentials:

$$\phi_n = \Psi - \frac{kT_L}{q} ln \frac{n}{n_i} \tag{1.10}$$

$$\phi_p = \Psi + \frac{kT_L}{q} ln \frac{p}{n_i} \tag{1.11}$$

By substituting these equations into the current density expressions (equations (1.4) and (1.5)), the following adapted current relationships are obtained:

$$\vec{J_n} = qD_n \nabla n - qn\mu_n \nabla \Psi - \mu_n n(kT_L \nabla (lnn_i))$$

(1.12)

$$\vec{J_p} = qD_p\nabla p - qp\mu_p\nabla\Psi + \mu_p p(kT_L\nabla(lnn_i))$$

(1.13)

The final term accounts for the gradient in the effective intrinsic carrier concentration, which takes account of bandgap narrowing effects. Effective electric fields change from equation (1.3) to

$$\vec{E_n} = -\nabla \left(\Psi + \frac{kT_L}{q}lnn_i\right) \tag{1.14}$$

$$\vec{E_p} = -\nabla \left( \Psi - \frac{kT_L}{q} lnn_i \right) \tag{1.15}$$

which then allows the more conventional formulation of drift-diffusion equations to be written as

$$\vec{J_n} = qn\mu_n \vec{E_n} + qD_n \nabla n \tag{1.16}$$

$$\vec{J_n} = qp\mu_p \vec{E_p} - qD_p \nabla p \tag{1.17}$$

It should be noted that this derivation of the drift-diffusion model has tacitly assumed that the Einstein relationship holds. In the case of Boltzmann statistics [5] this corresponds to:

$$D_n = \frac{kT_L}{q}\mu_n \tag{1.18}$$

$$D_p = \frac{kT_L}{q}\mu_p \tag{1.19}$$

If Fermi-Dirac statistics are assumed for electrons, Diffusivity for electron becomes

$$D_n = \frac{\left(\frac{kT_L}{q}\mu_n\right)F_{1/2}\left\{\frac{1}{kT_L}\left[\epsilon_{Fn} - \epsilon_C\right]\right\}}{F_{-1/2}\left\{\frac{1}{kT_L}\left[\epsilon_{Fn} - \epsilon_C\right]\right\}}$$

(1.20)

where  $F_{\alpha}$  is the Fermi-Dirac integral of order  $\alpha$  and  $\epsilon_{Fn} = -q\phi_n$ . An analogous expression is used for holes with Fermi-Dirac statistics; The Fermi-Dirac statistic is used instead of Boltzmann statistic when high doping concentrations are used in semiconductor  $(10^{19}cm^{-3})$ .

The Drift-diffusion model is so realized by Poisson equation (eq. (1.3)) and the two equations for electron and hole concentrations (eq. (1.12) and (1.13)).

#### 1.1.3 Density Of State

In order to evaluate Density of State for electrons and holes in semiconductor devices, a distribution probability as energy function must be used; Identical discussion must been made for electrons and holes, for simplicity we report discussion for electrons only. Electrons in thermal equilibrium at temperature  $T_L$  with a semiconductor lattice obey Fermi-Dirac statistics. That is the probability  $f(\epsilon)$  that an available electron state with energy  $\epsilon$  is occupied by an electron is:

$$f(\epsilon) = \frac{1}{1 + exp\left[\frac{\epsilon - E_F}{kT_L}\right]}$$

(1.21)

where  $E_F$  is a spatially independent reference energy known as the Fermi level and k is Boltzmanns constant. In the limit that,  $\epsilon - E_F \gg kT_L$ , Equation (1.21) can be approximated as:

$$f(\epsilon) = exp\left[\frac{E_F - \epsilon}{kT_L}\right]$$

(1.22)

Statistics based on the use of Equation (1.22) are referred to as Boltzmann statistics. The use of Boltzmann statistics instead of Fermi-Dirac statistics makes subsequent calculations much simpler. The use of Boltzmann statistics is normally justified in semiconductor device theory, but Fermi-Dirac statistics are necessary to account for certain properties of very highly doped materials.

Integrating the Fermi-Dirac statistics over a parabolic density of states in the conduction and valence bands, whose energy minimum is located at energies  $E_C$  and  $E_V$  respectively, yields the following expressions for the electron and hole concentrations:

$$n = N_C f_{1/2} \left( \frac{E_F - E_C}{kT_L} \right) \tag{1.23}$$

$$p = N_V f_{1/2} \left(\frac{E_V - E_F}{kT_L}\right) \tag{1.24}$$

where  $F(1/2)(\eta)$  is referred to as the Fermi-Dirac integral of order 1/2. If Equation (1.22) is a good approximation, then Equations (1.23) and (1.24) can be simplified to

$$n = N_C exp\left(\frac{E_F - E_C}{kT_L}\right) \tag{1.25}$$

$$p = N_V exp\left(\frac{E_V - E_F}{kT_L}\right) \tag{1.26}$$

which are referred to as the Boltzmann approximation.  $N_C$  and  $N_V$  are referred to as the effective density of states for electrons and holes and are given by:

$$N_C = 2\left(\frac{2\pi m_n k T_L}{h^2}^{3/2}\right)$$

(1.27)

$$N_V = 2\left(\frac{2\pi m_p k T_L^{3/2}}{h^2}\right)$$

(1.28)

where h is the Planck constant, and  $m_n$  and  $m_p$  are effective mass for electron and holes respectively.

#### 1.1.4 Mobility model

Free electrons present in conduction band are substantially free particles that tend to move in a Brownian motion with a medium speed  $v_{th}$ . The kinetic energy of the electrons can be expressed by the relation:

$$\frac{1}{2}m_n v_{th}^2 = \frac{3}{2}kT_L \tag{1.29}$$

At room temperature, the mean speed for Silicon is approximately  $10^7 cm/s$  [6].

Since the effects of various scattering phenomena, like lattice vibrations (phonons), impurity ions, other carriers, surfaces, and other material imperfections, the macroscopic mobility will be introduced by the transport equations. This mobility is therefore function of the local electric field, lattice temperature, doping concentration, and so on [7].

Mobility modeling is normally divided into:

- (i) low field behavior;

- (ii) high field behavior;

- (iii) bulk semiconductor regions;

- (iv) inversion layers.

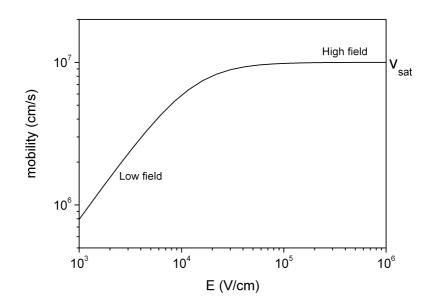

The low electric field behavior has carriers almost in equilibrium with the lattice and the mobility has a characteristic low-field value that is commonly denoted by the symbol  $\mu_{n0}, \mu_{p0}$ . The value of this mobility is dependent upon phonon and impurity scattering. Both of which act to decrease the low field mobility.

The high electric field behavior shows that the carrier mobility declines with electric field because the carriers that gain energy can take part in a wider range of scattering processes. The mean drift velocity no longer increases linearly with increasing electric field, but rises more slowly. Eventually, the velocity doesnt increase any more with increasing field but saturates at a constant velocity. This constant velocity is commonly denoted by the symbol  $v_{sat}$ . Impurity scattering is relatively insignificant for energetic carriers, and so  $v_{sat}$  is primarily a function of the lattice temperature.

Figure 1.1: Electron mobility as function of electric field at room temperature.

Modeling mobility in bulk material involves: (i) characterizing  $\mu_{n0}$  and  $\mu_{p0}$  as a function of doping and lattice temperature, (ii) characterizing  $v_{sat}$  as a function of lattice temperature, and (iii) describing the transition between the low field mobility and saturated velocity regions.

Modeling carrier mobility in inversion layers introduces additional complications. Carriers in inversion layers are subject to surface scattering, extreme carrier-carrier scattering, and quantum mechanical size quantization effects. These effects must be accounted for in order to perform accurate simulation of MOS devices. The transverse electric field is often used as a parameter that indicates the strength of inversion layer phenomena.

To use all the mobility model, the different mobility contributions are combined according to the following scheme: different mobility contributions are combined following Mathiessens rule [8]:

$$\frac{1}{\mu} = \frac{1}{\mu_1} + \frac{1}{\mu_2} + \frac{1}{\mu_3} \dots + \frac{1}{\mu_N}$$

(1.30)

#### Low field mobility model

The low field mobility parameter taking into account the effects of lattice scattering, impurity scattering (with screening from charged carriers), carrier-carrier scattering, and impurity clustering effects at high concentration. The total mobility described by Matthiessens rule add two mobility components [9]

$$\frac{1}{\mu_n} = \frac{1}{\mu_{nL}} + \frac{1}{\mu_{nDAP}}$$

(1.31)

$\mu_n$  is the total low field electron and hole mobility,  $\mu_{nL}$  is the electron mobility due to lattice scattering,  $\mu_{nDAP}$  the electron and hole mobility due to donor (D), acceptor (A), screening (P) and carrier-carrier scattering. A similar mobility equation could be evaluated for electrons.

The lattice scattering component,  $\mu_{nL}$  is given as:

$$\mu_{nL} = v_{nmax} \left(\frac{300}{TL}\right)^{\gamma} \tag{1.32}$$

where  $v_{nmax}$  is the maximum electron velocity that for silicon can be evaluated as  $1417(cm^2/V \cdot s)$ , and  $\gamma$  is a correction factor of 2.2; the equivalent value for holes are  $v_{hmax} = 470.5(cm^2/V \cdot s)$  and  $\gamma = 2.24$ .

The impurity-carrier scattering component of the total electron mobility is given by

$$\mu_{nDAP} = \mu_{N,n} \frac{N_{nsc}}{N_{nsc,eff}} + \mu_{nc} \left(\frac{n+p}{N_{nsc,eff}}\right)$$

(1.33)

where  $\mu_{N,n}$  is the impurity scatter component,  $N_{nsc} = N_D + N_A + p$ ,  $N_{nsc,eff} = N_D + \alpha N_A + \beta p$  and  $\mu_{nc}$  is the carrier-carrier scattering component.

#### Inversion layer mobility model

The inversion layer mobility model must take into account for mobility reduction due to MOS inversion layer, the transverse field, doping dependent and temperature dependent parts of the mobility are given by three components that are combined using Matthiessens rule [10]. These components are  $\mu_{AC}$ , and  $\mu_{sr}$ . The first component, is the surface mobility limited by scattering with acoustic phonons:

$$\mu_{nAC} = \frac{B_n}{E_\perp^{\alpha AC}} + \frac{N^{\alpha AC}}{T_L E_\perp^{\beta sr}} \tag{1.34}$$

the second component is the surface roughness factor, and is given by:

$$\mu_{nsr} = \frac{N^{\alpha sr}}{T_L E_\perp^{\beta sr}} \tag{1.35}$$

where  $T_L$  is the lattice temperature,  $E_{\perp}$  is the perpendicular electric field, and N is the total doping concentration.

| $A_n$     | $7.03e^5 \ cm^{-1}$ |

|-----------|---------------------|

| $A_p$     | $6.73e^5 \ cm^{-1}$ |

| $B_n$     | $1.23e^6 V/cm$      |

| $B_p$     | $1.69e^6 V/cm$      |

| $\beta_n$ | 1                   |

| $\beta_p$ | 1                   |

Table 1.1: Numerical parameters of impact ionization formula

#### 1.1.5 Impact ionization

Impact ionization phenomena modeling is essential in the simulation object of this thesis, because this phenomena is responsible of avalanche breakdown in power semiconductors, and is is responsible of carrier increase in memory devices; Therefore we must choose the model to use with extreme accuracy. The general impact ionization process is described by [11]

$$G = \alpha_n \left| \vec{J_n} \right| + \alpha_p \left| \vec{J_p} \right| \tag{1.36}$$

where, G is the local generation rate of electron-hole pairs,  $\alpha_n$  and  $\alpha_p$  are the ionization coefficient for electrons and holes, and  $J_n$  and  $J_p$  are their current densities. The ionization coefficient represents the number of electron-hole pairs generated by a carrier per unit distance travelled.

The generation rate can be calculated by using the following formula

$$\alpha_n = A_n exp\left[-\left(\frac{B_n}{E}\right)^{\beta n}\right] \tag{1.37}$$

$$\alpha_p = A_p exp\left[-\left(\frac{B_p}{E}\right)^{\beta p}\right] \tag{1.38}$$

where, E is the electric field in the direction of current flow at their structure's position and  $A_n$ ,  $A_p$ ,  $B_n$ ,  $B_p$ ,  $\beta_n$ , and  $\beta_p$  are parameters defined by the model with its valued shown on table 1.1.

#### 1.1.6 Band To Band Tunneling

If a sufficiently high electric field exists within a device local band bending may be sufficient to allow electrons to tunnel, by internal field emission, from the valence band into the conduction band. An additional electron is therefore generated in the conduction band and a hole in the valence band. This generation mechanism is implemented into the right-hand side of the continuity equations. The tunneling generation rate is [12] as:

$$G_{BTBT} = BB_A E^{BB\gamma} exp\left(-\frac{BB_B}{E}\right) \tag{1.39}$$

where E is the magnitude of local electric field and  $BB_A = 9.6615e^{18}$ ,  $BB_B = 3e^7 V/cm$ , and  $BB\gamma = 2$  are constant parameters. This bandto-band tunneling model uses the electric field value at each node to give a Generation rate at that point due to the tunneling. In reality, the tunneling process is non-local and is necessary to take into account the spatial profile of the energy bands. It is also necessary to take into account the spatial separation of the electrons generated in the conduction band from the holes generated in the valence band. A model for this process assumes that the tunneling can be modeled as being one-dimensional in nature so that it must be calculated using a special rectangular mesh superimposed over and coupled to the normal mesh. This mesh needs to include the junction region of interest and the direction of the Band-to-Band tunneling must be specified. We must adjust the extent and resolution of the mesh to obtain the best results.

#### 1.2 Self-consistent Poisson-Shroedinger model

The Drift-diffusion model is a good semiconductor physic approximation for most application, but for very thin devices (i10nm) the semiconductor band structure becomes different from the simple case of infinite semiconductor, and quantum confinement phenomena could be present [13]. In order to take into account for quantum phenomena, a enhanced model must be used.

#### 1.2.1 Shroedinger equation

The solution of Schrödinger's Equation gives a quantized description of the density of states in the presence of quantum mechanical confining potential variations. The calculation of the quantized density of states relies upon a solution of Schrödingers Equation.

$$\left(-\frac{\hbar}{2}\frac{\partial}{\partial z}\frac{1}{m_l(z)}\frac{\partial}{\partial z} + E_C(z) + \delta E_V\right)\Psi_{il} = E_{il}\Psi_{il}$$

(1.40)

$$\left(-\frac{\hbar}{2}\frac{\partial}{\partial z}\frac{1}{m_t(z)}\frac{\partial}{\partial z} + E_C(z) + \Delta E_V\right)\Psi_{it} = E_{it}\Psi_{it}$$

(1.41)

where  $E_{it}$  is the i-th eigenvalue energy for transverse mass,  $E_{il}$  is that for the longitudinal mass,  $\Psi_{it}$  is the transverse eigenfunction,  $\Psi_{il}$  is the longitudinal eigenfunction,  $\delta E_V$  is the energy offset for the ladder, and  $E_C$  is the conduction band energy. This expression is for electrons but an equivalent expression exists for holes.

The Schrödinger equation is solved over a finite domain  $[Z_-; Z_+]$ . The endpoints of this domain is defined by the boundary condition:

$$\frac{\Psi_{il}'}{\Psi_{il}} = \pm \frac{\sqrt{2m_{il} \left| E_{il} - E_C \right|}}{\hbar} \tag{1.42}$$

is applied, where for the upper sign, all position-dependent functions are taken at  $Z_+$  and, for the lower sign, at  $Z_+$ .

#### 1.2.2 Statistic

Using Fermi-Dirac statistics, the discrete nature of the quantized density of states reduces the integral over energy to a sum over bound state energies. The expression for the electron concentration then becomes

$$n(x) = 2\frac{kT_L}{\pi h^2} m_t(x) \sum_{i=0}^{\infty} |\Psi_{il}(x)|^2 \ln\left[1 + exp\left(-\frac{E_{il} - E_F}{kT_L}\right)\right] + \frac{kT_L}{\pi h^2} \sqrt{m_l(x)m_t(x)} \sum_{i=0}^{\infty} |\Psi_{it}(x)|^2 \ln\left[1 + exp\left(-\frac{E_{it} - E_F}{kT_L}\right)\right]$$

(1.43)

Once the solution of Schrodingers Equation is taken, carrier concentrations calculated from Equation (1.43) are substituted into the charge part of Poisson's Equation. The potential derived from solution of Poisson's Equation is substituted back into Schrodinger's Equation. This solution process (alternating between Schrodingers and Poissons equations) continues until convergence and a self-consistent solution of Schrodinger's and Poisson's equations is reached.

#### **1.3** Numerical technique

The physical model previously described provide us a set of partial differential equations (PDEs) to be solved. this set of PDEs must be solved on a set of spatpoints defined as a mesh that must describe the entire device. A discretized method will transform the original equations to a discrete nonlinear algebraic system that well approximate the system. This set of approximation, the mesh, and the PDEs set determine the nonlinear numerical problem to be solved.

The non-linear algebraic system is solved using an iterative procedure that refines successive estimates of the solution. Iteration continues until the corrections are small enough to satisfy convergence criteria, or until it is clear that the procedure is not going to converge. The non-linear iteration procedure starts from an initial guess. The corrections are calculated by solving linearized versions of the problem. The linear subproblems are solved by using direct techniques or iteratively.

#### 1.3.1 Mesh definition

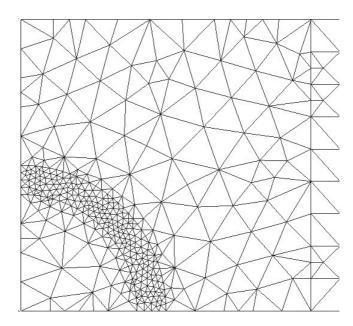

The first step in numerical resolution is the definition of a mesh that cover the entire device space; This mesh must contain enough points to provide the required accuracy, at the same time it's necessary to design a mesh that do not contain too many unnecessary points that impair efficiency. In order to create a good trade-off between this two rules a finite element method has been used.

The finite element method (FEM) is a numerical technique for finding approximate solutions of partial differential equations (PDE) as well as integral equations. The solution approach is based either on eliminating the differential equation completely, or rendering the PDE into an approximating system of ordinary differential equations.

The division of space into triangular spaces to create a non-uniform mesh that helps increase the number of mesh points in regions of space with high values of electric field over the mesh and relax in the less important maintaining good accuracy of the results.

To obtain good results in terms of convergence, efficiency and robustness is essential to define a good mesh that must respect certain rules [14]:

- Must contain a number of points that ensures a good accuracy.

- They must remove unnecessary points that increase simulation time.

- In order to obtain a good accuracy and robustness, it's necessary to reduce at a minimum value the number of obtuse triangles and the triangles long and thin.

• The triangle size must change smoothly in transition from a region where very small triangles must be used to a region where the use of much larger triangles.

Figure 1.2: Example of 2D finite element mesh, intersections as mesh points.

#### 1.3.2 Discretization method

Numerically solve a differential equation means to calculate approximate values of unknown functions in a sufficiently large number of points in space. so you can display the desired solution without permit detailed analysis. In particular, it is important to find an approximate method of approximation of differential operator.

Using the Euler discretization method can transform the system of partial differential equations into a set of nonlinear equations to be expressed in matrix form, which transforms the partial differential operator derived from the values of the unknown neighbors in space. Under these conditions, the Poisson equation is transformed into the following form

$$\|M\|\Phi = R(n,p) + b \tag{1.44}$$

Where ||M|| is the matrix form of second order derivative operator approximation,  $\Phi$  is the unknown vector, R is the space charge density, and  $\tilde{b}$  is the border condition vector. The derivative operator for a one-dimensional problem with  $x \in (0, a)$  can be presented as

$$||M|| = \begin{pmatrix} \alpha_1 + \beta_1 & -\beta_1 & 0 & 0 & \dots & 0\\ \alpha_2 & \alpha_2 + \beta_2 & -\beta_2 & 0 & & 0\\ 0 & \alpha_3 & \alpha_3 + \beta_3 & -\beta_3 & \ddots & 0\\ \vdots & & \ddots & \ddots & \ddots & -\beta_{m-1}\\ 0 & 0 & 0 & \dots & -\alpha_m & \alpha_m + \beta_m \end{pmatrix}$$

(1.45)

where

$$\alpha_i = \frac{2\epsilon}{h_i/(h_i + h_{i+1})}, \ \beta_i = \frac{2\epsilon}{h_{i+1}(h_i + h_{i+1})}$$

(1.46)

and

$$\Phi = \begin{pmatrix} \phi_1 \\ \phi_2 \\ \vdots \\ \phi_m \end{pmatrix}, \quad R = \begin{pmatrix} \rho_1 \\ \rho_2 \\ \vdots \\ \rho_m \end{pmatrix}, \qquad \tilde{b} = \begin{pmatrix} \alpha_1 \phi_D(0) \\ 0 \\ \vdots \\ \beta_m \phi_D(a) \end{pmatrix}$$

(1.47)

where  $h_i$  is the distance in space between i and i - 1 mesh point,  $\rho_i$  is the space charge density evaluated at mesh point, and  $\phi_D$  is the border condition potential at contacts.

Using the same considerations for the continuity equations we can obtain the following system matrix [15]

$$\begin{cases} \|M\| \Phi = \frac{1}{2\epsilon} R(n, p) + \frac{1}{2} \tilde{b} \\ \|M_n\| (\Phi)n = GR(n, p) + \tilde{b}_n \\ \|M_p\| (\Phi)p = GR(n, p) + \tilde{b}_p \end{cases}$$

(1.48)

Now it is important to define an iterative numerical solution to obtain the vectors  $\Phi$ , n, and p. [15]

- 1. We assign an initial guess for the vectors of the density of charge, in fact we assign them an arbitrarily fixed but plausible values, which we denote  $n^{(0)}$ ,  $p^{(0)}$ .

- 2. At this point begins the real iteration map. By induction suppose we have determined the vectors  $n^{(k)}$ ,  $p^{(k)}$ , and  $\Psi^{(k)}$ . We solve the Poisson equation discretized using the values for the density  $n^{(k)}$ ,  $p^{(k)}$ , and denote the solution with (k + 1). briefly write

$$2\epsilon \|M\| \Psi^{(k+1)} = R\left(n^{(k)}, n^{(k)}\right) + \epsilon b$$

(1.49)

3. We solve the equation of continuity for electrons in eq (1.48), after have eliminated the nonlinearity appropriately using the known values. in practice, if we denote by  $n^{(k+1)}$  the value of the new density of electron vector, it is obtained by solving the linear equation

$$\|M\|_{n}\left((Phi^{(k+1)})\right)n^{(k+1)} = GR\left(n^{(k+1)}, n^{(k)}, p^{(k)}\right) + b_{n} \qquad (1.50)$$

and by replacing

$$GR\left(n^{(k+1)}, n^{(k)}, p^{(k)}\right) = \|M\|_{n,GR}^{(k)}, n^{(k+1)} + b_{GR}^{(k)}$$

we obtain

$$\left[ \|M\|_{n}^{(k+1)} + \|M\|_{n,GR}^{(k)} \right] n^{(k+1)} = b_{GR}^{(k)} + b_{n}$$

(1.51)

4. Similarly it is the continuity equation for holes in eq (1.48). More precisely, denote by  $p^{(k+1)}$  the solution of linear problem.

$$\left[ \|M\|_{p}^{(k+1)} + \|M\|_{p,GR}^{(k+1)} \right] p^{(k+1)} = b_{GR}^{(k)} + b_{n}$$

(1.52)

5. At this step, we have  $n^{(k+1)}$ ,  $p^{(k+1)}$ , and  $\Psi^{(k+1)}$  from the previous one. Now we compare two kind of errors: the absolute errors, defined as the maximum variation from the previous solution; and the right hand side error. If it appears that these errors are below a certain tolerance value we can accept vectors as a solution of the coupled system. Otherwise return to step 2.

This iterative method is successful if it ends with the convergence condition is reached, where the error tends to diverge, or are unable to obtain the solution using a reasonable number of iterations, then the simulation stops without getting a new solution, it will be necessary to modify the boundary conditions to obtain an intermediate solution, or modify the structure of the mesh to improve the accuracy of the simulation. [16]

## Part I

### Power MOSFET device analysis

## Chapter 2 Power mosfet devices

Power electronics have been reached a crucial importance in most applications, such as automotive and aerospace applications. In order to achieve good results in terms of performance and reliability lots of studies have been made to get better electrical characteristics like on resistance, thermal dissipation, switching speed, and breakdown voltage.

Power semiconductor devices are more complicated than low-power corresponding devices in terms of operational characteristics and structure more complicated. The added complexity is due to modification made starting from low power devices made to make it ready for high power applications. The main properties that a power device must have [17] are:

- 1. Large breakdown voltage

- 2. Low on resistivity and low on voltage

- 3. fast switching time

- 4. Large power dissipation capability

In all device types, there is a trade-off between breakdown voltage and on-state resistivity. Increasing breakdown voltage will cause a higher blocking voltage for power device, but consequently will produce an increasing in on-state resistivity that causes higher power loss in device on state.

This trade off mean that there is not only one device type useful for all applications. The requirement of the specific application must be matched to the capabilities of the available devices. This will require clever and innovative design approaches.

In the next chapters, the main power devices used in this thesis work are presented and described, with particular attention to electrical characteristics and differences between p-n and MOSFET structures.

#### 2.1 Power diode

The basic semiconductor device is made with p-n junction. In low power application this device is formed by the union of a n-type semiconductor with a p-type one in the same crystal. this kind of junction can be made by diffusing acceptor impurities into an n-type semiconductor crystal, or by diffusing donor impurities into a p-type semiconductor instead.

An important characteristic of p-n junction is how the doping changes from n-type to p-type region. The simplest one is defined as the abrupt change in doping level at junction position, this represent the so called abrupt junction. A more gradually change in doping density is the linearly graded junction that make linearly change in doping level near p-n junction. A real junction instead can be expressed with a gaussian doping profile diffusion. This doping profile came classical profile generated by a diffusion process at high temperature (900 :  $1150^{\circ}C$ ) [18].

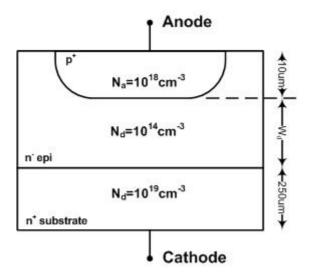

Power diode device are fabricated on a heavily doped n-type substrate on top of which is grown a lightly doped  $n^-$  epitaxial layer of specified thickness. Finally the p-n junction is formed by diffusing a heavily doped p-type region to form the anode of the diode. A typical power diode is shown on figure 2.1 cross section. The cross section area will vary according to the amount of total current the device is designed to carry. The area A will include the Z dimension that will be very large compared with other dimensions. [19, 20]

Figure 2.1: p-n-junction power mosfet diode cross section with its dimensional characteristics and doping levels.

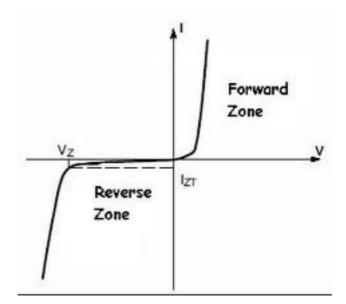

The *i*-v characteristic of the diode is shown on figure 2.2. In forward region current grows linearly instead of a exponentially normal low power diode. This trend is due to large currents in power diode that create ohmic drops that mask the exponential *i*-v characteristic [21].

In reverse bias zone a small negative leakage current will flow until the reverse breakdown voltage  $V_Z$  is reached. When breakdown is reached, the voltage will remain essentially constant while the current increase of several orders of magnitudes, and its grow is limited only by the external circuit limit. The combination of a large current and voltage at breakdown condition leads to a very high power dissipation that cause the destruction of the device. This is the main reason that induce to use very carefully devices in that operation mode, and often it cannot be used.

Figure 2.2: The I-V characteristic of a p-n junction diode.

#### 2.1.1 Basic p-n physics

As first analysis, an abrupt p-n junction is analyzed. The abrupt junction show an immediate change in doping concentration along x direction, changing doping impurities from acceptor  $N_A$  to donor  $N_D$ . A unbalanced junction can be defined if  $N_A >> N_D$ . Starting from one dimensional Poisson equation we obtain

$$-\frac{\partial^2 V}{\partial x^2} = \frac{\partial \xi}{\partial x} = \frac{q}{\epsilon_s} = \frac{\rho(x)}{\epsilon_s} \left[ p(x) - n(x) + N_D^+ - N_A^- \right]$$

(2.1)

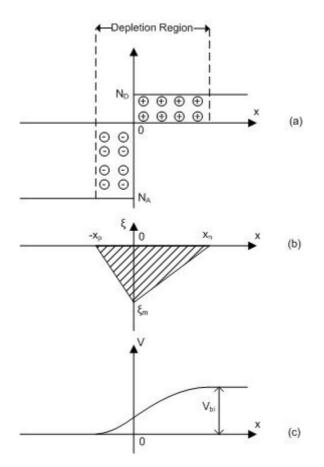

Figure 2.3: One-dimensional visualization of p-n junction in thermal equilibrium. (a) Space-charge distribution. The dashed lines indicate the majoritycarrier distribution tails. (b) Electric field distribution. (c) potential variation with distance x, where  $V_{bi}$  is the built-in potential.

that becomes

$$-\frac{\partial^2 V}{\partial x^2} \approx \frac{\rho(x)}{\epsilon_s} N_A^- \quad \text{for} \quad -x_p \le x < 0 \tag{2.2}$$

$$-\frac{\partial^2 V}{\partial x^2} \approx \frac{\rho(x)}{\epsilon_s} N_D^+ \quad \text{for} \quad 0 < x \le x_n \tag{2.3}$$

The electric field is obtained by integrated equations (2.1) as shown in figure 2.3b

$$\xi(x) = -\frac{qN_A(x+x_p)}{\epsilon_s} \quad \text{for} \quad -x_p \le x < 0 \tag{2.4}$$

$$\xi(x) = -\xi_m + \frac{qN_D x}{\epsilon_s} = \frac{qN_D}{\epsilon_s} \quad \text{for} \quad 0 < x \le x_n \tag{2.5}$$

where  $\xi_m$  is the maximum electric field that exists at x=0 and is given by

$$|\xi_m| = \frac{qN_D x_n}{\epsilon_s} = \frac{qN_A x_p}{\epsilon_s} \tag{2.6}$$

Integrating equation (2.1) once again, Figure 2.3c gives the potential distribution V(x) and the built-in potential  $V_{bi}$

$$V(x) = \xi_m \left( x + \frac{x^2}{2W} \right) \tag{2.7}$$

$$V_{bi} = \frac{1}{2}\xi_m W = \frac{1}{2}\xi_m (x_n + x_p)$$

(2.8)

where W is the total depletion width. Eliminating  $\xi_m$  from equation (2.8) yields

$$W = \sqrt{\frac{2\epsilon_s}{q} \left(\frac{N_A + N_D}{N_A N_D}\right) V_{bi}}$$

(2.9)

for a two-sided abrupt junction. For a one-sided unbalanced abrupt junction, figure (2.9) reduces to

$$W = \sqrt{\frac{2\epsilon_s V_{bi}}{qN_B}} \tag{2.10}$$

where  $N_B = N_D$  or  $N_A$  depending on whether  $N_A >> N_D$  or vice versa.

$$\mathbf{J_n} = q\mu_n n\xi + qD_n \nabla n \tag{2.11}$$

Where  $\mathbf{J}_{\mathbf{n}}$  is the electron current density, q is the elementary charge,  $\mu_n$  is the electron mobility and  $D_n$  is the electron diffusivity. The same equation

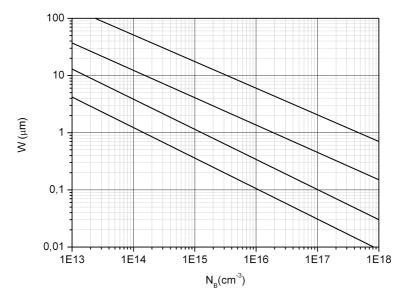

Figure 2.4: depletion-layer width as a function of doping for one-sided abrupt junction in Si for various voltage

can be written for hole current by replacing the electron concentration n, the electron mobility and diffusivity with the holes one. The equation consist of the drift component caused by the field and the diffusion component caused by the carrier concentration gradient. For a one dimensional case equation (2.11) reduce to

$$\mathbf{J_n} = q\mu_n n\xi + qD_n \frac{\partial n}{\partial x} = q\mu_n \left( n\xi + \frac{kT}{q} \frac{\partial n}{\partial x} \right)$$

(2.12)

At equilibrium condition, when no current flows and no voltage is applied, density current inside semiconductor is equal to zero.

Applying a reverse bias to a p-n junction a increase in the depletion regions, and a reverse low value current will be present. This reverse bias current can be approximately given by the sum of the diffusion components in the neutral region and the generation current in the depletion region [3].

# 2.1.2 junction breakdown

The rapid increase in current at reverse-bias voltage over p-n junction is called reverse breakdown, or avalanche breakdown. Operation of p-n junction in breakdown must be avoided because the product of a large voltage and a high current leads to very high power dissipation that will quickly destroy the junction if it's not reduced. The main mechanism that causes breakdown are three: thermal instability, tunneling effect, and avalanche multiplication [3,22].

#### Thermal instability

Thermal instability is a small effect in semiconductor with relatively small bandgap like Ge lattice. In the condition of heat dissipation due to reverse current at high reverse voltage, the junction temperature will increase its value. this temperature increase, increases the reverse current in comparison with its value at lower temperature. Because of the heat dissipation at high reverse voltage, the characteristic shows a negative differential resistance. In this case the diode will be destroyed unless some special measures such as a large series limiting resistor is used. The thermal instability is temperature dependent, in particular breakdown occurs at lower voltage as increasing room temperature.

In Silicon devices, thermal instability can be neglected due to larger bandgap that reduce drastically its effect.

#### Band-To-Band tunneling

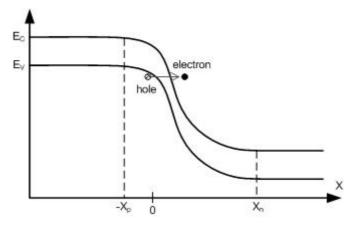

The tunneling effect is a one-dimensional effect related to a square energy barrier. As can be seen in Figure 2.5, in reverse voltage condition the increase in current is generated by electrons in valence band that jump horizontally in conduction band causing a hole-electron pair generation that increases current. This phenomena is related to barrier Height  $E_0$  and thickness W, the quantum-mechanical transmission probability  $T_t$  is given by

$$T_t = \left[1 + \frac{E_0^2 sinh^2 kW}{4E(E_0 - E)}\right]^{-1}$$

(2.13)

with

$$k = \sqrt{\frac{2m(E_0 - E)}{\hbar^2}}$$

(2.14)

where E is the carrier's energy. The probability decreases monotonically with decreasing E. When  $kW \gg 1$ , the probability becomes

$$T_t \approx \frac{16E(E_0 - E)}{E_0^2} exp(-2kW)$$

(2.15)

Finally, the tunneling current density for a p-n junction is given by

$$J_t = \frac{\sqrt{2m^*q^3\xi V}}{4\pi^2\hbar E_g^{1/2}}exp - \frac{q\sqrt{2m^*E_g^{3/2}}}{3q\xi\hbar}$$

(2.16)

Figure 2.5: tunneling effect description on band structure

Figure 2.6: Avalanche breakdown effect on a single electron; impact with holeelectron pair generation.

where  $\xi$  is the electric field at the junction,  $E_g$  the bandgap, V is the applied voltage, and  $m^*$  the effective mass.

When the electric filed approaches  $10^6$  V/cm in Silicon, significant current begins to flow by means of the band-to-band tunneling process. To obtain such a high field, the junction must have relatively high impurity concentrations on both the p and n sides.

# Avalanche Breakdown

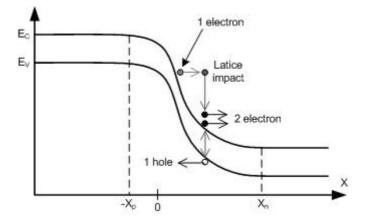

Avalanche multiplication, or impact ionization, is the most important mechanism in junction breakdown, since the avalanche breakdown voltage imposes an upper limit on the reverse bias for most devices, like on the Drain voltage of MOSFETs, and the reverse bias on diodes.

Figure 2.6 describe impact ionization for an electron in a pn junction in reverse bias condition; In particular, the free electron in the conduction band moves to the right due to electric field and increase its energy, when a collision of free electron with lattice occurs, the electron lose its exceeding energy returning to the lower limit of the conduction band. If this transferred energy is sufficiently high, it will generate an electron-hole pair, which may repeat the same sequence [23].

In order to characterize this phenomena in p-n structure, we first derive the basic ionization integral which determines the breakdown condition. Assumes that a current  $I_{p0}$  is incident at the left-side of the depletion region with width W. If the electric field in the depletion region is high enough that electron-hole pairs are generated by the impact ionization process, the hole current  $I_p$  will increase with distance through the depletion region and reaches a value  $M_p I_{p0}$  at W. Similarly, the electron current  $I_n$  will increase from x = W to x = 0. The total current  $(I = I_p + I_n)$  is constant at steady state. The incremental hole current at x equals the number of electron-hole pairs generated per second in the distance dx:

$$d\left(\frac{I_p}{q}\right) = \left(\frac{I_p}{q}\right)(\alpha_p dx) + \left(\frac{I_n}{q}\right)(\alpha_n dx) \tag{2.17}$$

or

$$\frac{dI_p}{dx} - (\alpha_p - \alpha_n) I_p = \alpha_n I \tag{2.18}$$

Where  $\alpha_n$  and  $\alpha_p$  are respectively electron and hole ionization rates. The solution of equation (2.18) with boundary condition that  $I = I_p(W) = M_p I_{p0}$  is given by:

$$I_p(x) = \frac{I\left\{\frac{1}{M_p} + \int_0^x \alpha_n exp\left[-\int_0^x \left(\alpha_p - \alpha_n\right) dx'\right] dx\right\}}{exp\left[-\int_0^x \left(\alpha_p - \alpha_n\right) dx'\right]}$$

(2.19)

where  $M_p$  is the multiplication factor of holes and is defined as

$$M_p = \frac{I_p(W)}{I_p(0)}$$

(2.20)

Equation (2.19) can be written as

$$1 - \frac{1}{M_p} = \int_0^W \alpha_p exp\left[-\int_0^x (\alpha_p - \alpha_n) dx'\right] dx \qquad (2.21)$$

The avalanche breakdown is defined as the voltage where  $M_p$  approaches infinity. Hence the breakdown condition is given by the ionization integral

$$\int_0^W \alpha_p exp \left[ -\int_0^x (\alpha_p - \alpha_n) dx' \right] dx = 1$$

(2.22)

If the avalanche process is initiated by electrons instead of holes, the ionization integral is given by:

$$\int_{0}^{W} \alpha_n exp\left[-\int_{x}^{W} (\alpha_n - \alpha_p) dx'\right] dx = 1$$

(2.23)

Equations (2.22) and (2.23) are equivalent; this means that breakdown condition depends only on what is happening within the depletion region and not on the carriers that initiate the avalanche process.

For semiconductor with equal ionization rates  $(\alpha_n = \alpha_p = \alpha)$ , equations (2.22) and (2.23) reduce to simple expression

$$\int_0^W \alpha dx = 1 \tag{2.24}$$

From the breakdown conditions described above and the field dependence of the ionization rates, the breakdown voltages, maximum electric filed, and depletion layer width can be calculated. As discussed previously, the electric field and potential in the depletion layer are determined from the solutions of Poisson's equation. Depletion layer that satisfy Equation (2.22) can be obtained numerically using an iteration method, like Runge-Kutta method. With known boundaries we obtain

$$BV = \frac{\xi_m W}{2} = \frac{\epsilon_s \xi_m^2}{2q} (N_B)^{-1}$$

(2.25)

for a one-sided abrupt junction where  $N_B$  is the ionized background impurity concentration of the lightly doped side,  $\epsilon_s$  is the silicon dielectric constant, and  $\xi_m$  the maximum electric field.

By using breakdown voltage value obtained by formula (2.25) an solving Poisson equation it can be obtained the depletion layer width as

$$W_{BV} = 2.67e^{10} (N_B)^{-7/8}$$

(2.26)

and the maximum electrical field value

$$\xi_{BV} = \left(\frac{N_B}{2.41e^{-29}}\right)^{1/8} \tag{2.27}$$

The mechanism of breakdown for Silicon junctions with breakdown voltages less than about  ${}^{4}E_{g}/q$  is found to be due to the tunneling effect. For junction with breakdown voltages higher than  $6E_{g}/q$ , the main mechanism is the avalanche multiplication. At voltages  $4E_G/q < V < 6E_G/q$ , the breakdown is due to a mixture of both avalanche and band-to-band tunneling. Since the energy bandgap Eg in Silicon decrease with increasing temperature, the breakdown voltage in that semiconductor due to tunneling effect has a negative temperature coefficient; that is, the voltage decreases with increasing temperature [23].

# 2.2 Power MOSFET

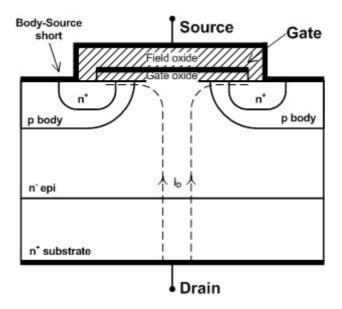

Power MOSFET device differs too from its equivalent low power device for the same reasons expressed before. The power MOSFET structure is no more specular from source-to-drain view, since drain region must be able to support very high blocking voltage; Perhaps this structure has been modified and now is similar to power diode one. A classical power MOSFET is shown in figure 2.7. Starting from a  $n^+$  bottom substrate a  $n^+$  region is grown to form Drain drift region. After what a *p-type* doping implantation is made to form body region, and finally a *n-type* doping implantation inside body region is made to create source region. After doping formation, gate oxide and contact are growth on top of device, so structure is ready.

The doping in the two  $n^+$  end layers, labeled source and drain in figure 2.7, is approximately the same in both layer and is quite large, typically  $10^{19}cm^{-3}$ . The *p*-type middle layer named body is the region where the channel is established between source and drain in a small layer of interface near gate oxide. This region is typically doped at  $10^{16}cm^{-3}$ . The  $n^-$  layer is the drain drift region and is typically doped at  $10^{14} - 10^{15}cm^{-3}$ . This drift region determines the breakdown voltage of the device [24].

If no voltage is applied to gate, there is no contact between source and drain, so no current can flow between the two contacts because one of p-n junctions (either the body-source junction or the drain-body junction) will be reverse biased by either polarity of applied voltage between the drain and source. However, an application of a voltage that biases the gate positive with respect to source will convert the silicon surface beneath the gate oxide into an n-type channel, connecting the source to the drain and allowing the flow of an appreciable current. The current flow vertically from drain contact at bottom device to gate oxide center, pass across body region horizontally at gate-to-body interface, and reach source contact.

The gate thickness, gate width, and the number of devices connected electrically in parallel (with every single contact connected in parallel) are important in determining how much current will flow for a given gate-tosource voltage. The previously described structure is the so called VDMOS, meaning Vertical Diffused MOSFET. The name crudely describe the fabri-

Figure 2.7: Power MOSFET vertical cross section. A single MOS device is often composed of many thousands of cells connected in parallel that replicates this structure.

cation sequence of the device.

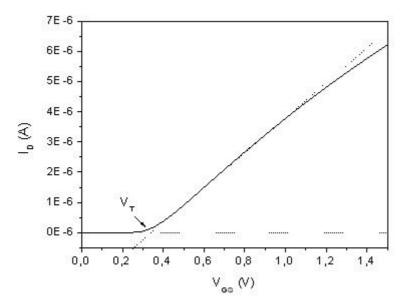

# 2.2.1 *I-V* characteristic

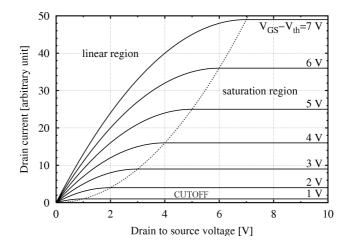

The power MOSFET is a tree terminal device where the gate contact intended as input is electrically isolated and is used to control the flow of current between the other two output terminals source and drain. Figure 2.8 show the output characteristic, drain current  $i_D$  as a function of drainto-source voltage  $V_{DS}$  with gate-to-source voltage  $V_{GS}$  as a parameter.

In power electronic applications, the MOSFET is used as a switch to control the flow of power to de load towards gate contact [25]. In these applications the MOSFET transverses the  $i_D$ -V<sub>GS</sub> characteristics from cutoff trough the active region to the linear region as the device turns on and back again when it turns off. The cutoff, active, and linear region are shown on figure 2.8.

The MOSFET is in cutoff when the gate-source voltage is less than threshold voltage  $V_{th}$ , a typical value for threshold voltage in power MOS-FET applications for an *n*-type is about one volt. The device is an open circuit and must hold off the power supply voltage applied to the circuit. When the device is driven by a large gate-source voltage, it is driven into the linear region where the drain-source voltage  $V_D S$  is small. In this region

Figure 2.8: Drain current to drain voltage characteristic of an n-channel MOSFET at various gate voltages.

the power dissipation can be kept within reasonable bounds by minimizing  $V_{DS}$  even if the drain current is fairly large. The mosfet is in the linear region when

$$v_{GS} - V_{th} > v_{DS} > 0$$

(2.28)

In the active region the drain current is independent from the drainsource voltage and depends only to gate-source voltage. Can be said that in this operational region, drain current is saturated. A simple first order theory predicts that in the active region the drain current is given by

$$i_D = K(v_{GS} - V_{th})^2 \tag{2.29}$$

Where K is a constant that depends on device geometry. This simple model don't take into account of some parasitic effects like:

- bjt parasitic effect related to *n-p-n* junctions respectively from sourcebody-drain.

- the presence of two devices side by side produce a jfet effect in drift drain region under the gate due to body-to drain depletion region.

- the high structure's parallelization cause a source increase in on state resistance.

This characteristics are related to VMOSFET, some other power MOS-FET structures can reduce such effects.

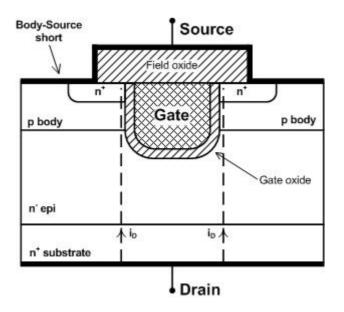

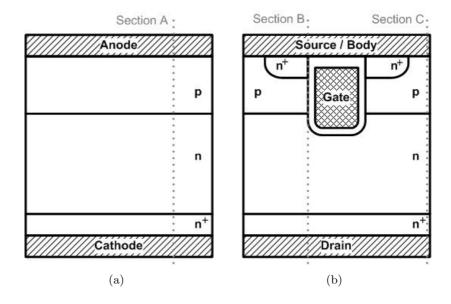

# 2.3 Trench Power MOSFET

The Trench power MOSFET, or UMOSFET, represent a variation from power VDMOSFET design that have the advantage of higher cell density but is more difficult to manufacture than the planar device [26]. Trench power MOSFET device structure is presented in figure 2.9. This new device topology put the two gate channels vertically at the interface between p-body and gate oxide regions.

Figure 2.9: Trench power MOSFET device cross section

In fact, trench power MOSFET device fabrication start with an epitaxial growth of n-epi drain layer, followed by a trench formation with a etching process will be made. this process must be very accurate to ensure a low roughness on its border because a higher roughness can increase the on resistivity. After trench formation the gate oxide oxidation and poly gate deposition will be made. Subsequently a p-type doping implantation is made to form body region, and a n-type doping implantation inside body region near trench edges are made to create source regions. Finally a field oxide is put on top of the trench to electrically isolate gate to source contact and the three contacts are realized.

# 2.3.1 Trench power MOSFET breakdown

MOSFET devices have two voltage ratings that should not be exceeded:  $V_{GSmax}$  and  $BV_{DSS}$ . The maximum allowable gate-source voltage  $V_{GSmax}$

Figure 2.10: Electric field contour lines in Trench power MOSFET's cross section at breakdown condition

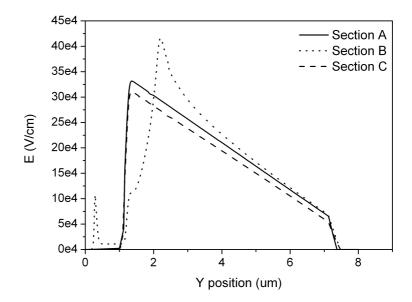

is determined by the requirement that the gate oxide not be broken down by large electric fields. Good-quality thermally grown  $SiO_2$  breaks down at electric field values on the order of  $5e^6 - 10e^6$  v/cm. This means that a gate oxide 100nm thick can theorically support a gate-source voltage of 50-100 V. For a Trench device the voltage value will decrease by a factor  $2\pi r$  due tu the trench bottom rounding gate that create a tip effect increasing local electric field value. The maximum allowable drain-source voltage  $BV_{DSS}$ is the largest voltage the MOSFET can hold off without avalanche breakdown of the drain-body p-n junction. Large values of breakdown voltage are achieved by the use of the lightly doped drain drift region. The lightly doped drift region is used to contain the depletion layer of the reverse biased drain-body junction. The length of the drift region is determined by the desired breakdown voltage rating. The electric field maximum value on Trench device is no more on bulk-drain junction, as for a simple junction, the maximum electric field shift nearing trench's border. Figure 2.10 show electrical field cross section in a Trench power MOSFET device in breakdown condition  $BV_{DSS}$ . As can be noted, the maximum electric field is placed on trench rounding shape neighborhood [27].

# Chapter 3

# Trench power MOSFET simulations

As described above, using a device simulator allows to obtain experimental results on structures not yet been realized or to evaluate the internal features that otherwise would be impossible to analyze. This chapter uses the numerical techniques described above for simulations of Trench power MOSFET devices. After an initial setup and testing of the model setup and simulation were carried out a series of simulations to identify the main parameters that influence the breakdown voltage and identify the cause. Furthermore, the result was compared in terms of breakdown of the trench structure with a pn junction structure reference.

# 3.1 Simulation setup

To obtain good simulation results it is essential that every aspect of the simulation is well defined. In particular:

- Set up a physical model that includes the main phenomena that may occur

- The structure must be built properly in terms of size and doping

- The device mesh must show a good trade-off between a mesh with enough mesh points to allow a good degree of approximation, and one with the fewest points to help you get quick results

- Te numerical resolution method must show an adequate level of approximation of all the electrical parameters to be evaluated.

Finally, it is good practice to check that the simulation result is correct, trying to explain the physics of the device or by comparing the results obtained with a simulation of a test device. In order to obtain a high current value with low resistivity, a power MOSFET device is made by the union of a large number of MOSFET devices shorted in parallel, the single devices are very long and occupy all the die width. [26]

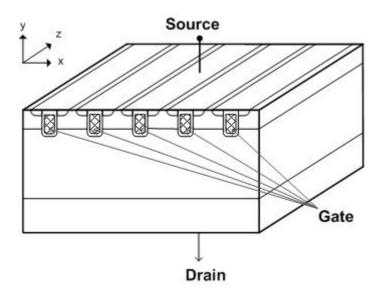

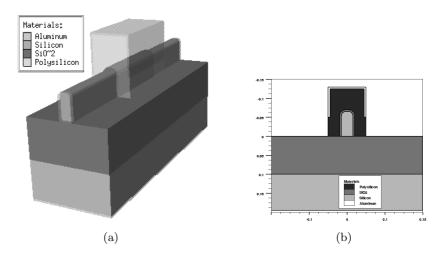

Figure 3.1: Schematic design of classical Trench power MOSFET device

The structure does not change its characteristics in the Z direction, this allow to create two-dimensional simulations assuming that along the

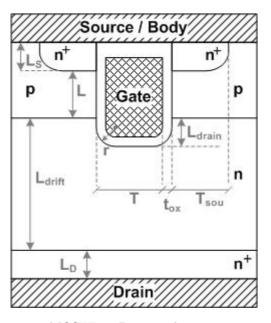

Figure 3.2: Trench power MOSFET 2D vertical cross section with its main geometrical parameters

Z direction the electrical characteristics does not change; This is a good approximation since power devices are very large [20, 28].

Trench power MOSFET structure is described in figure 3.2. The gate is located at structure's top-center, the bulk and source regions are shorted in a single contact (Source), and drain is placed at structure's bottom. Drain doping have different doping concentration from top to bottom direction; in particular there are two different regions; a drift region with a lower doping concentration and a fixed length on top, and a substrate region with higher doping level to ensure lower resistivity. Drift region doping level is not constant, a Gaussian distribution near the bottom interface with n+ region is present. This Gaussian distribution came from diffusion process that move doping atoms from substrate to drift region. The diffusion length is calculated as the distance between bulk-drain p-n junction and the depth where doping reaches the value of 2 times drift doping value, this distance is called for simplicity drift length.

The trench's shape exceed the bulk region and penetrate inside drain drift region, this length is called Ltrench and is evaluated as the vertical distance between bulk-to-drain p-n junction and the lower point in trench oxide-semiconductor interface.

The structure's main characteristics default values are shown on table 3.1. The structure was simulated using the drift diffusion model, with the

| Name        | Value            | Description                                      |

|-------------|------------------|--------------------------------------------------|

| T           | 750nm            | Trench width                                     |

| $t_{ox}$    | 100nm            | Oxide thickness                                  |

| $t_{sou}$   | 250nm            | Source pad width                                 |

| $t_{Tot}$   | $7\mu m$         | Domain simulation length                         |

| r           | 200nm            | Trench's bottom radius                           |

| $L_S$       | 75nm             | Source pad depth                                 |

| L           | $1 \mu m$        | Gate length                                      |

| $L_{drain}$ | 300nm            | Trench penetration into drain region             |

| $L_{drift}$ | $4.5 \mu m$      | Drain lighly doped region depth                  |

| $L_D$       | $0.5 \mu m$      | Drain strongly doped region depth                |

| $L_{Tot}$   | $6.1 \mu m$      | Total simulation height                          |

| $N_S$       | $1e^{20}cm^{-3}$ | Source pad <i>n</i> -type doping concentration   |

| $N_G$       | $1e^{20}cm^{-3}$ | Gate polysiliocn <i>n</i> -type doping conc.     |

| $N_B$       | $2e^{18}cm^{-3}$ | Body <i>p</i> -type doping concentration         |

| $N_{drift}$ | $3e^{15}cm^{-3}$ | Drain <i>n</i> -type lighly doped doping conc.   |

| $N_D$       | $1e^{20}cm^{-3}$ | Drain <i>n</i> -type strongly doped doping conc. |

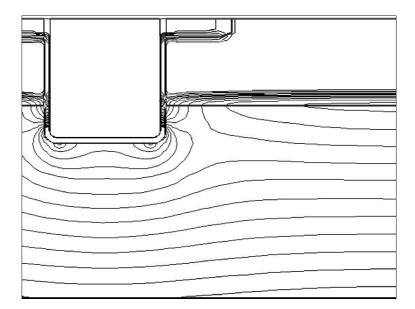

Table 3.1: Default geometrical and doping concentration values

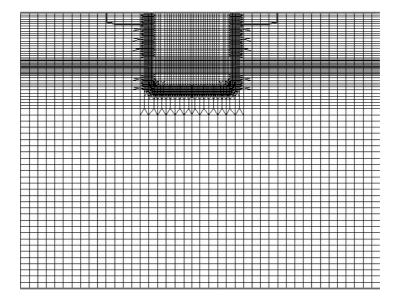

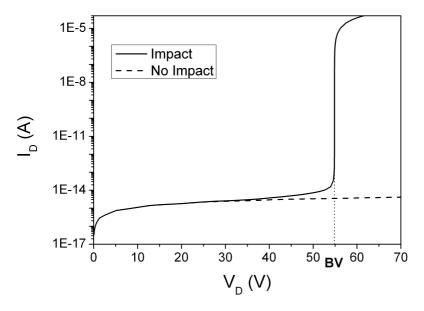

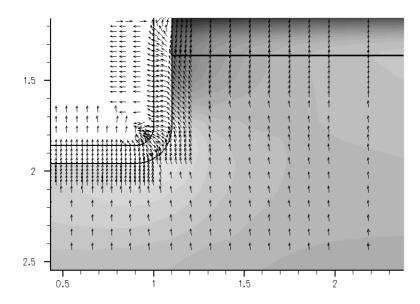

addition of impact ionization model to properly simulate the breakdown phenomenon. Figure 3.3 shows mesh description of default Trench MOS structure, the following mesh is made by the union of two different finite element method meshes: one with square mesh points, in areas with uniform and triangular elements, and one with a FEM mesh with triangular shape where the density of points increases by grade. In particular, the mesh is thickened near the region of oxide trench, regions in which we find a triangular mesh, the mesh in the remaining structure maintains the rectangular shape which allows a more simple numerical analysis. [29] Near the bodydrain junction, the mesh is thickened in the y direction only, so it is not necessary to use a triangular mesh to increase the density of points. The number of simulation points to the following structure is 7088, with 7002 elements, of whom 460 triangular and 6542 rectangular, the solution to a problem of this type requires about 0.45-5.21sec.

# 3.1.1 pn reference structure setup

The trench structure's breakdown phenomena is somehow linked to the breakdown of a p-n structure where the p-type region is the bulk region and the n-type region is the drain region; The junction is unbalanced, since doping of the p region is much greater than the doping of the region n,

Figure 3.3: Trench structure mesh description

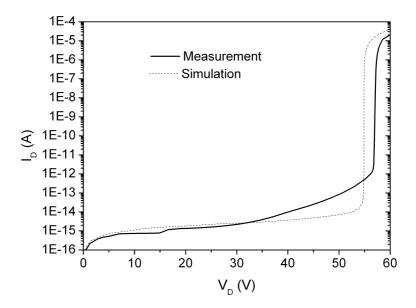

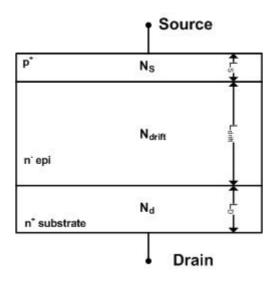

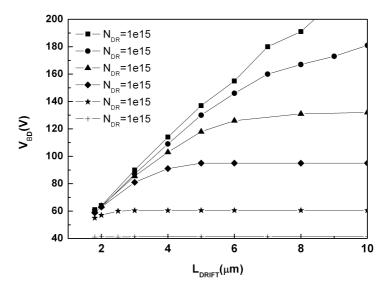

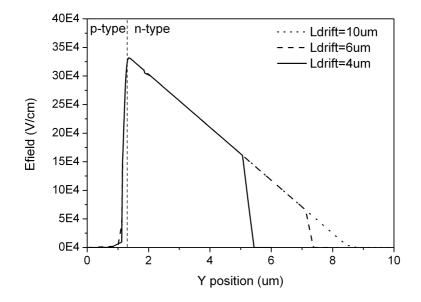

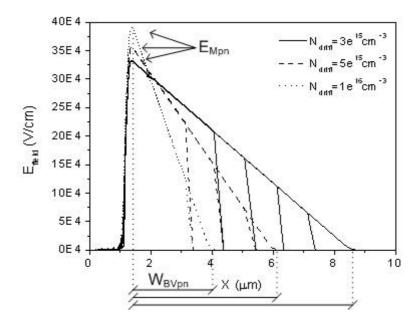

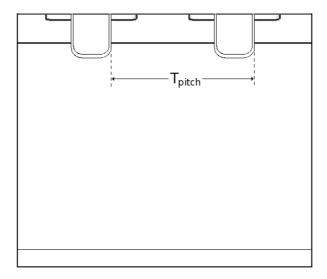

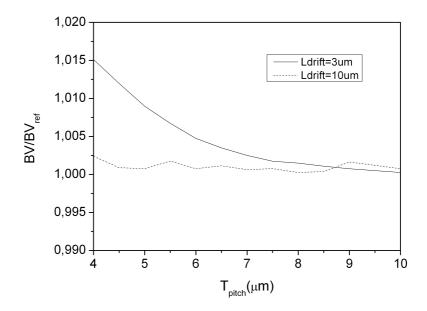

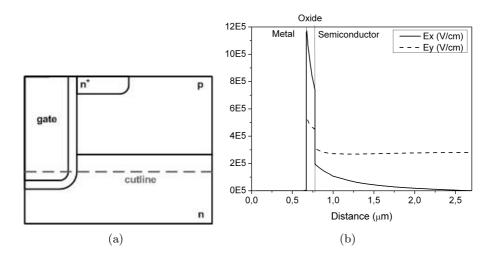

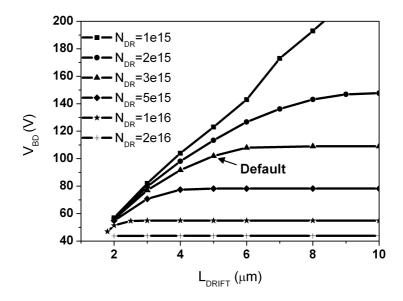

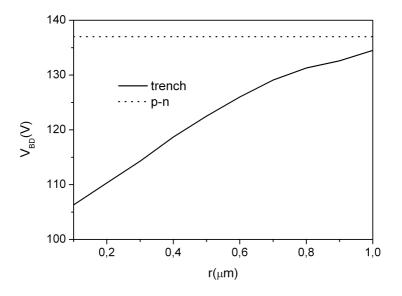

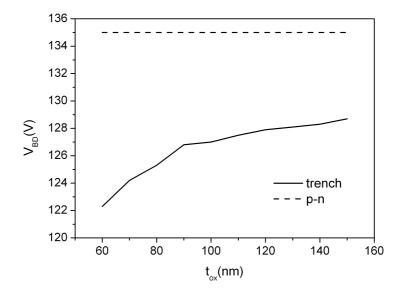

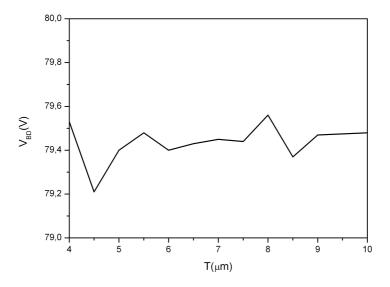

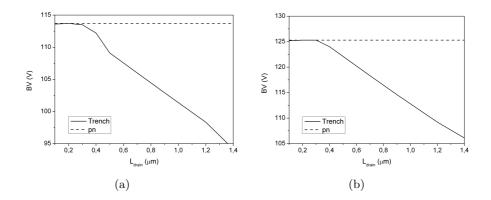

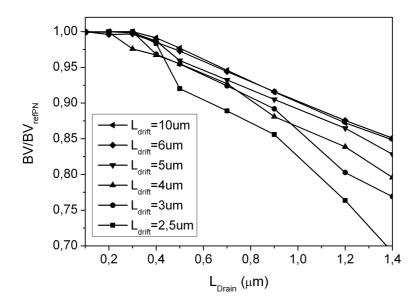

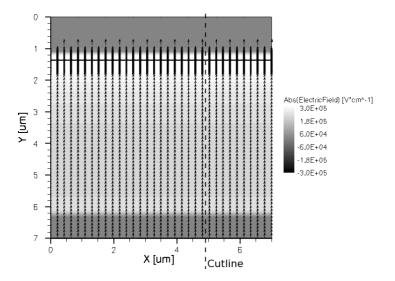

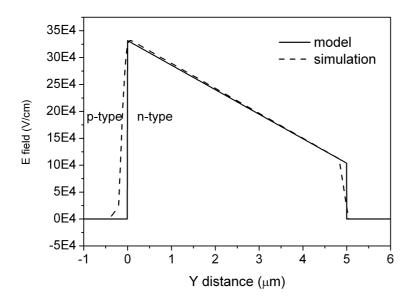

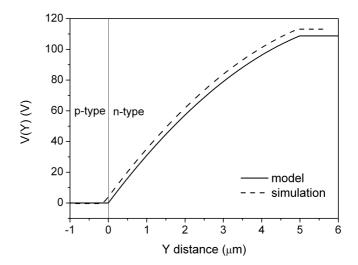

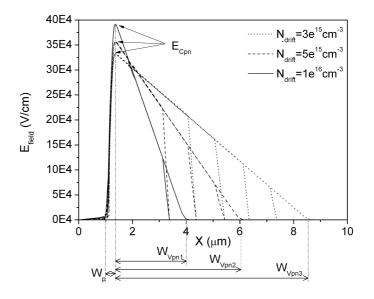

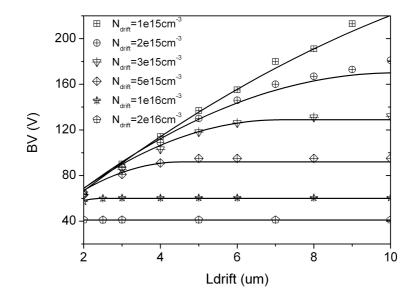

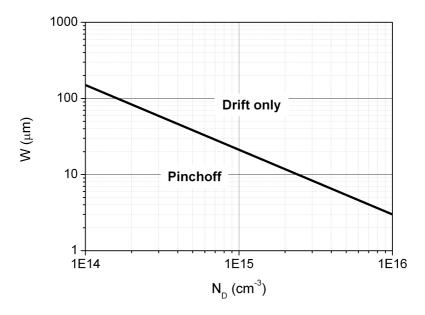

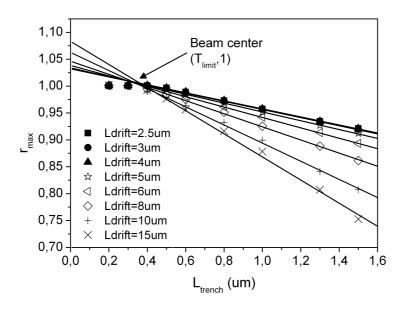

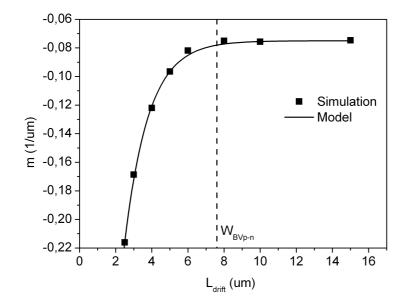

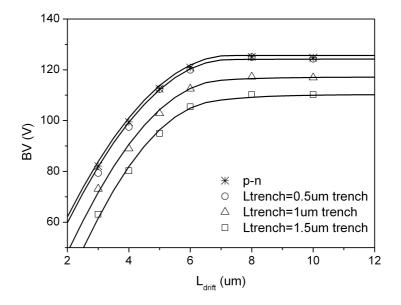

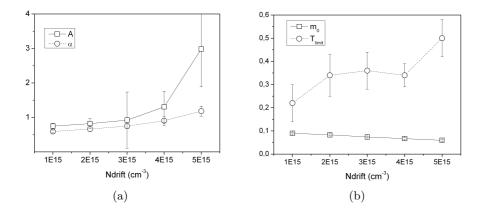

perhaps the drain region is the only one to be discussed. [30]