# Università della Calabria

Dipartimento di Informatica, Modellistica, Elettronica e Sistemistica

Dottorato di Ricerca

in

Information and Communication Technologies

XXXIII Ciclo, Settore disciplinare: ING-INF/01

# Progettazione di circuiti a bassissima potenza e tensione per System on Chip energicamente autonomi

Coordinatore: Ch.mo Prof. Felice Crupi

Firma oscurata in base alle linee guida del Garante della privacy Firma......

Supervisore: Ch.mo Prof. Marco Lanuzza

Firma oscurata in base alle linee guida del Garante della privacy

Firma.....

Dottorando: Dott. Luigi Fassio

Firma oscurata in base alle linee guida del Garante della privacy Firma.....

# Università della Calabria

Dipartimento di Informatica, Modellistica, Elettronica e Sistemistica

Thesis for the degree of Doctor of Philosophy

in

Information and Communication Technologies

33° Cycle, Disciplinar sector: ING-INF/01

## Design of Ultra-Low Power and Voltage circuits for energy autonomous System on Chip

Coordinator: Prof. Dr. Felice Crupi

Email: felice.crupi@unical.it

Supervisor: Prof. Dr. Marco Lanuzza

Email: m.lanuzza@dimes.unical.it

Student: Luigi Fassio Email: luigi.fassio@unical.it I.fassio.92@gmail.com

Alla mia famiglia,

a Tiara, la mia nuova famiglia

Ringrazio il Professor Lanuzza, Professor Crupi e Professor Alioto per

l'opportunità data e il lavoro svolto e un ringraxiamento speciale a Raffaele per la

pazienza e il grande aiuto dato.

## **Table of Contents**

| List of Figures       | 1 |

|-----------------------|---|

| List of Tables        |   |

| List of Abbreviations | 6 |

| Sommario              |   |

| Abstarct              |   |

| Introduction          |   |

#### Chapter 1: Energy Harvesting for System-on-Chip and Design

| of Ultra-     | -low Power/Voltage Circuits                            |    |

|---------------|--------------------------------------------------------|----|

| 1.1 Energy-H  | Iarvested System on Chip                               |    |

| 1.1.1         | Energy harvesting sources                              |    |

| 1.1.2         | Super-micro capacitors                                 |    |

| 1.2 Design of | f Ultra-low Power/Voltage Circuits                     |    |

| 1.2.1         | MOSFET operation in subthreshold region                |    |

| 1.2.2         | Impact of process variability in subthreshold circuits |    |

|               | f CMOS Voltage and Current References                  | 34 |

|               | bltage Reference down to 0.25-V, 5.4-pW Operation      |    |

| 2.1.1 F       | Proposed architecture and operating principle          |    |

| 2.1.2 N       | Aeasurement results in 180-nm process                  |    |

| 2.1.3 0       | Comparison with the state of the art                   |    |

| 2.2 From a Vo | bltage Reference to a Current Reference                | 50 |

| 2.2.1 F       | Proposed architecture and operating principle          | 50 |

| 2.2.2 Measurement results in 180-nm process | 53 |

|---------------------------------------------|----|

| 2.2.3 Comparison with the state of the art  | 59 |

| Chapter 3: Design of a Corner-Aware CMOS Voltage Reference for   |     |

|------------------------------------------------------------------|-----|

| Purely-Harvested Systems                                         | 62  |

| 3.1 Circuit Architecture and Operating Principle                 | 62  |

| 3.2 Oscillator-Based On-Chip Process Sensor                      | 63  |

| 3.2.1 Measurement results in 180-nm process                      | 66  |

| 3.3 Basic ULP/ULV Voltage Reference Circuit                      | 69  |

| 3.3.1 Measurement results in 180-nm process with and without     |     |

| corner-aware replica combination                                 | 71  |

| 3.4 Comparison with the state of the art                         | 75  |

| Chapter 4: Design of an Ultra-Low Voltage Level Shifter          | 78  |

| 4.1 Prior Art on Level Shifter Designs                           | 78  |

| 4.2 Ultra-Low Voltage Level Shifter with High-Speed and          |     |

| Energy-Efficient Operation                                       | 79  |

| 4.2.1 Proposed solution and operating principle                  | 80  |

| 4.2.2 Measurement results in 180-nm process                      | 82  |

| 4.2.3 Comparison with the state of the art                       | 88  |

| Chapter 5: Design of Ultra-Low Power Dynamic Voltage Comparators | 90  |

| 5.1 Dynamic Voltage Comparator (DVC)                             | 90  |

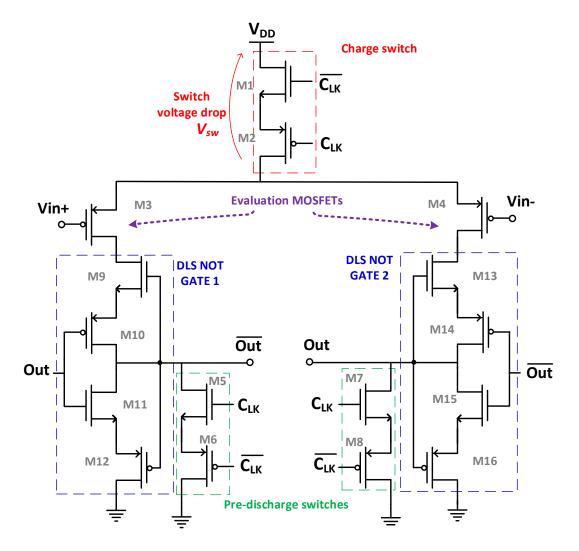

| 5.2 Dynamic Leakage Suppression (DLS) Logic                      | 92  |

| 5.3 Ultra-Low Power Single-Stage DLS-Based DVC                   | 95  |

| 5.3.1 Measurement results in 180-nm process                      | 96  |

| 5.4 Ultra-Low Power Dual-Stage DLS-Based DVC                     | 98  |

| 5.4.1 Measurement results in 180-nm process                      | 101 |

| 5.5 Comparison with the state of the art                         | 105 |

| Conclusion                                                       | 107 |

| Bibliography                                                     | 109 |

| List of Publications                                             | 119 |

### **List of Figures**

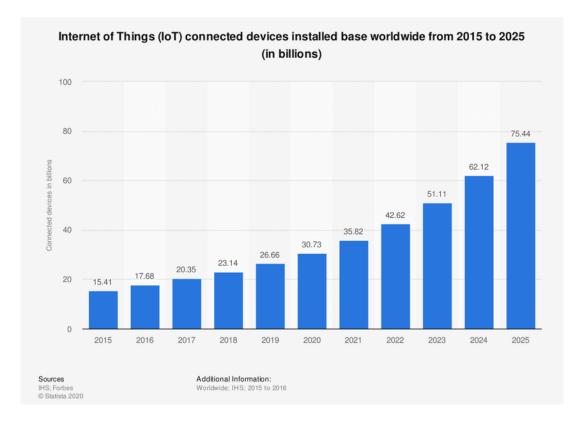

- 1 This statistic represents the number of connected devices (Internet of Things-IoT) in the world between 2015 and 2025. In 2025, the source predicted that 75.44 billion connected objects would be in circulation worldwide [4].

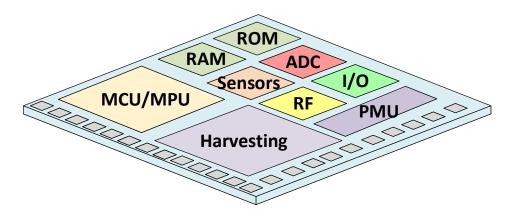

- 1.1 A System-on-Chip integrates on die all the blocks needed to solve its tasks.

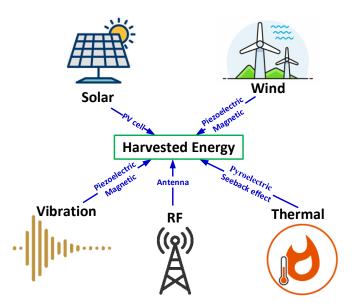

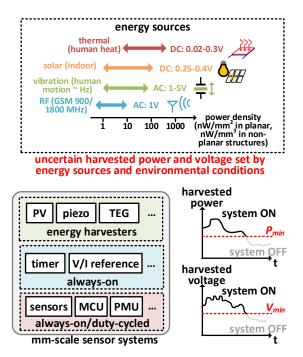

- 1.2 Energy harvesting sources and conversion methods.

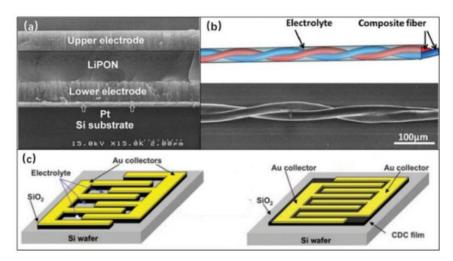

- 1.3 The common structure of MSCs: (a) standard sandwich MSCs, (b) wire-shaped fibrous MSCs, and (c) interdigital MSCs. Figure from [29].

- 1.4 Low minimum voltage  $(V_{min})$  and minimum power  $(P_{min})$  are desirable in energyharvested SoCs to prolong operation under unfavorable conditions.

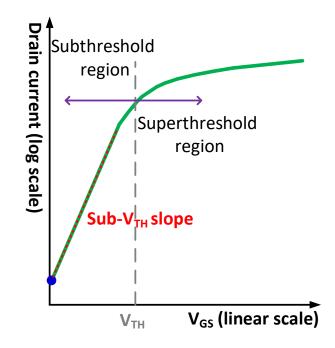

- 1.5 MOSFET current-voltage characteristics highlighting the subthreshold and superthreshold operating regions. In the superthreshold region, the current is fairly linear, whereas in the subthreshold regime it is exponentially dependent on V<sub>GS</sub>.

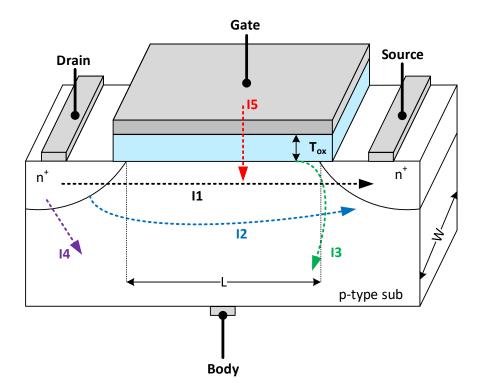

- 1.6 Structure of an n-channel MOSFET with different current contributions.

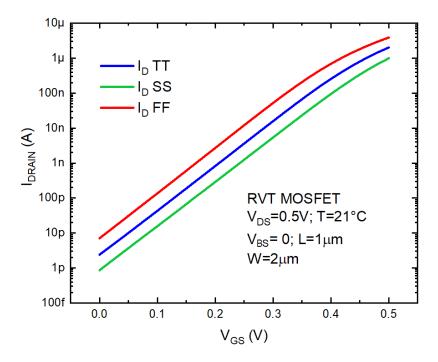

- 1.7 Measurement results for an nMOSFET (regular threshold voltage RVT device, L = 1 $\mu$ m,  $W = 2 \mu$ m, T = 21°C,  $V_{BS} = 0$  V and  $V_{DS} = 0.5$  V) from corner wafer chips.

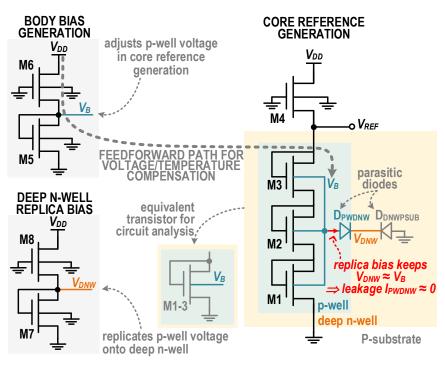

- 2.1 Schematic of the proposed voltage reference.

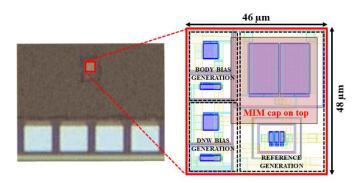

- 2.2 Die photo and layout of the proposed voltage reference.

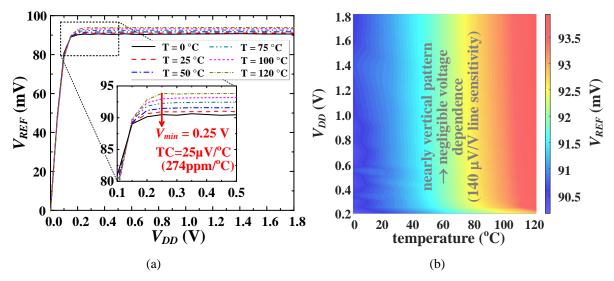

- 2.3 (a) Measured reference voltage vs. supply voltage at several temperatures, (b) color map of reference voltage across supply voltages and temperatures.

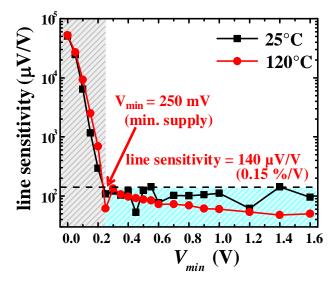

- 2.4 Measured line sensitivity vs. minimum supply voltage  $V_{min}$  (evaluated in the voltage range from  $V_{min}$  up to the 1.8 V nominal voltage) at 25°C and 120°C.

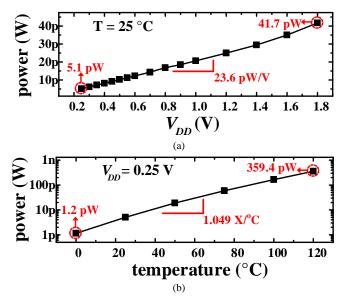

- 2.5 Measured power consumption versus (a) the supply voltage at 25 °C, (b) temperatures at  $V_{DD} = 0.25$  V for a typical sample.

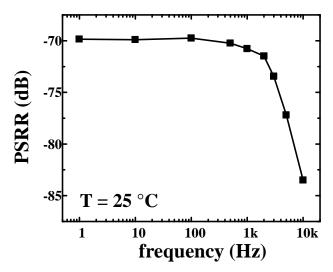

- 2.6 Measured power supply rejection ratio (PSRR) vs. frequency at 25°C for a typical sample.

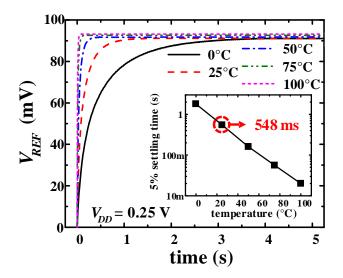

- 2.7 Measured start-up waveform of  $V_{REF}$  for different temperatures at  $V_{DD} = 0.25$  V. The inset shows the 5% settling time vs. temperature

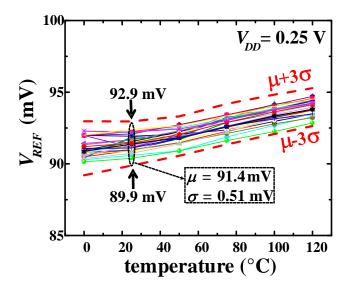

- 2.8 Measured  $V_{REF}$  vs. temperature across 30 die samples at  $V_{DD} = 0.25$  V.

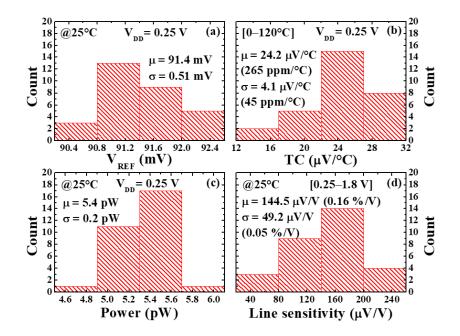

- 2.9 Measurements histogram across 30 die samples: (a)  $V_{REF}$  at 25 °C and  $V_{DD}$ = 0.25 V, (b) temperature coefficient at  $V_{DD}$ =0.25 V, (c) power consumption at 25 °C and  $V_{DD}$ =0.25 V, (d) line sensitivity at 25°C.

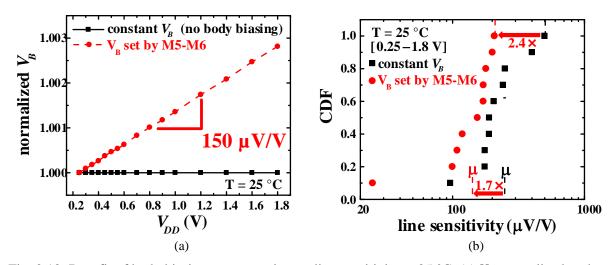

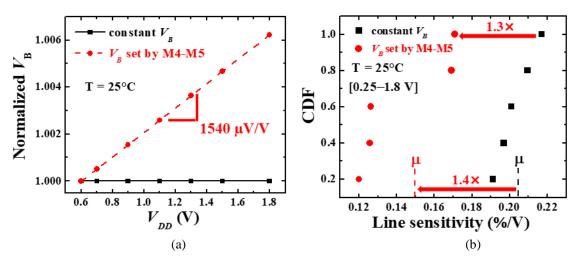

- 2.10 Benefit of body biasing compensation on line sensitivity at 25 °C: (a)  $V_B$  normalized to the value at  $V_{DD}$ =0.25 V vs.  $V_{DD}$  for a typical sample, b) cumulative distribution function (CDF) of line sensitivity across die samples.

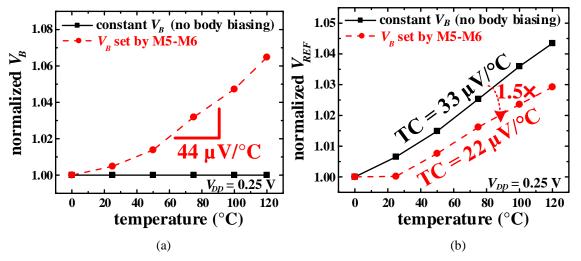

- 2.11 Benefit of body biasing compensation on temperature coefficient at  $V_{DD}$ =0.25 V: (a)  $V_B$  normalized to the value at 0°C vs. temperature, (b)  $V_{REF}$  normalized to the value at 0 °C vs. temperature for a typical sample.

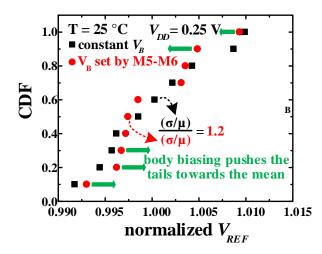

- 2.12 Benefit of body biasing compensation on process sensitivity, as shown by the cumulative distribution push towards the mean (25 °C,  $V_{DD}$ =0.25 V).

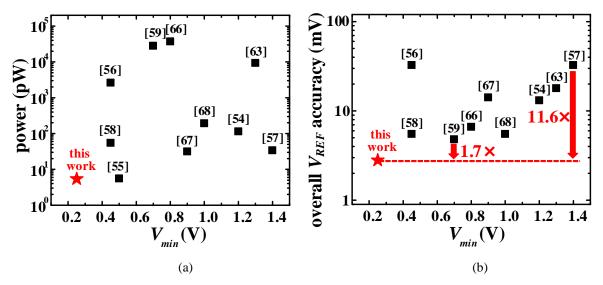

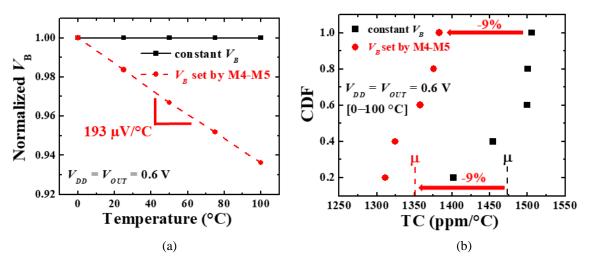

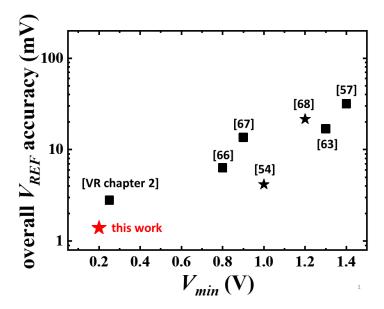

- 2.13 (a) Power and (b) absolute  $V_{REF}$  accuracy vs.  $V_{min}$  in state-of-the-art voltage references fabricated in the same 180-nm technology generation.

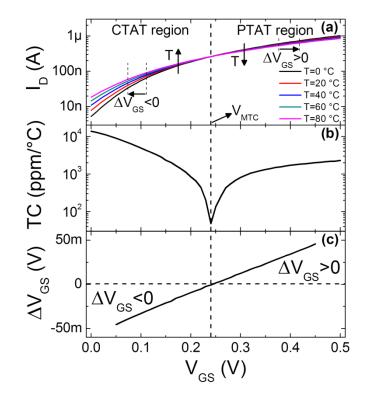

- 2.14 (a)  $I_D$ - $V_{GS}$  characteristics of a typical nMOSFET at different temperatures, (b) temperature coefficient *TC* versus  $V_{GS}$ , and (c) required  $\Delta V_{GS}$  at different  $V_{GS}$  for temperature compensation [39].

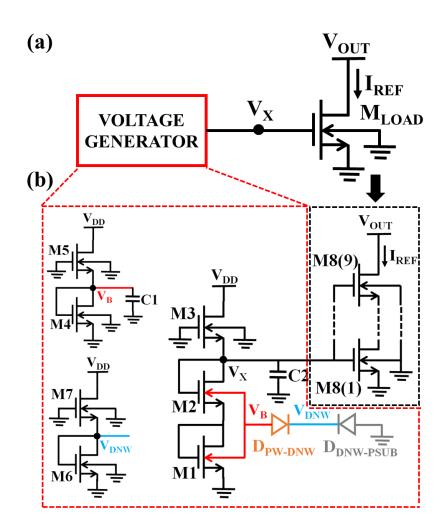

- 2.15 (a) Conceptual diagram and (b) schematic of the proposed current reference.

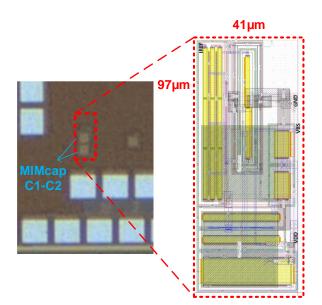

- 2.16 Die photo and layout of the proposed current reference.

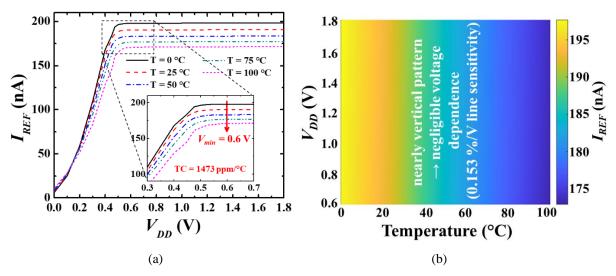

- 2.17 (a) Measured reference current vs. supply voltage at several temperatures, (b) color map of reference current across supply voltages and temperatures ( $V_{OUT} = 0.6$  V).

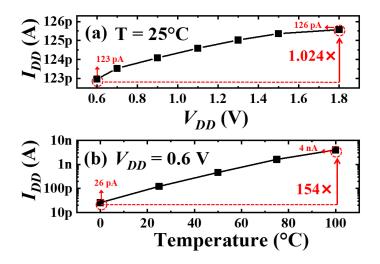

- 2.18 Measured supply current versus (a) the supply voltage at 25 °C, (b) temperatures at  $V_{DD}$ = 0.6 V for a typical sample ( $V_{OUT}$  = 0.6 V in both cases) for a typical sample.

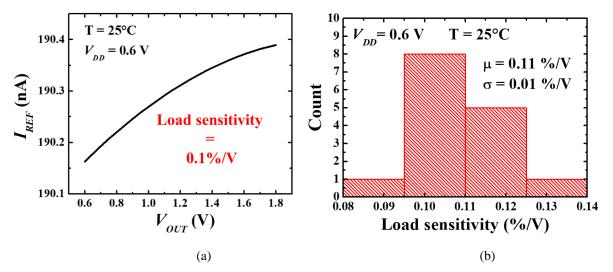

- 2.19 Measured reference current vs.  $V_{OUT}$ , i.e., load sensitivity for (a) a typical sample and (b) across 15 die samples at  $V_{DD} = 0.6$  V and 25 °C.

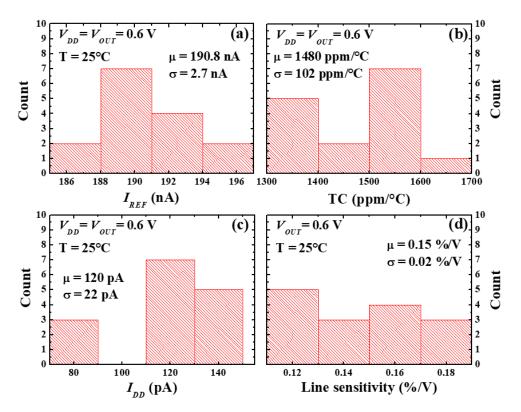

- 2.20 Measurements histogram across 15 die samples: (a)  $I_{REF}$  at 25 °C and  $V_{DD} = V_{OUT} = 0.6$ V, (b) temperature coefficient at  $V_{DD} = V_{OUT} = 0.6$  V, (c) supply current at 25 °C and  $V_{DD} = V_{OUT} = 0.6$  V, (d) line sensitivity at 25°C and  $V_{OUT} = 0.6$  V.

- 2.21 Benefit of body biasing on line sensitivity at 25 °C and  $V_{OUT} = 0.6$  V: (a)  $V_B$  normalized to the value at  $V_{DD} = 0.6$  V vs.  $V_{DD}$  for a typical sample, b) cumulative distribution function (CDF) of line sensitivity across die samples.

- 2.22 Benefit of body biasing on temperature coefficient at  $V_{DD} = V_{OUT} = 0.6$  V: (a)  $V_B$  normalized to the value at 0°C vs. temperature, (b) cumulative distribution function (CDF) of temperature coefficient across die samples.

- 2.23 (a) Power excluding  $I_{REF}$  contribution vs. area and (b)  $I_{TOT}/I_{REF}$  vs.  $V_{min}$  in state-of-the-art current references fabricated in the same 180-nm technology generation.

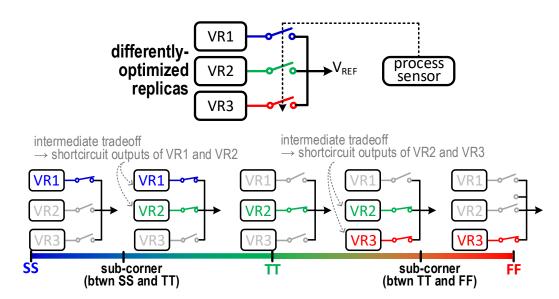

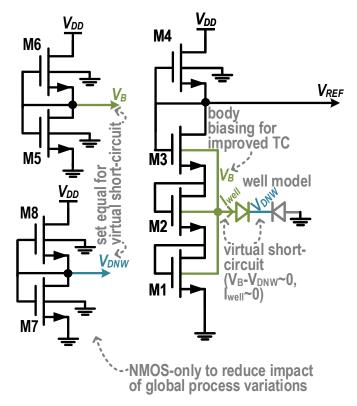

- 3.1 Scheme and operating principle of the proposed NMOS-only corner-aware architecture.

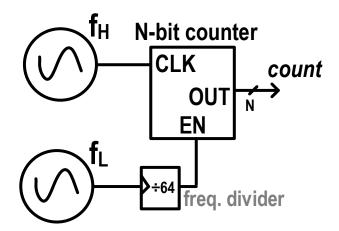

- 3.2 Process sensor architecture.

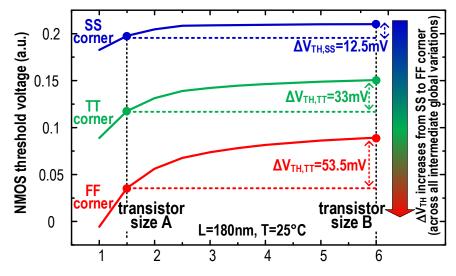

- 3.3 Operating principle of the process sensor: process corners can be detected with a pair of circuits sized as A and B by reading out a circuit parameter that depends on V<sub>TH</sub> (i.e., the oscillator frequency).

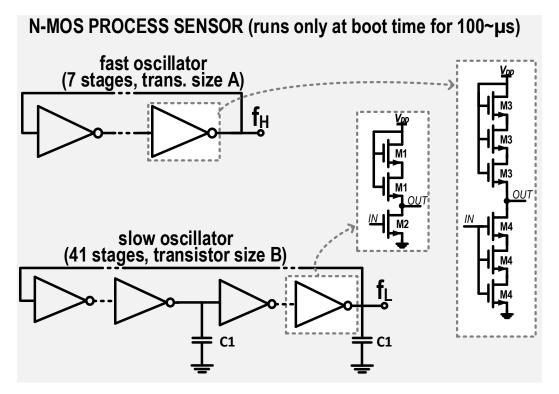

- 3.4 Schematic of implemented fast and slow oscillators.

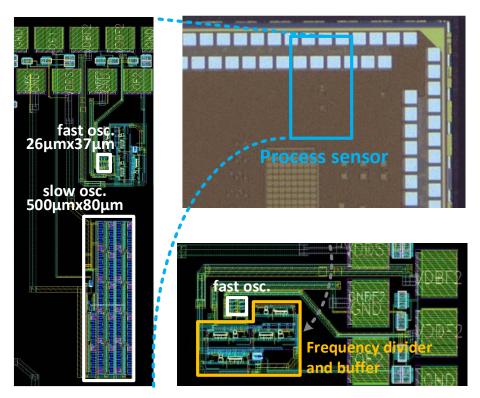

- 3.5 Layout of the implemented oscillators and chip micrograph.

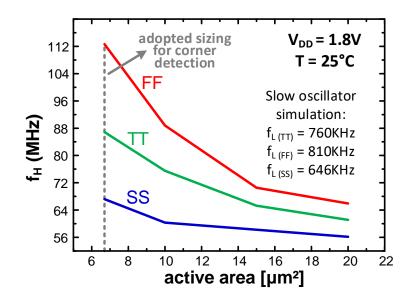

- 3.6 Frequency of the fast oscillator as function of the active area for  $V_{DD} = 1.8$  V and 25°C from corner simulation analysis.

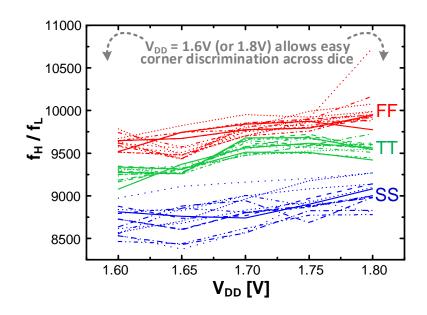

- 3.7 Measured frequency ratio between the two oscillators as a function of  $V_{DD}$  at 25 °C across corner dice.

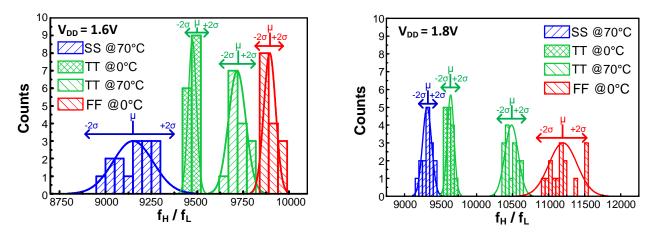

- 3.8 Measured statistical distribution of the frequency ratio between the two oscillators across dice, temperature, and voltage variations.

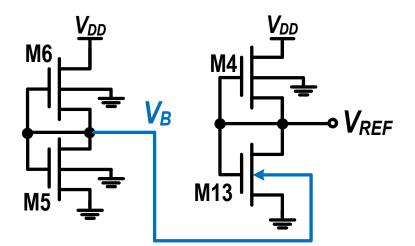

- 3.9 Schematic of the basic voltage reference circuit used for each corner replica.

- 3.10 Simplified circuit analysis of the basic reference circuit in Fig. 3.9 with M1-M3 lumped into a single transistor M13.

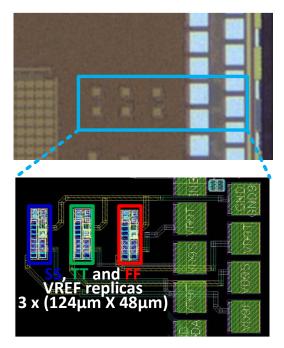

- 3.11 Layout of the voltage reference replicas and die micrograph.

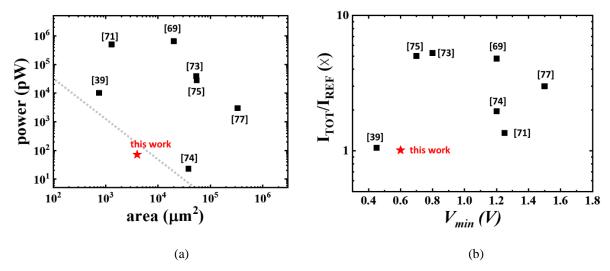

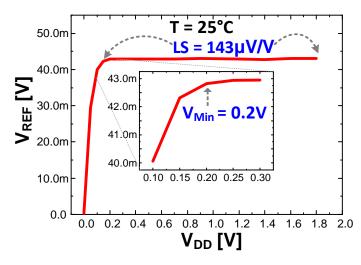

- 3.12 (a) Measured reference voltage vs. supply voltage at room temperature in the case of typical behavior.

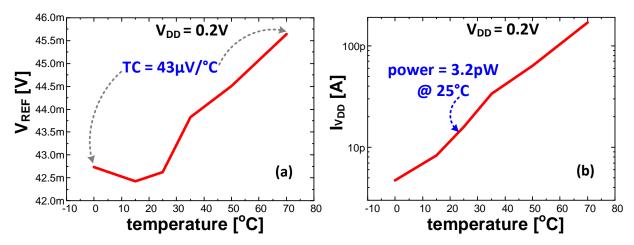

- 3.13 Measured (a) reference voltage and (b) supply current as a function of temperature in the case of typical behavior.

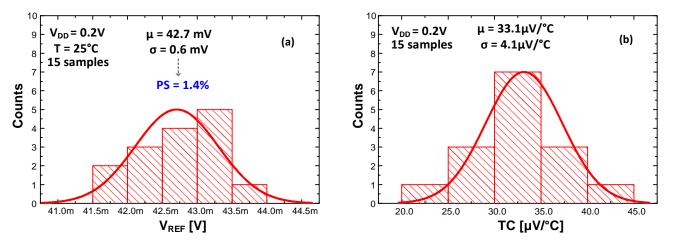

- 3.14 Measured statistical distribution of (a) reference voltage (at 0.2 V and 25 °C) and (b) temperature coefficient (at 0.2 V) for the TT circuit replica across 15 TT test chips.

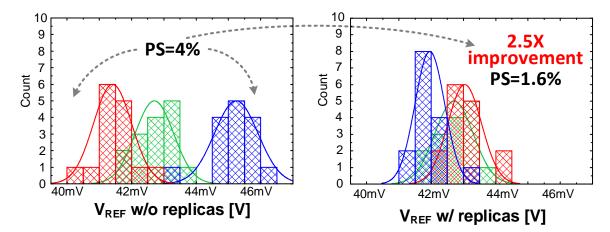

- 3.15 Measured statistical distribution of reference voltage (at 0.2 V and 25 °C) w/o and w/ replica selection across corners.

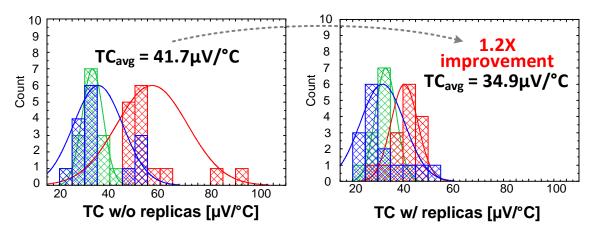

- 3.16 Measured statistical distribution of temperature coefficient (at 0.2 V) w/o and w/ replica selection across corners.

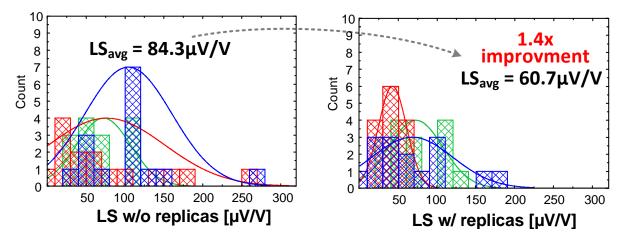

- 3.17 Measured statistical distribution of line sensitivity (at 25 °C) w/o and w/ replica selection across corners.

- 3.18 Absolute  $V_{REF}$  accuracy vs.  $V_{min}$  in state-of-the-art voltage references fabricated in the same 180-nm technology generation. Start symbols denote results from corner wafer measurements.

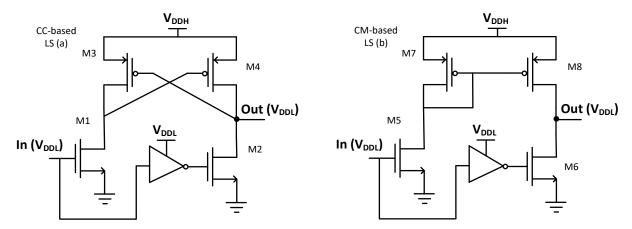

- 4.1 Schematic of conventional (a) cross-coupled (CC) and (b) current mirror (CM) based level shifter topologies.

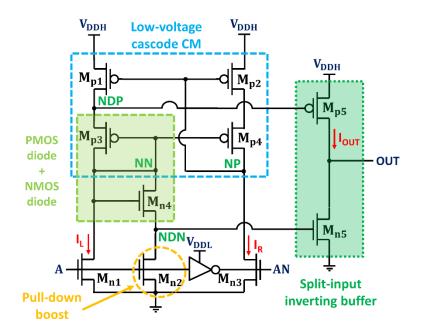

- 4.2 Schematic of the proposed level shifter.

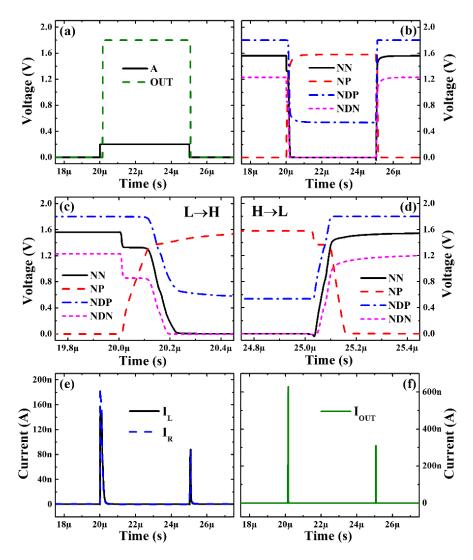

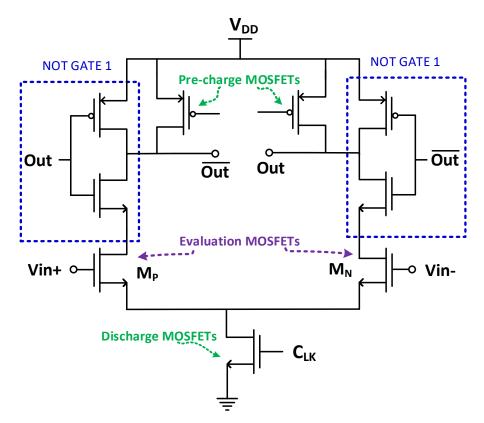

- 4.3 Simulated transient behavior of the proposed level shifter for a voltage up-conversion from 200 mV up to 1.8 V. (a) Input (A) and output (OUT) voltages. (b) Voltages at internal nodes (NN, NP, NDP, and NDN). (c)-(d) Details of NN, NP, NDP, and NDN signals during L $\rightarrow$ H and H $\rightarrow$ L transitions. (e) Left- and right-branch currents (*I*<sub>L</sub> and *I*<sub>R</sub>). (f) Current of the output stage (*I*<sub>OUT</sub>).

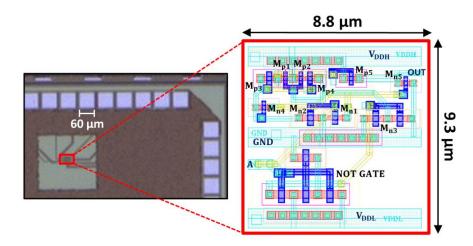

- 4.4 Micrograph of the fabricated test chip and layout of the proposed level shifter.

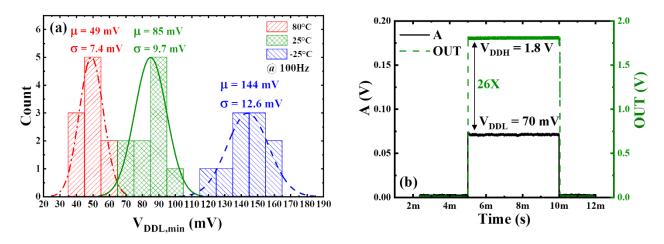

- 4.5 (a) Statistical distribution of measured minimum V<sub>DDL</sub> for successful up-conversion to the nominal supply voltage (1.8 V) at different temperatures (-25 °C, 25 °C, and 80 °C), and (b) measured input (A) and output (OUT) waveforms for 70 mV→1.8 V conversion at 25 °C.

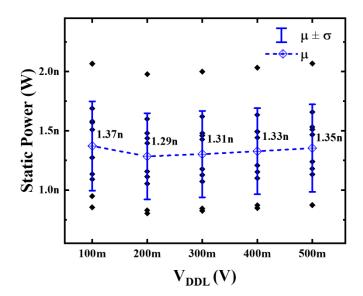

- 4.6 Measured static power as a function of  $V_{DDL}$  for  $V_{DDH} = 1.8$  V at 25 °C. 1- $\sigma$  error bars and mean ( $\mu$ ) plot are also shown.

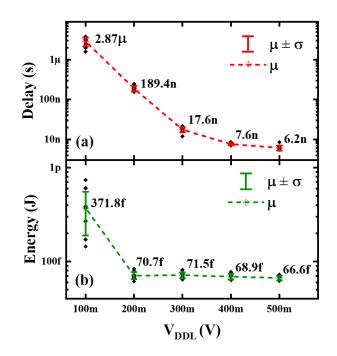

- 4.7 Measured (a) delay and (b) energy per transition (100-kHz input signal) as a function of  $V_{DDL}$  for  $V_{DDH} = 1.8$  V at 25 °C. 1- $\sigma$  error bars and mean ( $\mu$ ) plot are also shown.

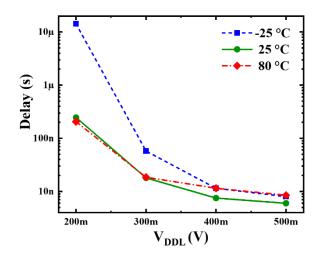

- 4.8 Measured delay as a function of  $V_{DDL}$  for a typical sample at  $V_{DDH} = 1.8$  V and three different temperatures (-25 °C, 25 °C, and 80 °C).

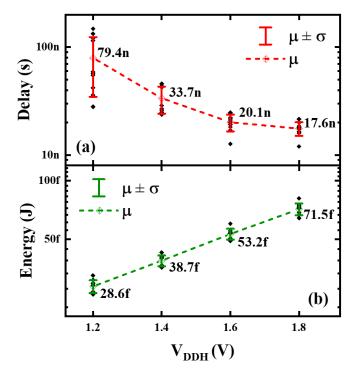

- 4.9 Measured (a) delay and (b) energy per transition (100-kHz input signal) as a function of  $V_{DDH}$  for  $V_{DDL} = 0.3$  V at 25 °C. 1- $\sigma$  error bars and mean ( $\mu$ ) plot are also shown.

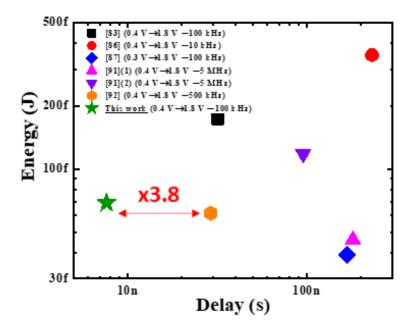

- 4.10 Energy-delay comparison against state-of-the-art level shifters fabricated in 180-nm CMOS.

- 5.1 Schematic of a conventional dynamic voltage comparator.

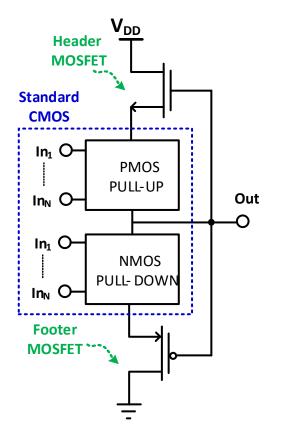

- 5.2 Basic structure of DLS logic gates.

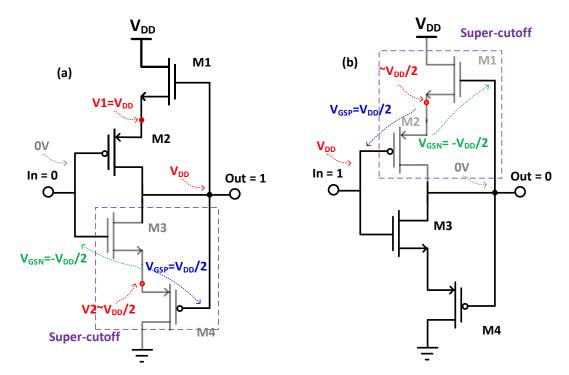

- 5.3 DLS NOT gate with (a) logic 'zero' and (b) logic 'one' at the input, highlighting the voltage across the transistors.

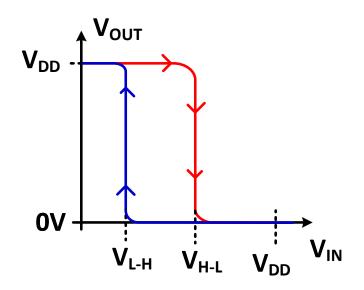

- 5.4 Static transfer characteristics of a DLS NOT gate.

- 5.5 Schematic of the single-stage DLS-based DVC with pre-discharge phase.

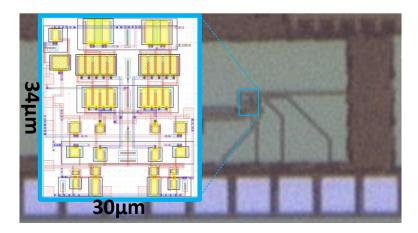

- 5.6 Layout and chip micrograph of the proposed ULP single-stage DLS-based DVC.

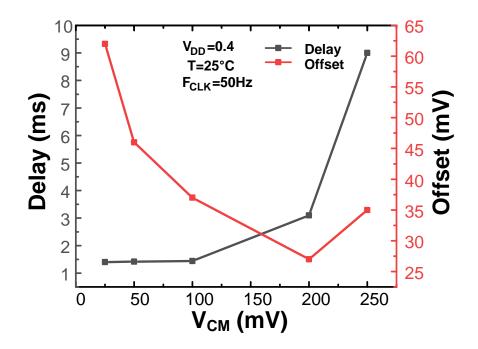

- 5.7 Measured delay and offset voltage vs.  $V_{CM}$  for  $V_{DD} = 0.4$  V, 25 °C, and 50-Hz clock frequency for one sample.

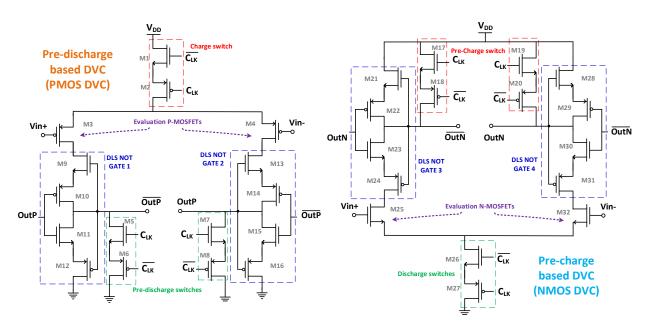

- 5.8 Schematic of single-stage DVCs: (left) pre-discharge based and (right) pre-charge based structures.

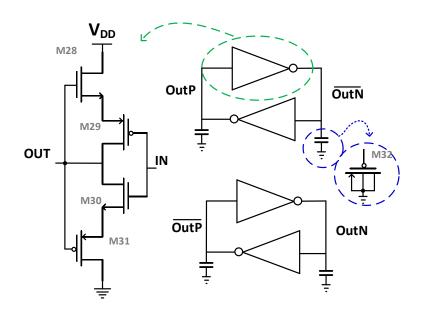

- 5.9 Interconnection circuit between the output nodes of the two single-stage structures.

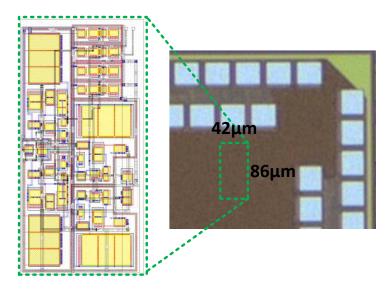

- 5.10 Layout of the proposed DVC and die micrograph with area occupancy.

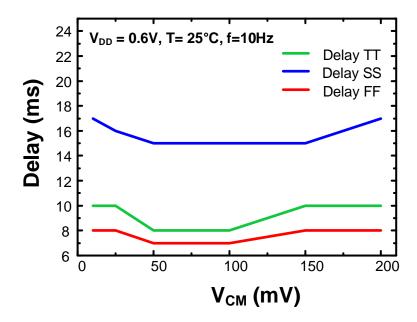

- 5.11 Measured delay vs.  $V_{CM}$  for  $V_{DD} = 0.6$  V, 25 °C, and 10-Hz clock frequency in the three test chips (TT, SS and FF corner wafers).

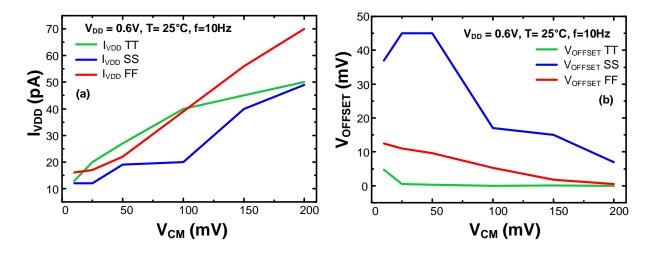

- 5.12 Measured (a) current consumption (a) and (b) offset voltage (b) as function of  $V_{CM}$  for  $V_{DD} = 0.6$  V, 25 °C, and 10-Hz clock frequency in the three test chips (TT, SS and FF corner wafers).

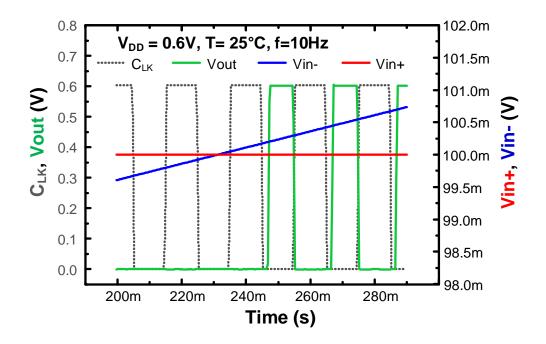

- 5.13 Measured input and output signals of the proposed dual-stage DVC for  $V_{DD} = 0.6$  V, 25 °C, and 10-Hz clock frequency in the three test chips (TT corner chip).

## **List of Tables**

- 1.1 Comparison of the available output powers from different energy harvesting sources.

- 1.2 Comparison of recent Micro Super-Capacitors technologies.

- 2.1 Adopted transistor flavor and sizing for the proposed voltage reference

- 2.2 Performance summary and comparison with the state-of-art voltage references (best performance in bold).

- 2.3 Adopted transistor flavor and sizing for the proposed current reference.

- 2.4 Performance summary and comparison with the state-of-art current references (only measured data and best performance in bold).

- 3.1 Transistor sizing for the implemented oscillators.

- 3.2 Adopted transistor sizing for the three replicas of the voltage reference circuit, each optimized at different corners for minimum process sensitivity and temperature coefficient (in bold sizes varying across different optimizations).

- 3.3 Performance summary and comparison with state-of-the-art voltage references (best performance in bold).

- 4.1 Transistors type and sizing for the proposed level shifter.

- 4.2 Comparison of the proposed level shifter with the state of the art.

- 5.1 Transistor flavor and sizing of the single-stage ULP DVC.

- 5.2 Transistor flavor and sizing for the dual-stage DLS-based DVC.

- 5.3 Comparison of two proposed DLS-based DVCs against state-of-the-art designs.

## List of Abbreviations

| ADC    | Analog to digital converter                       |

|--------|---------------------------------------------------|

| Bio-Z  | Bioelectrical impedance                           |

| BTBT   | Band-To-Band Tunnelling                           |

| CDF    | Cumulative Distribution Function                  |

| CMOS   | Complementary MOS                                 |

| CMR    | Common Mode Range                                 |

| CTAT   | Complementary to Absolute Temperaure              |

| DC     | Direct current                                    |

| DIBL   | Drain-Induced Barrier Lowering                    |

| DLS    | Dynamic Leakage Suppression logic                 |

| DNW    | Deep n-well                                       |

| DVC    | Dynamic voltage comparator                        |

| ECG    | Electrocardiogram                                 |

| EM     | Electro Magnetic                                  |

| ETR    | Energy per Transition                             |

| GIDL   | Gate-Induced Drain Leakage                        |

| IC     | Integrated Circuit                                |

| ID     | Drain current                                     |

| IoT    | Internet of Things                                |

| IP     | Intellectual Property                             |

| Li-ion | Lithium ione                                      |

| LP     | Low Power                                         |

| LS     | Level Shifter                                     |

| LV     | Low Voltage                                       |

| MCU    | Micro Controller Unit                             |

| MEMS   | Micro Electro-Mechanical Systems                  |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MPPT   | Maximum Power Point Tracker                       |

| MSC    | Micro Super Capacitor                             |

| MTC    | Minimum Temperatur Coefficient                    |

| MVT    | Medium/Low Threshold Voltage                      |

| NiCd   | Nickel-Cadmium                                    |

|        |                                                   |

| NiMH            | Nickel Metal Hidrate                |

|-----------------|-------------------------------------|

| PDN             | Pull-Down Network                   |

| PLL             | Phase-Locked Loop                   |

| PSRR            | Power Supply Rejection Ratio        |

| PTAT            | Proportional to Absolute Temperaure |

| PUN             | Pull-Up Network                     |

| PVC             | PhotoVoltaic cell                   |

| PVT             | Process Voltage Temperature         |

| RF              | Radio Frequency                     |

| RFID            | Radio Frequency Identification      |

| RVT             | Regular Threshold Voltage           |

| SAR             | Successive Approximation Register   |

| SoC             | System-on-Chip                      |

| TC              | Temperature Coefficient             |

| ULP             | Ultra Low Power                     |

| ULV             | Ultra-Low Voltage                   |

| V <sub>BS</sub> | Body to Source Voltage              |

| V <sub>DS</sub> | Drain to Source Voltage             |

| V <sub>GS</sub> | Gate to Source Voltage              |

| VLSI            | Very Large Scale Integration        |

| VR              | Voltage Reference                   |

| VTH             | Threshold Voltage                   |

| ZTC             | Zero Temperature Coefficient        |

|                 |                                     |

### Sommario

I circuiti integrati a bassissima potenza e tensione (ULP/ULV) sia digitali che analogici hanno riscosso un notevole interesse da parte della comunità scientifica negli ultimi anni. L'avvento dell'era dell'Internet of Things (IoT) ha inoltre incrementato l'interesse del mercato nello sviluppo di circuiti ULP/ULV in modo tale da realizzare Systems-on-Chip (SoCs) energicamente autonomi e con dimensioni estremamente ridotte. Reti di sensori wireless, dispositivi biomedici impiantabili, sensori indossabili, sistemi di controllo ambientale intelligenti, monitoraggio della qualità dell'aria, controllo di condizioni nei depositi e nei campi agricoli sono solo alcuni dei campi applicativi che possono beneficiare dalla progettazione di circuiti ULP/ULV.

La progettazione di blocchi circuitali ULP/ULV per SoC energeticamente autonomi è un argomento ampio e necessita di alcune conoscenze sui diversi elementi che possono comporre questi SoC. A tal riguardo, il presente lavoro di tesi fornisce innanzitutto una panoramica generale sui SoC energeticamente autonomi con un focus sulle fonti di raccolta di energia ("energy harvesting") disponibili e sulle diverse soluzioni di accumulo di energia.

La disponibilità di soluzioni di raccolta e accumulo di energia integrabili su chip apre la strada allo sviluppo di nodi sensori IoT senza batteria e sposta la sfida verso la progettazione di circuiti ULP/ULV tali da far funzionare il nodo anche con bassissime quantità di energia disponibile. Tra i vari elementi costitutivi chiave dei SoC, questa tesi presenta il progetto di circuiti di riferimento di tensione/corrente finalizzati alla generazine di una polarizzazione DC precisa e stabile in un'ampia gamma di condizioni operative, un traslatore di livello per interfacciare i blocchi operanti tra diversi domini di tensione e comparatori per interfacciare il mondo analogico con quello digitale.

In primo luogo, viene presentato un circuito di riferimento di tensione a bassa area in grado di funzionare a una tensione di alimentazione di soli 250 mV e 5.4 pW di consumo energetico a temperatura ambiente. Il circuito proposto sfrutta uno schema di polarizzazione del body ("body biasing") per contrastare l'effetto delle fluttuazioni di tensione/temperatura e quindi per garantire una buona precisione della tensione di uscita generata, come dimostrato attraverso misure su un chip di test fabbricato con una tecnologia CMOS a 180 nm. Viene inoltre presentato e convalidato mediante misure su un prototipo a 180 nm il progetto di un circuito di riferimento di corrente basato su un generatore di tensione che sfrutta la struttura utilizzata per

il riferimento di tensione. Il circuito proposto funziona correttamente fino a una tensione minima di 0.6 V per generare una corrente nel range di nA con solo 4.000 µm<sup>2</sup> di superficie occupata, raggiungendo allo stesso tempo un'elevata efficienza energetica garantita dal consumo di potenza nel range di pW nel sottoblocco del generatore di tensione. Quindi, viene proposto il progetto di un riferimento di tensione basato sull'impiego di un sensore di processo su chip con l'obiettivo di ottenere una bassa sensibilità alle variazioni di processo e una buona precisione complessiva rispetto alle variazioni di processo-tensione-temperatura, garantendo allo stesso tempo un funzionamento ULP/ULV (ovvero tensione di alimentazione minima di 200 mV e consumo energetico di soli 3.2 pW a temperatura ambiente). I risultati sperimentali in una tecnologia CMOS a 180 nm su wafer d'angolo dimostrano l'efficacia della soluzione proposta. Inoltre, viene presentato il progetto di un robusto traslatore di livello in grado di convertire tensioni di ingresso dal regime di sottosoglia (circa 100 mV) fino alla tensione di alimentazione nominale (1.8 V). Il circuito proposto si basa su una topologia a specchio di corrente cascode a bassa tensione auto-polarizzata che include transistor PMOS e NMOS collegati a diodo per pilotare efficacemente il buffer utilizzato come stadio di uscita in modo da ottenere un'elevata efficienza energetica. I risultati sperimentali ottenuti in una tecnologia CMOS a 180 nm e attraverso i wafer d'angolo dimostrano una buona robustezza e buone prestazioni del traslatore di livello proposto rispetto ai circuiti proposti in letteratura. Infine, viene proposto il progetto di un comparatore ULP/ULV implementato utilizzando la famiglia logica DLS. In particolare, vengono presentate due diverse topologie di comparatore, ovvero una struttura a singolo stadio e un'architettura a doppio stadio basata sulla combinazione di due comparatori a singolo stadio. I risultati sperimentali su chip di test fabbricati in una tecnologia a 180 nm dimostrano un consumo di potenza nell'ordine di poche decine di pW.

### Abstract

Ultra-low power/voltage (ULP/ULV) circuits (both analog and digital blocks) have been gaining considerable interest from the scientific community in the last few years. The advent of the Internet of Things (IoT) era has also increased the interest of the market in ULP/ULV circuits addressed to energy-autonomous and extremely small-sized Systems-on-Chip (SoCs). Wireless sensor networks, biomedical implantable devices, wearable computing, ambient control intelligence, air quality monitoring, warehouse, and agriculture monitoring are just some of the fields that can benefit from ULP/ULV circuits.

The design of ULP/ULV circuit blocks for energy-autonomous SoCs is a wide topic and needs some knowledge on several elements that can compose these SoCs. In this regard, this thesis first provides a general overview on energy-autonomous SoCs with a focus on available energy harvesting sources and energy storage solutions.

The availability of on-chip energy harvesting/storage opens the route for the development of battery-less IoT sensor nodes and moves the challenge towards the design of ULP/ULV circuits that make the node working even with a small amount of available energy from harvesting. Among various key building blocks of SoCs, this thesis presents the design of voltage/current reference circuits to provide a precise and stable DC bias under a wide range of environmental conditions, a level shifter to interface blocks between different voltage domains, and comparators to interface the analog world with the digital one.

More specifically, a low-area voltage reference circuit able to operate at supply voltage as low as 250 mV and 5.4 pW of power consumption at room temperature is first presented. The proposed circuit exploits a body biasing scheme to deal with the effect of voltage/temperature fluctuations and hence to ensure good accuracy of the generated output voltage, as demonstrated through measurements on a test chip fabricated in 180-nm CMOS technology. The design of a current reference circuit based on a voltage generator exploiting the structure used for the voltage reference is also presented and validated by means of silicon measurements on a 180nm prototype. The proposed circuit properly works down to 0.6 V to generate a current in the nA range with only 4,000- $\mu$ m<sup>2</sup> area occupancy, while reaching high power efficiency as guaranteed by the pW-power consumption of the voltage generator sub-block. Then, the design of a global variation-aware voltage reference based on an on-chip process sensor is proposed with the aim of achieving low sensitivity to process variations and overall good accuracy against process-voltage-temperature (PVT) variations, while also ensuring ULP/ULV operation, i.e., minimum supply voltage of 200 mV and power consumption of only 3.2 pW at room temperature. Experimental results in 180-nm CMOS technology across corner wafers demonstrate the effectiveness of the proposed solution. In addition, the design of a robust level shifter able to convert input voltages from the subthreshold regime (around 100 mV) up to the nominal supply voltage (1.8 V) is presented. The proposed circuit is based on a self-biased low-voltage cascode current mirror topology that features diode-connected PMOS and NMOS transistors to drive the split-input inverting buffer used as output stage with high energy efficiency. Obtained measurement results in 180-nm CMOS technology and across corner wafers demonstrate good robustness and performance of the proposed level shifter as compared to prior art. Finally, the design of an ULP/ULV comparator is proposed by using the dynamic leakage suppression (DLS) logic family. In particular, two different topologies, i.e., a single-stage structure and a dual-stage architecture based on the combination of two single-stage comparator are presented and validated through silicon measurements on 180-nm test chips, which demonstrate a power consumption of few tens of pW.

My research activity during PhD concerned the design of innovative ULP/ULV circuits and their validation through silicon measurements. First, a low-area voltage reference circuit able to operate at supply voltage as low as 250 mV and 5.4 pW of power consumption at room temperature was designed and fabricated in 180-nm CMOS technology. The proposed circuit exploits a body biasing scheme to deal with the effect of voltage/temperature fluctuations and hence to ensure good accuracy of the generated output voltage. A current reference circuit based on a voltage generator exploiting the structure used for the voltage reference was also designed and validated by means of silicon measurements on a 180-nm prototype. The proposed current reference properly works down to 0.6 V to generate a current in the nA range with only 4,000- $\mu$ m<sup>2</sup> area occupancy, while reaching high power efficiency as guaranteed by the pW-power consumption of the voltage generator sub-block. Then, the design of a global variation-aware voltage reference based on an on-chip process sensor was realized with the aim of achieving competitive sensitivity to process variations and and overall accuracy against process-voltagetemperature (PVT) variations, while also ensuring ULP/ULV operation (minimum supply voltage of 200 mV and power consumption of only 3.2pW at room temperature). Experimental results in 180-nm CMOS technology across corner wafers demonstrate the effectiveness of the proposed solution. The research activity was also addressed to interfacing blocks between different voltage domains in multiple-voltage systems. In this regard, a robust level shifter able

to convert input voltages from the subthreshold regime (around 100 mV) up to the nominal supply voltage (1.8 V) was designed. The proposed circuit is based on a self-biased low-voltage cascode current mirror topology that features diode-connected PMOS and NMOS transistors to drive the split-input inverting buffer used as output stage with high energy efficiency. Obtained measurement results in 180-nm CMOS technology and across corner wafers demonstrate good robustness and performance of the proposed level shifter as compared to prior art. Finally, to interface the analog world with the digital one, an ULP/ULV comparator was designed by using the dynamic leakage suppression (DLS) logic family. Two different topologies, i.e., a single-stage structure and a dual-stage architecture based on the combination of two single-stage comparator were fabricated and validated through silicon measurements on 180-nm test chips, which demonstrated a power consumption of few tens of pW.

## Introduction

The design of ultra-low power/voltage (ULP/ULV) circuits for energy-autonomous Systemson-Chip (SoCs) is gaining great interest in view of ever increasing demand of Internet of Things (IoT) sensor nodes with low area/power/voltage budget.

The main motivation in realizing ULP circuits and systems is the increasing battery lifetime of SoC. Indeed, battery technology has evolved much slower than CMOS technology. A considerable research effort has therefore been recently dedicated to reduce the power consumption of sensor nodes, which today has to be below the microwatt for the above applications. Voltage scaling is an attractive and very effective lever to reduce power consumption. ULP design thus often translates into ULV design. For this reason, energy-autonomous sensor nodes typically operate at supply voltages that are below the MOSFET threshold voltage ( $V_{TH}$ ) [1]. The latter represents a key challenge for circuit designers since it introduces several limitations in different aspects. Among these, the reduced supply voltage limits the use of conventional design techniques, thus leading the way to introduce new circuit topologies [2]. For example, bandgap voltage references typically require high supply voltage, thus giving rise to the need of introducing new voltage reference structures to be used in energy-autonomous SoC.

An aggressive power consumption scaling makes it possible to have SoCs that do not require any battery. Indeed, batteries in IoT devices is a major issue due to their large area occupation and expensive cost. They can be up to three times more expensive than the single chip they supply [3]. Their size is determined by the lifetime of the sensor node, which directly affects how often they need to be replaced. This has a significant impact on maintenance cost. To extend the overall lifetime, the battery is usually recharged slowly by harvesting some limited power from the environment, such as using a solar cell or radio frequency harvesting. Hence, battery miniaturization often results in highly-discontinuous operation of IoT devices, as they stop operating every time the battery runs out of energy.

Fig.1: This statistics represents the number of Internet of Things (IoT) connected devices in the world between 2015 and 2025. In 2025, the source predicted that 75.44 billion connected objects would be in circulation worldwide [4].

The statistics on the worldwide connected IoT devices (Fig.1) shows that the number of IoT devices will keep growing in the next years. The use of batteries will increase correspondingly by following a similar trend, which in turn will introduce environmental issue of battery disposal.

However, operation without any energy storage system may not be a feasible solution for selfpowering systems due to the unstable or intermittent harvesting sources. On the other hand, modern IoT devices are frequently switched between stand-by and active modes, where the stand-by mode time is typically longer compared to the active mode. Such duty-cycled operation mode gives rise to the need of energy storage to accumulate the energy surplus during the stand-by mode. The stored energy can be then used during the active mode or for the RF block (considering it requires a large amount of energy) to transmit information outside the IoT node.

Electrochemical super-capacitors as one of the energy storage solutions offers several advantages over rechargeable batteries in such applications. This because they exhibit much longer cycle life, which is equivalent to longer service time, and much higher power density for

higher efficiency of the whole power system. In the last few years, researchers have developed new materials and techniques to fabricate on-chip micro super-capacitors for micro-scale energy storages [5].

Recent technology advancements make it also possible to realize on-chip photovoltaic cells on the top level of the MOSFET structure while achieving a considerable power (1.22 mW/cm2) [6]. Similarly, antennas for RF harvesting can be also integrated on-chip with a capability of harvesting 0.5 uW of power at a distance of 7 cm away from a relatively low source power of +20-dBm (less than 1-W) at 4-GHz [7].

The availability of super-micro capacitors and on-chip energy harvesting thus enables the development of battery-less IoT sensor nodes, which in turn requires the design of ULP/ULV circuits to ensure the node is able to work even with a small amount of energy available from harvesting.

In the above context, this thesis mainly concerns the design of innovative ULP/ULV circuits for energy-autonomous SoCs and their validation through silicon measurements. A low-area voltage reference circuit able to operate at supply voltage as low as 250 mV and 5.4 pW of power consumption at room temperature is first proposed and validated in 180-nm CMOS technology. The proposed circuit exploits a body biasing scheme to deal with the effect of voltage/temperature fluctuations and hence to ensure good accuracy of the generated output voltage. A current reference circuit based on a voltage generator exploiting the structure used for the voltage reference is also presented and validated by means of silicon measurements on a 180-nm prototype. The proposed current reference properly works down to 0.6 V to generate a current in the nA range with only 4,000- $\mu$ m<sup>2</sup> area occupancy, while reaching high power efficiency as guaranteed by the pW-power consumption of the voltage generator sub-block. Then, the design of a global variation-aware voltage reference based on an on-chip process sensor is proposed to reach competitive sensitivity to process variations and overall accuracy against process-voltage-temperature (PVT) variations, while also ensuring ULP/ULV operation (minimum supply voltage of only 200 mV and power consumption of only 3.2 pW at room temperature). The proposed circuit is validated through measurements on a 180-nm test chip across corner wafers. My research activity during PhD was also addressed to interface blocks between different voltage domains in multiple-voltage systems. In this regard, a robust level shifter able to convert input voltages from the subthreshold regime (around 100 mV) up to the nominal supply voltage (1.8 V) is proposed. This circuit is based on a self-biased low-voltage cascode current mirror topology that includes diode-connected PMOS and NMOS transistors to drive the split-input inverting buffer used as output stage with high energy efficiency. Obtained measurement results in 180-nm CMOS technology and across corner wafers demonstrate good robustness and performance of the proposed level shifter as compared to prior art. Finally, to interface the analog world with the digital one, an ULP/ULV comparator is designed by using the dynamic leakage suppression (DLS) logic family. In particular, two different topologies, i.e., a single-stage structure and a dual-stage architecture based on the combination of two single-stage comparator are proposed and validated through silicon measurements on 180-nm test chips, which demonstrate a power consumption of few tens of pW.

A summary of the content of each chapter of this thesis is presented below:

Chapter 1 provides an overview of SoCs and energy harvesting sources that can power those SoCs. The technology used to realize micro-super capacitor for on-chip energy storage systems is also explored. In addition, the design of ULP/ULV circuits is introduced with a focus on the MOSFET operation in the subthreshold regime and the impact of process variability in subthreshold circuits.

Chapter 2 presents the design of CMOS voltage and current reference circuits for highly uncertain harvesting systems. More specifically, the design of a ULP/ULV voltage reference which exploit body biasing feedback to improve its figures of merit is presented, along with a detailed circuit analysis. Measurement results on a 180-nm test chip are provided to demonstrate the effectiveness of the proposed approach. Then, a CMOS current reference circuit exploiting the structure used for the voltage reference is also presented and validated by means of silicon measurements on a 180-nm prototype.

Chapter 3 introduces the design of a global variation-aware voltage reference with ULP/ULV operation. The architecture is based on design replicas optimized at different process corners and an on-chip process sensor, which allows selecting the best combination of replicas. Experimental results in 180-nm CMOS technology across corner wafers are provided to demonstrate the effectiveness of the proposed solution.

Chapter 4 presents the design of a robust level shifter able to convert input voltages from the subthreshold regime (100 mV) up to the nominal supply voltage (1.8 V). The proposed circuit is based on a self-biased low-voltage cascode current mirror (CM) topology that features diode-connected PMOS and NMOS transistors to drive the split-input inverting buffer used as output

stage with high energy efficiency. Obtained measurement results in 180-nm CMOS technology and across corner wafers demonstrate the effectiveness of the proposed level shifter as compared to prior art.

Chapter 5 presents the design of ULP dynamic voltage comparators (DVCs) exploiting Dynamic Leakage Suppression (DLS) logic. Two different DVC topologies, i.e., a single-stage structure and a dual-stage architecture based on the combination of two single-stage DVCs are presented and validated through silicon measurements on 180-nm test chips.

## Chapter 1: Energy Harvesting for System-on-Chip and Design of Ultra-low Power/Voltage Circuits

This chapter firstly gives an overview of energy-harvested Systems-on-Chip (SoCs) and some of their recent applications. Particular attention is paid to the power levels that can be generated on a chip level. Available harvesting sources are presented, while comparing their power density data. This overview on energy harvesting sources provides assistance in choosing the type of harvester when designing a ULP/ULV SoC. Along with the selection of the energy harvesting source, a storage system that can be integrated and able to supply the energy for the circuits on the SoC has to be defined. Accordingly, technologies for realizing micro super-capacitors are also presented. Then, the chapter introduces the design of ULP/ULV circuits with a focus on the MOSFET operation in the subthreshold regime and the impact of process variability in subthreshold circuits.

#### **1.1 Energy-Harvested System-on-Chip**

A System-on-chip (SoC) architecture is a microchip that can integrate sensors, power supply block with MPPT, analog blocks for the signal conditioning, ADCs, microprocessor, memories, and RF block to communicate (Fig.1.1). The main difference between system-on-chip and other computing systems is that an SoC requires parts that have to be designed for the specific function and environment where it is placed.

Fig.1.1: A System-on-Chip integrates on die all the blocks needed to solve its tasks.

This device typically exploits energy harvesting systems for the power supply and is usually paired with a rechargeable battery (i.e., Li-ion, NiCd, NiMH and others) which stores the

exceeded power from the harvesting. Recent works show how it is possible to integrate a great number of sensors and computing blocks on a single chip supplied by integrated energy harvesting systems. This is possible by implementing ULP/ULV analog and mixed-signal circuits.

An example of SoC power supply block used for a biomedical implant is reported in [6]. A charge pump that receives the harvested solar energy from parallel-connected photodiodes is implemented to achieve an output power of 1.65  $\mu$ W in a 1.54-mm<sup>2</sup> active area with 1.22 mW/cm<sup>2</sup> light input. The device under test is placed under pork skin to simulate the biomedical implant. Lower light condition brings the power supply block to generate a lower power.

In order to solve the problem of the discontinuous energy source from the energy harvesting, a recent work [8] shows a dual-mode architecture comprising of a microcontroller and a power management module, which can operate both in normal (NM) and leakage suppression mode (LSM). These two operating modes of NM and LSM, respectively, allow the use of microcontroller (MCU) with a fast clock frequency and low energy per operation when the system is powered by the battery and with a low frequency and low power configuration when the energy comes from purely harvesting. The MCU can work with poor light condition: in detail, the system is fully running at 55-lux light intensity with a 0.54 mm<sup>2</sup> on-chip solar cell.

An even more interesting harvesting source comes from biological sources. In particular, recent works that adopt microbial fuel cells demonstrate harvesting energy from bacteria is a feasible solution. In this regard, a paper-based microbial fuel cells realized in [9] shows the possibility to harvest bio-power from bacteria-containing liquid derived from renewable and sustainable wastewater. Intrinsic feature of the paper allows for rapid adsorption of bacteria-containing solution through capillary, thus leading to a very short start-up time. SoC addressed to analyse water quality or underground sensors system for agriculture [10] could benefit from the use of biologic harvesting source. Basically, this kind of harvesting is interestingly useful in all environment where there is humidity or water and no light or RF sources.

Concerning the sensing blocks, several solutions were proposed to integrate on-chip temperature sensors. An ultra-low power CMOS temperature sensor in 0.13- $\mu$ m standard CMOS process with an area of 0.0014 mm<sup>2</sup> and a power consumption of 0.15  $\mu$ W is presented in [11]. In addition, a pW relaxation oscillator is proposed in [12]. Implementing pW oscillators makes it possible to save energy for the clock generation and to design temperature sensors

with power consumption in the order of pW (by using ULP logic design for the control block). Using Micro Electro-Mechanical Systems (MEMS) allows realizing gyroscope sensors, force sensors for accelerometer or air pressure measurement, humidity and temperature sensors [13] and others. Fabrication of MEMS has recently evolved from the process technology in semiconductor device fabrication [14], thus making a complete on-chip integration of this kind of sensors feasible. A wide variety of sensors can be integrated in SoC for biomedical applications. A 2-channel ECG monitoring, a Bio-Z readout channel for respiration analysis and a thermistor-based temperature sensor for body temperature monitoring are implemented in [15]. The Bio-Z is the Bioelectrical impedance, i.e., a commonly used method for estimating body composition, more specifically body fat and muscle mass.

Overall, the research effort in designing ULP/ULV circuits, along with the research on exploiting alternative energy source and storage systems in micrometer scale will allow realizing energy-autonomous SoCs that can solve multiple tasks, being ideally perpetual and working until something physically breaks inside.

#### 1.1.1 Energy harvesting sources

The goal of energy harvesting is to convert energy from one form to another that can be used to power supply electronic devices or SoC. When implemented in environmental monitoring nodes, energy-harvested solutions can directly extract energy from the environment and use it to feed such nodes. Our surroundings offer plenty of opportunities to take advantage of (Fig.1.2), from which a small amount of energy can be scavenged and used for the power supply of specific sensor nodes. The difference between energy harvesting and energy scavenging is related to the energy source dependency. When a waste energy is used (e.g., indoor light of heat from air conditioning unit), it is possible to define the harvesting of energy as energy scavenging [16].

Fig.1.2: Energy harvesting sources and conversion methods.

Energy harvesting sources can be categorized to ambient or external ones. The ambient sources are accessible within an environment without any external energy supply. The external sources emit energy in the environment, with the intent for this energy to be harvested by the sensor nodes [17].

The most commonly used source for energy harvesting is the Sun, i.e. an affordable energy source that presents high power density in outdoor environments. A photovoltaic cell (PVC) generates a DC voltage that can be directly used by the circuits. Working with low-light condition is also possible by using DC-DC converter, enabling the increase of supply voltage needed for the operation of SoC. It is well known that the solar cell is not a constant voltage and current source. The output power of the cell depends on the sunlight intensity and the ambient temperature. DC-DC converter with MPPT is used to deal with this. Correct position of the PVC in the environment is also important to achieve its maximum possible efficiency. Therefore, solar harvesting is a discontinuous energy source where the discontinuity is predictable (night and day cycle). Solar harvesting solutions, e.g. PVC, can be easily placed on a chip, as demonstrated in [18].

Thermal energy can be converted to electricity by thermoelectric transducers depending on spatial variations in temperature or pyroelectric transducers depending on temporal variations in temperature. Thermoelectric generators are based on the Seebeck effect [19] and implemented with series-connected p-type and n-type semiconductor blocks. The open circuit

voltage and the maximum power point of thermoelectric transducers depend on the temperature difference between the cold side and the hot side of the transducer. Pyroelectric converters use pyroelectric material, i.e., a class of non-centrosymmetric polar crystals that exhibit an inherent coupling between electrical polarization and temperature, such that a change in temperature results in a change in the electric dipole moment known as pyroelectric [20]. The open circuit voltage and generated power mainly depend on the rate of the temperature change.

Wind-based energy harvesting systems convert kinetic energy into electricity using turbines, rotors, and in general the principles of electromagnetic induction. For instance, using piezoelectric material allows exploiting micro piezoelectric strips moved by the wind to generate energy [21]. The wind-based harvesting solutions are classified in electromagnetic and piezoelectric types. In particular, piezoelectric-based solutions allows compact system, easy operation with low wind speed conditions, higher efficiency, instant start-up with no dead time, smaller size, and lightweight. However, they can be easily damaged when high pressure is applied to the piezoelectric wind energy harvester because of the brittleness of the piezoelectric device [22]. Research on the effect of global warming shows an increase in the average global wind speed in the last ten year. Decadal-scale variations of near-surface wind are probably determined by internal decadal ocean-atmosphere oscillations, rather than by vegetation growth and/or urbanization as hypothesized previously. Such strengthening has increased potential wind energy by  $17 \pm 2\%$  from 2010 to 2017 [23]. The main issue of wind-based harvesting comes from their size and the discontinuity of the source. The average wind speed increasing combined with research on miniaturized wind-based harvester can allow the use of piezoelectric-based wind energy harvesting in SoC.

Piezoelectric material is also used for vibration energy harvester, where a vibration or movement is transduced in a strength applied to the piezoelectric material that will finally transform it into electric energy. Vibration or movement harvesting systems can also exploit MEMS. For instance, a MEMS-based vibration harvester can consist of an electroplated copper planar spring, a permanent magnet and a copper planar coil [24], while generating a maximal output power of 700 nW with an input vibration frequency of 94.5 Hz and input acceleration of 4.94 m/s.

Radio frequency (RF) energy harvesting is an energy conversion method used for converting energy from the electromagnetic (EM) field in a voltage source that can supply a current that

depends on the EM field intensity. Modern house has Wi-Fi router, mobile phones, Bluetooth devices and other devices that transmit RF EM waves. Outside the house, we can find mobile phone repeaters that can supply our electronic devices by using RF harvesting. RF-based energy harvesting/scavenging can be used to supply the power required for wearable electronics devices, RFID, medical implantable devices, wireless sensor network and internet of things (IoT) nodes [25]. RF energy harvesting is a continuous source in an environment that is surrounded by transmitting devices. Furthermore, RF-based harvesting systems are simple and can be easily placed on a chip, as solar harvesting solutions. They typically consist of an antenna, a matching circuit, and a rectifier. The antenna can be made using the metal layer inside the chip and usually placed at the border of the chip. The matching circuit is made with capacitors and inductors. The former can be implemented by using the MOSFET capacitance, while the latter are available in the library of different IC producers or can be realized with spirals implemented with metal layer. Rectifier can be implemented using N-P Diode or MOSFETs [26].

Finally, Table 1.1 [27] compares the different energy harvesting sources in terms of the provided power density. Solar energy shows the highest power density in outdoor applications, while the power decreases for indoor application where light has less intensity. Vibration and wind energy become comparable to solar energy for indoor applications. Thermal energy sources are a good candidate for human activities harvesting and can be combined with vibration harvesting. RF harvesting shows the smallest amount of power density and it is strongly dependent by the distance of the RF sources.

| Harvesting source |                              | Power density              |

|-------------------|------------------------------|----------------------------|

| Solon onongy      | Outdoors                     | 15-0.15 mW/cm <sup>2</sup> |

| Solar energy      | Indoors                      | 10-100 µW/cm <sup>2</sup>  |

|                   | Piezoelectric (in the shoes) | 330 µW                     |

| Vibration         | Electrostatic conversion     | 21 nW/mm <sup>3</sup>      |

|                   | Electromagnetic conversion   | 184 µW/mm³                 |

|                   | Thermoelectric (5°C          | 40 µW/cm <sup>2</sup>      |

| Thermic           | gradient)                    | 40 µ w/cm                  |

| Thermic           | Pyroelectric (Temperature    | 8.6 μW/cm <sup>2</sup>     |

|                   | rate 8.5°C/s)                | 8.0 µ w/cm                 |

| RF                | GSM 900/1800 MHz             | 100 nW/cm <sup>2</sup>     |

| Л                 | Wi-Fi 2.4 GHz                | 10 nW/cm <sup>2</sup>      |

| Wind              | Wind speed 5m/s              | 380 µW/mm <sup>3</sup>     |

| Acoustic (similar to |          |                       |

|----------------------|----------|-----------------------|

| vibration            | At 75 dB | 30 nW/mm <sup>3</sup> |

| harvesting)          |          |                       |

Table 1.1: Comparison of the available output powers from different energy harvesting sources.

#### **1.1.2 Super-micro capacitors**

The term "micro-supercapacitors" (MSC) normally refers to miniaturized super-capacitors that range from microns to centimetres and can be integrated on-chip with circuits and microelectronic components. MSCs with stable performance can be integrated as the energy storage and power supply units. In general, micro-batteries are the primary choice for self-powered systems since they provide an energy density that can ensure stable supply current. However, the charge/discharge mechanism of batteries typically result in limited lifetime and power density. On the other hand, MSCs ensure longer operating lifetime (>100,000 cycles), faster charge/discharge rates as well as higher power density [28]. The reduced number of charge/discharge cycles also translates into a smaller capacitance degradation.

Fig.1.3: The common structure of MSCs: (a) standard sandwich MSCs, (b) wire-shaped fibrous MSCs, and (c) interdigital MSCs. Figure from [29].

At present, there are three typologies of MSC: standard sandwich-structure MSCs, interdigitalstructure MSCs and fibrous MSCs [29], as shown in Fig.1.3. Conventional sandwich MSC is a vertical structure composed of two electrodes and electrolyte sandwiched in the middle. MSCs with in-plane interdigital electrodes are separated by insulated gap. In particular, the performance of an interdigital-structure MSC mainly depends on the electrode width, thickness and gap size [30]. Fibrous MSC is pseudo-capacitor relying on the fast surface faradaic redox reactions, where a fibre material is used as support. This type of MSCs allow flexible design for wearable devices. A large number of studies have shown that reasonable design of the materials (in particular, the electrode material) is fundamental to improve the electrochemical performance of MSCs.

Overall, MSCs suffer of self-discharge that can consist of a relatively fast diffusion process and a slower leakage current. The open-circuit voltage decay due to charge losses can be caused by side reactions, which may be due to over-potential decomposition of the electrolyte, redox-reactions caused by impurities, or possible functional groups on the carbon surface. Another cause for observed self-discharge is the flaws during the production, which may result in micro-short circuits between the anode and the cathode [31].

Research on new materials for the electrode and electrolyte can mitigate the problem of the self-discharge, while increasing the capacitance of MSCs. Table 1.2 compares different materials and technologies used for MSCs, also in terms of the energy density that can be achieved. MSCs can have 3-dimension or 2-dimension. The first type is presented in [32], [33] and [36] and it is not possible to be used in SoC considering they cannot be integrated on-chip, even if it shows a great capacitance density. [35] shows the highest capacitance among on-chip MSCs as compared to [34] and [37].

| References | Electrode material                                  | Electrolyte<br>material                                  | Flexi<br>bility | On-<br>chip | Capacitance<br>density | Energy<br>density          |

|------------|-----------------------------------------------------|----------------------------------------------------------|-----------------|-------------|------------------------|----------------------------|

| [32] 2020  | Carbon/Vanadium<br>disulphide<br>nanosheets (C/VS2) | H <sub>2</sub> SO <sub>4</sub> Gel                       | No              | No          | 86.5 F/cm <sup>3</sup> | 15.6<br>mWh/cm³            |

| [33] 2017  | Micropatterned<br>multi-walled<br>carbon nanotube   | Polyvinyl alcohol-<br>H <sub>3</sub> PO <sub>4</sub> gel | Yes             | No          | 2.02 F/cm <sup>3</sup> | N/A                        |

| [34] 2017  | Aluminium and<br>Silicon nanowires                  | 1-Ethyl-3-<br>Methylimidazolium<br>Bismide               | No              | Yes         | 13 µF/cm <sup>2</sup>  | 108<br>μWh/cm <sup>2</sup> |

| [35] 2018  | RuO <sub>2</sub>                                    | H <sub>2</sub> SO <sub>4</sub> gel                       | Yes             | Yes         | 6.5 mF/cm <sup>2</sup> | N/A                        |

| [36] 2020 | Ti <sub>3</sub> C <sub>2</sub> T <sub>x</sub> MXenes<br>with sodium<br>ascorbate | H <sub>2</sub> SO <sub>4</sub> /PVA gel | Yes | No  | 322 F/cm <sup>3</sup>  | 100<br>mWh/cm <sup>3</sup> |

|-----------|----------------------------------------------------------------------------------|-----------------------------------------|-----|-----|------------------------|----------------------------|

| [37] 2019 | MnO <sub>2</sub> and Silicon nanotube                                            | 1 M Na2SO4                              | Yes | Yes | 2.1 mF/cm <sup>2</sup> | N/A                        |

Table 1.2: Comparison of recent Micro Super-Capacitors technologies.

### 1.2 Design of Ultra-low Power/Voltage Circuits

The fast-increasing demand for IoT sensor nodes with aggressive form factor, cost and lifetime targets requires relentless power/voltage reductions to fit the capabilities of smaller and low-cost energy harvesting sources [38]-[39]. Such miniaturized sensor nodes with millimeter-scale energy harvesters tightly constrain the system power [40]-[43], due to the fluctuating and uncertain nature of the harvested power and frequent unavailability of miniaturized batteries [12], [44]-[50]. Indeed, whenever the harvested power (voltage) drops below the minimum system power  $P_{min}$  (and minimum voltage  $V_{min}$ ), the operation is inevitably interrupted. Therefore, reducing both  $P_{min}$  and  $V_{min}$  is fundamental to prevent forced system shutdowns or interruptions, whenever unfavorable environmental conditions challenge the regulation limits of the intermediate power conversion [44], as depicted in Fig. 1.4.

Fig. 1.4: Low minimum voltage  $(V_{min})$  and minimum power  $(P_{min})$  are desirable in energyharvested SoCs to prolong operation under unfavorable conditions.

The same considerations apply to directly-harvested systems, where the intermediate power conversion between the harvester and the system is eliminated altogether to further reduce the system power floor  $P_{min}$  [12], [40]. More quantitatively, the harvested power density in most energy sources is in the nW/mm<sup>2</sup> range (see Table 1.1) and hence constrain  $P_{min}$  in the scale of nWs. Concerning the harvested voltage, its range strictly depends on the operating principle and the environmental conditions [49]. For instance, solar harvesting typically generates voltages below 0.5 V, and down to less than 0.3 V at dim light conditions [42].

Taking all this into account, the design of ULP (i.e., power consumption in the order of few nW or below) and ULV (i.e., minimum operating voltage below 0.5 V) circuits to be integrated in energy-harvested SoCs becomes crucial.

#### **1.2.1 MOSFET operation in subthreshold region**

In general, the total power dissipation of a CMOS circuit is given by the sum of static and dynamic power, as expressed by

$$P_{tot} = V_{DD} I_{stat} + \alpha C V_{DD}^2 f$$

(1.1)

where  $V_{DD}$  is the supply voltage,  $I_{stat}$  is the static supply current,  $\alpha$  is the switching activity rate, C is the load capacitance, and f is the clock frequency. According to (1.1), low-power operation can be achieved by reducing the load capacitance or the frequency, as well as drastic reduction in power consumption can be achieved by reducing the  $V_{DD}$ . Aggressive voltage scaling typically leads the transistors to work in subthreshold region with a significant reduction of their static current and hence the standby power consumption.

The operation of MOSFETs in the subthreshold region is typically exploited when designing ULP/ULV circuits. A CMOS circuit is said to operate in subthreshold if all the transistors work with a gate-source voltage ( $V_{GS}$ ) lower than their threshold voltage ( $V_{TH}$ ), as shown in Fig.1.5.

Fig.1.5: MOSFET current-voltage characteristics highlighting the subthreshold and superthreshold operating regions. In the superthreshold region, the current is fairly linear, whereas in the subthreshold regime it is exponentially dependent on  $V_{GS}$ .

The basic four-terminal nMOSFET channel structure is depicted in Fig. 1.6. The substrate (connected to the Body terminal) is composed of p-type silicon, where two n<sup>+</sup>-type wells are formed and connected to the drain and source terminals. Then, the gate consists of heavily doped or silicide polysilicon, and is separated from the substrate by a thin silicon dioxide film, i.e., the gate oxide. The main device parameters are the gate oxide thickness ( $T_{ox}$ ) and its dielectric constant ( $\mathcal{E}_r$ ), the channel length (L), the substrate doping concentration ( $N_{sub}$ ), and the channel width (W).

Fig. 1.6: Structure of an n-channel MOSFET with different current contributions.

When the MOSFET works in subthreshold region ( $V_{GS} < V_{TH}$ ), the drain current is given by:

$$I_{sub} = \frac{W}{L} I_0 \exp\left(\frac{V_{GS} - V_{TH}}{nkT/q}\right) \left(1 - \exp\left(\frac{-V_{DS}}{kT/q}\right)\right)$$

(1.2)

where  $I_0$  is the intrinsic sub-threshold current at zero gate-source voltage, *n* is the subthreshold slope, *k* is the Boltzmann constant, *T* is the absolute temperature, *q* is the electron charge with  $V_T = kT/q$  being the thermal voltage, and  $V_{DS}$  is the drain-source voltage.

By including the body effect (i.e., body-source voltage  $V_{BS} \neq 0$ ), Equation 1.2 becomes as below:

$$I_{sub} = \frac{W}{L} I_0 \exp\left(\frac{V_{GS} - V_{TH0} + \lambda_{BB} V_{BS}}{nkT/q}\right) \left(1 - \exp\left(\frac{-V_{DS}}{kT/q}\right)\right)$$

(1.3)

where  $V_{TH0}$  is the zero-bias threshold voltage and  $\lambda_{BB}$  is the threshold voltage body coefficient, considering that the threshold voltage  $V_{TH}$  is expressed by  $V_{TH0} - \lambda_{BB}V_{BS}$ .

Finally, considering  $V_{DS} > 4V_T$  (with  $V_T \cong 26 \, mV$  at room temperature), the term  $\exp\left(\frac{-V_{DS}}{V_T}\right)$  approaches zero, thus leading to the following simplified expression:

$$I_{sub} = \frac{W}{L} I_0 \exp\left(\frac{V_{GS} - V_{TH0} + \lambda_{BB} V_{BS}}{nkT/q}\right)$$

(1.4)

Analysing the different current contributions in the MOSFET (highlighted in Fig. 1.6) is fundamental to achieve a better insight for the circuit designer, especially in designing subthreshold circuits.

The current I1 consists of the subthreshold current between source and drain depending on the applied gate voltage which create a weak inversion layer in the channel. An additional effect for this current is given by the Drain-Induced Barrier Lowering (DIBL), which occurs when a high drain voltage is applied to a short-channel device.

The current I2 is the channel punch-through. When the channel is short and the drain voltage is high, the depletion regions of drain and source approach each other. As a result, the gate voltage loses control over the channel.

The current I3 represents the Gate-Induced Drain Leakage (GIDL). This is the result of a high electric field on the gate-drain overlap region. As a consequence, the depletion width of the drain to substrate n-p junction is reduced [50]. Carriers are generated in the substrate and drain from the direct band-to-band tunnelling. This phenomenon is more prominent in technology with thin oxide that works with high gate voltage.

The current I4 is the reverse n-p junction leakage and could affect also the source-body n-p junction if the source voltage is higher than the body voltage. It has two components: the minority carrier diffusion/drift near the edge of the depletion region and the electron-hole pair generation in the depletion region of the reverse-biased junction. If both n- and p-regions are heavily doped, Band-To-Band Tunnelling (BTBT) can also be present.

The current I5 refers to oxide leakage tunnelling with two contributions. The first one is due to the high electric field which results in the tunnelling of electrons from the inverted substrate-to-gate and also from the gate-to-substrate through the oxide. The second contribution is the gate current due to hot carrier injection. If a region with a high electric field is located near the oxide-channel interface, some of the electrons or holes can gain sufficient energy from the field to cross the interface potential barrier and enter the oxide layer.

#### 1.2.2 Impact of process variability on subthreshold circuits

Due to the relentless miniaturization of MOSFET devices, process variability has become a critical issue in the design of VLSI circuits. Within a chip, the main source of variability comes from the MOSFETs, but also interconnections, resistors, capacitors and diodes contribute to performance variability. Increasing process variations provides a primary opposition to voltage scaling and limits the achievable power reduction.

CMOS technology includes two major types of process variability: local (intra-die) and global (inter-die). Local variability is related to the differences of identical MOSFETs across a short distance. Global variability refers to changes for identical MOSFETs separated by a longer distance (i.e., on a different die) or fabricated at a different time [51].

A different classification is given by [52], where process variability is categorized to withindie, die-to-die and wafer-to-wafer. Within-die and die-to-die classifications reflect some of the spatial characteristics of the variations. Those that vary rapidly over small distances (< die size) are called within-die, whereas variations that change gradually over the wafer will cause dieto-die variations. Wafer-to-wafer variations reflect both the spatial and temporal characteristics of the process and cause different wafers to have different properties.

From the designer's point of view, the process variability is typically divided into two categories.

The local variability or within-die is considered a mismatch, which leads similar MOSFETs within a circuit to exhibit different characteristics of each other. On the other hand, the global or process variability is typically described as a same threshold voltage change for all the MOSFETs within a circuit.

The local variation or mismatch ( $\sigma$ ) of MOSFET parameters such as channel dopant concentration, mobility, and gate oxide thickness is typically modelled considering an area dependency according to the Pelgrom's law [53], as given by

$$\sigma \propto \frac{1}{\sqrt{WL}} \tag{1.5}$$

Qualitatively, local variations decrease as the device size increases since the parameters mediate over a greater distance or area. According to (1.5), the solution to reduce the impact of mismatch is the increase of the MOSFETs' size, but at the cost of greater area occupation.

Conversely, the global variability is modelled by different worst-case process corners. Such corners are generated considering slow (S), i.e., less conductive, and fast (F), i.e., more conductive, nMOSFETs and pMOSFETs. On one hand, when a MOSFET is defined fast, this means that its threshold voltage is reduced by the variability. On the other hand, a slow MOSFET has higher threshold voltage with respect to the nominal one. As a result, we have four different corners with respect to the nominal one given by typical (T) nMOSFETs and pMOSFETs (i.e., TT corner): (*i*) SS corner given by slow nMOSFETs and pMOSFETs to model the worst-case condition for the speed, (*ii*) FF corner given by fast nMOSFETs and pMOSFETs to model the worst-case condition for the power consumption, (*iii*) the SF corner given by slow nMOSFETs and fast pMOSFETs to model the worst-case condition for the logic "zero" in digital circuits, and (*iv*) the FS corner given by fast nMOSFETs and slow pMOSFETs to model the worst-case condition for the logic "one" in digital circuits. Note that SF and FS corner are also considered in the design and analysis of analog circuits employing both MOSFET typologies.

Fig. 1.7: Measurement results for an nMOSFET (regular threshold voltage RVT device,  $L = 1 \mu m$ ,  $W = 2 \mu m$ , T = 21°C,  $V_{BS} = 0$  V and  $V_{DS} = 0.5$  V) from corner wafer chips.

As an example, Fig. 1.7 shows the experimental current-voltage characteristics of an RVT (regular threshold voltage) nMOSFET with  $L = 1 \mu m$  and  $W = 2 \mu m$  extracted from corner wafer chips implemented in a commercial 180-nm CMOS technology.

According to (1.2)-(1.4), in the subthreshold regime, the drain current depends exponentially on the  $V_{TH}$ . Therefore, a  $V_{TH}$  change owing to the process variations translates into a significant change in the MOSFET conductivity. This requires specific precautions and circuital solutions when designing subthreshold circuits for ULP/ULV applications. In general, the impact of process variations can be mitigated by using MOSFETs of the same type [54]. Another solution concerns the use of post-silicon trimming to adjust the circuit performance after fabrication. In addition, automatic trimming solutions can be also implemented by exploiting a process sensor (as discussed in Chapter 3) or implementing feedback/feedforward control in the circuit design (as discussed in Chapter 2).

# Chapter 2: Design of CMOS Voltage and Current References for Highly-Uncertain Harvesting

Voltage and current references are key building blocks in IoT sensor nodes, often expected to be always-on to ensure proper circuit biasing and robust system operation at all times, regardless of process, voltage and temperature (PVT) variations. To align with the requirements of millimetre-scale harvested systems, always-on reference circuits have to exhibit a power consumption below the nW range, to avoid eating up a significant fraction of the requested minimum power. Similarly, their minimum supply voltage has to be kept as low as possible. This chapter firstly presents the design of a compact NMOS-only voltage reference that is able to operate down to a 0.25-V supply voltage and 5.4-pW power consumption at room temperature. The presented voltage reference is based on a body biasing scheme assisted by replica well biasing to compensate voltage and temperature fluctuations. Detailed circuit analysis is provided, along with trimming-less measurement results on a 180-nm test chip to demonstrate the effectiveness of the proposed approach. Then, the design of a current reference circuit exploiting the structure used for the voltage reference is also presented and validated by means of silicon measurements on a 180-nm prototype.

## 2.1 CMOS Voltage Reference down to 0.25-V, 5.4-pW Operation

In prior art, voltage references are categorized into CMOS and bandgap (BGR) topologies [54]-[67]. Under subthreshold operation, CMOS voltage references [54]-[61] typically allow sub-1 V operation, lower power and smaller area. As a drawback, their accuracy is limited by the susceptibility of the transistor threshold voltage to PVT variations. Conversely, BGR references [62]-[66] exhibit better accuracy at the cost of higher minimum operating voltage, area occupation, process requirements (e.g., availability of BJT transistors), and power in the tens of nWs. Hybrid designs [67]-[68] were also proposed with the aim of covering the intermediate gap between CMOS and BGR solutions, but with  $V_{DD,min}$  (~1 V) higher than CMOS references.

Here, an NMOS-only voltage reference to enable both ultra-low  $V_{min}$  and  $P_{min}$  for adoption in resource-constrained sensor nodes, along with compact area and trimming suppression for low cost, while achieving a competitive absolute accuracy, is presented [C1]. The proposed circuit

employs body biasing for the compensation of environmental (i.e., temperature and voltage) fluctuations, as assisted by replica deep n-well biasing for the temperature-dependent leakage suppression of p-well/deep n-well parasitic diodes. Experimental results on 180-nm test chips demonstrate operation from 1.8 V down to 0.25 V, 5.4-pW power consumption, 2,200- $\mu$ m<sup>2</sup> area, while achieving a 2.8-mV absolute accuracy lower than prior art.

#### 2.1.1 Proposed architecture and operating principle

The proposed voltage reference is based on an 8-transistor circuit comprising a body bias generation block, a deep n-well replica bias, and a core reference generation block, as shown in Fig. 2.1. As generated by the latter block, the output reference voltage  $V_{REF}$  is set by the strength ratio of transistors M4 and the diode-connected stacked transistors M1-M3. Being  $V_{REF}$  positive and the gate of M4 connected to ground, transistor M4 is reverse gate-biased (i.e., it has negative gate-source voltage) and hence conducts a current that is well below the regular transistor leakage. This leads to sub-leakage power consumption, as targeted for highly-uncertain harvesting systems.

Fig. 2.1: Schematic of the proposed voltage reference.

Concerning the body bias generation block in Fig. 2.1, the p-well body enclosing transistors

M1-M3 is biased through a voltage  $V_B$  that is generated by the body bias generation transistors M5-M6. These two-transistor block mimics the structure of the core reference generation block, to track its die-to-die and environmental variations. Indeed, transistor M6 is reverse gate-biased, and hence draws a sub-leakage power. As main difference between the two blocks, M1-M3 are stacked to reduce the strength of their equivalent transistors M1-3 in Fig. 2.1 and hence pushing  $V_{REF}$  closer to the mid-supply point, compared to  $V_B$ . In other words, the number of stacked transistors can be used as a knob to control  $V_{REF}$  amplitude.